数字集成电路接口标准和逻辑电平

逻辑电路

- 数字电路由组合逻辑和寄存器组成。数字集成电路按照电路结构,可分成 TTL 电路和 CMOS 电路两大系列。常用的 74xx 和 4000 系列器件采用的就分别是 TTL 和 CMOS 电平逻辑。

- TTL 器件是流控器件,输入电阻小,速度快,驱动能力强,功耗大。

- CMOS 器件是压控器件,输入电阻大,速度慢,驱动能力弱,功耗小。

门电路

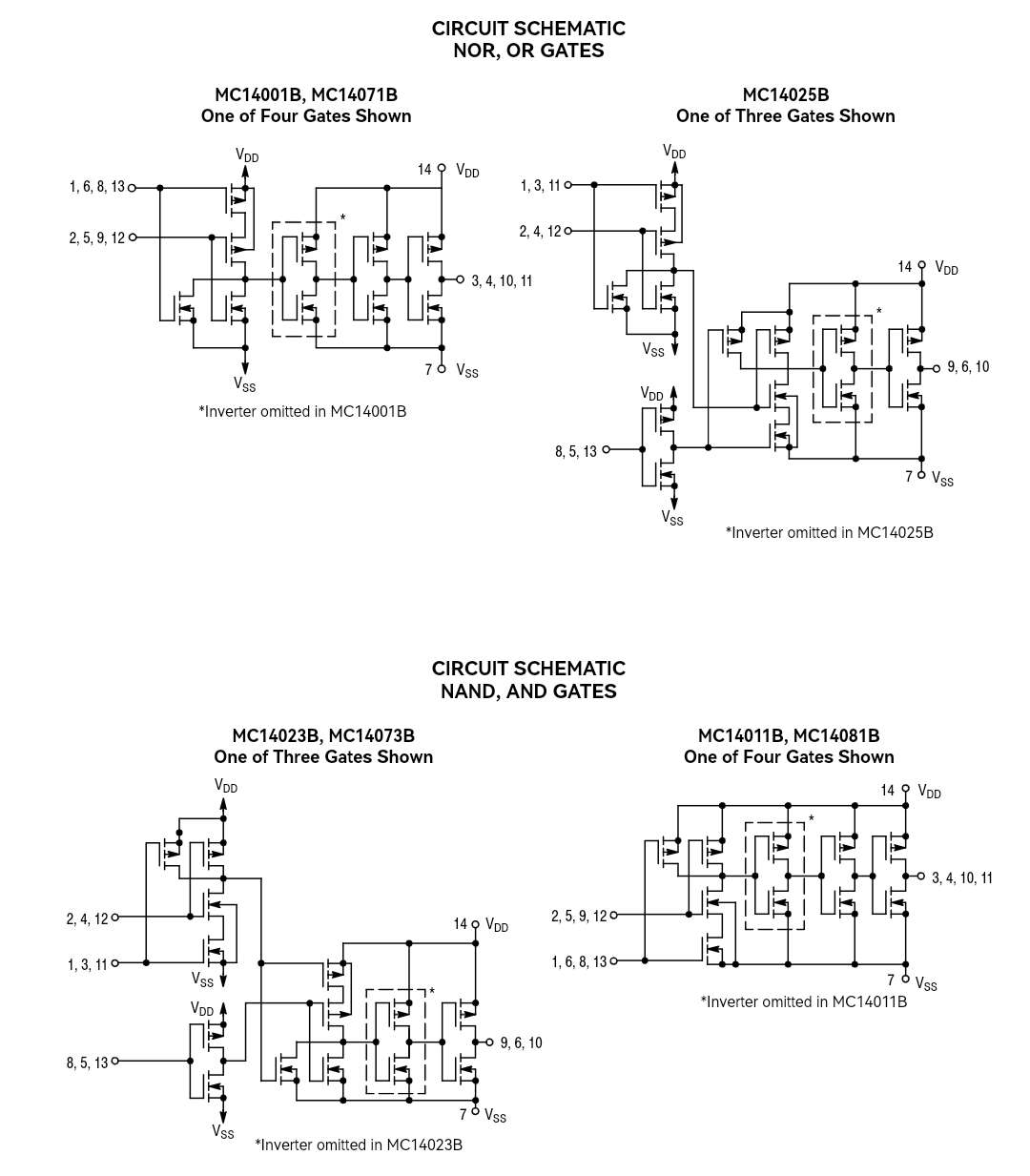

- 实际应用的门电路都是集成电路,门电路几乎可以组成数字电路里面任何一种复杂的功能电路。

- 常用的七种基本逻辑门为与门、或门、非门、与非门、或非门、异或门、同或门。另外还有一种常用的基本门电路为传输门。

- 门电路输出端的电路结构有三种:有源负载推拉式(或互补式)输出、集电极(或漏极)开路输出和三态输出。

逻辑电平

- 常用的逻辑电平接口标准主要有 TTL、CMOS、LVTTL、LVCMOS 和 SSTL。TTL 和 CMOS 常用的供电电压为 5V,LVTTL 和 LVCMOS 常用的供电电压有 3.3V、2.5V、1.8V。

- 单端信号接口标准主要有三类,分别是 LVTTL 和 LVCMOS(JESD8-5,JESD8-B)、SSTL(JESD8-8,JESD8-9B,JESD8-15)、HSTL(JESD8-6)。

数字集成电路接口标准

-

工作条件

供电范围 窄范围 正常范围 扩展范围 额定电压 3.3V 3.3V 3.3V 供电电压 3.15~3.45V 3.0~3.6V 2.7~3.6V -

直流电气特性

电平标准 VOH VOL VIH VIL 单位 TTL:5V (4.5~5.5V) ≥2.4 ≤0.5V ≥2 ≤0.8 V LVTTL:3.3V (3.0~3.6V) ≥2.4 ≤0.4V ≥2 ≤0.8 V LVTTL:2.5V(2.3~2.7) ≥2.0 ≤0.2V ≥1.7 ≤0.7 V CMOS:5V(4.5~5.5V) ≥4.45 ≤0.5 ≥3.5 ≤1.5 V LVCMOS:3.3V (3.0~3.6V) ≥3.2(VDD-0.2) ≤0.1(0.2) ≥2.0 ≤0.7 V LVCMOS:2.5V(2.3~2.7V) ≥2( 1.7~2.1) ≤0.1(0.2~0.7) ≥1.7 ≤0.7 V

参考文献

- 门电路_百度百科

- 数字电路基础知识——CMOS 门电路 (与非门、或非、非门、OD 门、传输门、三态门)_摆渡沧桑的博客-CSDN 博客

- 常用电平标准——LVTTL、LVCMOS、LVDS 等_生活就是那么无聊的博客-CSDN 博客

- 常用电平及接口电平 - 道客巴巴

- I/O 接口标准(1):LVTTL、LVCMOS、SSTL、HSTL_casevison 的博客-CSDN 博客

- JESD8-23 适用于非端接数字集成电路的统一宽电源电压范围 CMOS 直流接口标准

- JESD8C-01 标称电压 3V/3.3 V 数字集成电路接口标准

版权声明:本文为「梦幻之心星」原创,依据 CC BY-NC-SA 4.0 许可证进行授权,转载请附上原文出处链接及本声明。

博客园地址:https://www.cnblogs.com/Sky-seeker

微信公众号:关注微信公众号,获取即时推送

![]()

浙公网安备 33010602011771号

浙公网安备 33010602011771号