校验和

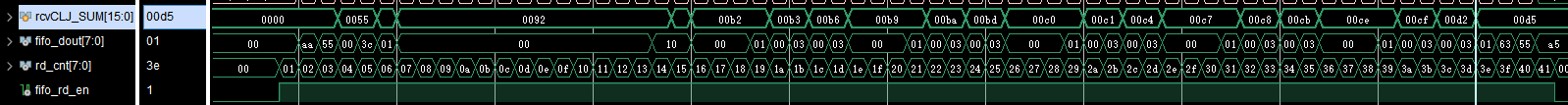

1. 对应数据位累加和:

需确认协议规定是从哪一位累加到哪一位,以及对应到代码中rd_cnt[7:0]是从第几位累加到第几位。

//校验和 reg [15:0] rcvCLJ_SUM; always @(posedge SYS_CLK or negedge sys_rst_n ) begin if(!sys_rst_n) rcvCLJ_SUM <= 16'd0; else if(rd_cnt>8'd2 && rd_cnt<8'd62 && fifo_rd_en) //从帧长位开始累加到校验和位。 rcvCLJ_SUM <= rcvCLJ_SUM + fifo_dout; else rcvCLJ_SUM <= rcvCLJ_SUM; end

调整效果如上。

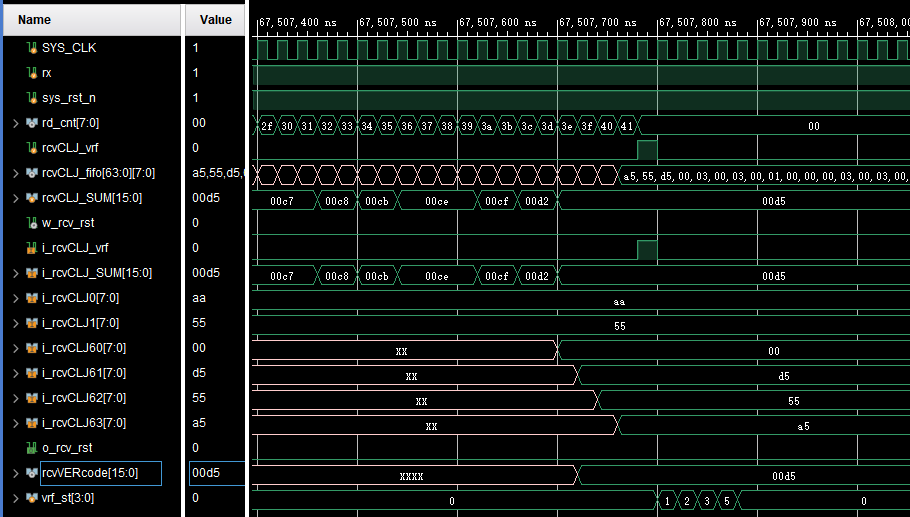

2. 帧头帧尾,校验和比对:

reg rcvCLJ_vrf; always @(posedge SYS_CLK or negedge sys_rst_n ) begin if(!sys_rst_n) rcvCLJ_vrf <= 1'd0; else if(rd_cnt== 8'd65) rcvCLJ_vrf <= 1'd1; //数据已全部存入rcvCLJ_fifo,可进行数据校准 else rcvCLJ_vrf <= 1'd0; end spi_rcvCLJ_verify spi_rcvCLJ_verify( .i_Clk(SYS_CLK), .i_Rst_L(sys_rst_n), .i_rcvCLJ_vrf(rcvCLJ_vrf), .i_rcvCLJ0(rcvCLJ_fifo[0]), .i_rcvCLJ1(rcvCLJ_fifo[1]),//帧头 .i_rcvCLJ60(rcvCLJ_fifo[60]), .i_rcvCLJ61(rcvCLJ_fifo[61]),//校验和 .i_rcvCLJ62(rcvCLJ_fifo[62]), .i_rcvCLJ63(rcvCLJ_fifo[63]),//帧尾 .i_rcvCLJ_SUM(rcvCLJ_SUM), .o_rcv_rst(w_rcv_rst) );

//校验模块

`timescale 1ns / 1ns

module spi_rcvCLJ_verify(

input i_Clk ,

input i_Rst_L ,

input i_rcvCLJ_vrf,

input [15:0] i_rcvCLJ_SUM, //get SUM

input [7:0] i_rcvCLJ0,

input [7:0] i_rcvCLJ1,

input [7:0] i_rcvCLJ60,

input [7:0] i_rcvCLJ61,

input [7:0] i_rcvCLJ62,

input [7:0] i_rcvCLJ63,

output reg o_rcv_rst

);

//verification

wire [15:0] rcvVERcode ;

assign rcvVERcode = i_rcvCLJ60 * 256 + i_rcvCLJ61;

reg [3:0] vrf_st ;

always @(posedge i_Clk) begin

if(!i_Rst_L)begin

o_rcv_rst <= 1'd0;

vrf_st<=4'h0;

end

else begin

case(vrf_st)

4'h0: begin

if(i_rcvCLJ_vrf) //verification ready

begin

vrf_st<= 4'h1;

end

end

4'h1: begin

if(i_rcvCLJ0 ==8'hAA && i_rcvCLJ1==8'h55) //frame head

vrf_st<=4'h2;

else

vrf_st<= 4'h4;//exam1

end

4'h2: begin

if(i_rcvCLJ_SUM == rcvVERcode) //vrf_code

vrf_st<=4'h3;

else

vrf_st<= 4'h4;//exam2

end

4'h3: begin

if(i_rcvCLJ62==8'h55 && i_rcvCLJ63==8'hAA) //frame_tail

vrf_st<=4'h5;

else

vrf_st<= 4'h4;//exam3

end

4'h4: begin

o_rcv_rst <= 1'd1;

vrf_st<= 4'h5;

end

4'h5: begin

o_rcv_rst <= 1'd0;

vrf_st<= 4'h0;

end

default: begin

vrf_st<=4'h0;

end

endcase

end

end

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号