数字逻辑实践3->EDA技术与Verilog设计

本文属于EDA技术概述类文章。对EDA技术现状进行介绍。

1 EDA技术及其发展

概念

EDA(Electronic Design Automation),指的是以计算机为工作平台,以EDA软件工具为开发环境,以PLD期间或者ASIC专用集成电路为目标期间设计实现电路系统的一种技术。

-

电子CAD(Computer Aided Design)

狭义的CAD 偏重于“制图”和“建模”(几何模型),广义CAD即覆盖了所有利用计算机进行辅助设计的过程,在这个意义上,CAE和EDA 也可以理解为是CAD的一种;

-

电子CAE(Computer Aided Engineering)

CAE的核心在于建模--解方程。

CAE 的关注点和出发点在于解决实际工程问题,无论是电磁仿真分析还是流体受力分析等实际问题在工程中都最终被抽象为了一个个数学方程,而得出仿真结果的过程就是求解数学问题的过程。

在CAE领域应用比较多的有有限元分析、有限差分法、加权余量法等求解方程的经典方法,所以CAE的核心在于解方程,这一过程也凝聚了工程师的智慧输出,所以说CAE和工程结合最为紧密,同时门槛极高;

-

EDA(Electronic Design Automation)

在CAD绘图技术基础上融合了应用电子技术、计算机技术、信息处理技术等实现电子产品的自动设计。

部分参考:

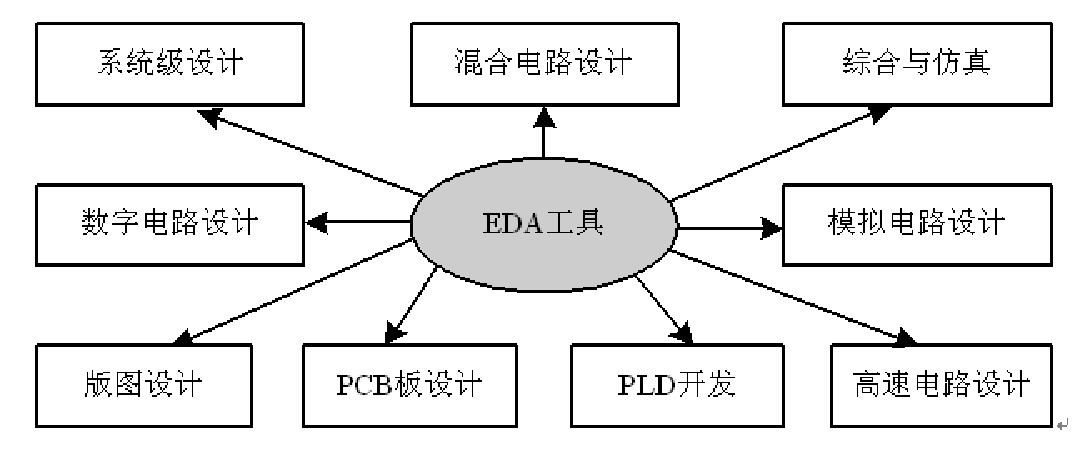

EDA技术的应用范畴

EDA技术的新发展

-

在FPGA上实现DSP应用

-

嵌入式处理器软核的成熟

-

自主知识产权

-

电子技术领域全方位融入EDA技术

-

电子领域各学科的界限更加模糊、互为包容

-

更大规模的FPGA和CPLD器件不断推出

-

IP核的广泛应用

-

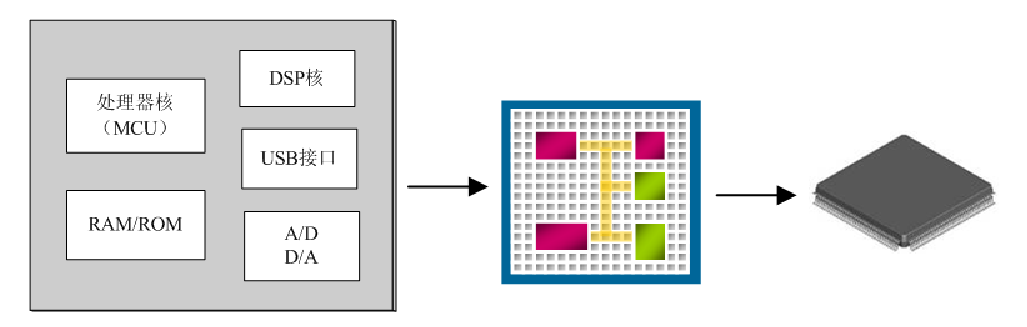

SoC高效低成本设计技术的成熟

现代EDA技术的特征

-

硬件描述语言设计输入

-

自顶向下设计方法(即 Top-down设计)

-

开放性和标准化

-

高层综合与优化

2 Top-down设计与IP核设计

Top-down设计

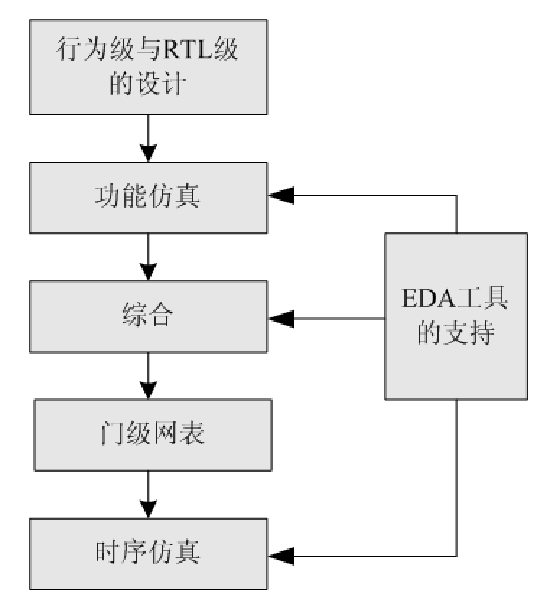

Top-down的设计须经过“设计—验证—修改设计—再验证”的过程,不断反复。

直到结果能够实现所要求的功能,并在速度、功耗、价格和可靠性方面实现较为合理的平衡。

上图就是自顶向下设计;

与之相对的是自底向上的设计(Bottom-up设计)👇

由设计者调用设计库中的元件(如各种门电路、加法器、计数器等) ,设计组合出满足自己需要的系统 缺点:效率低、易出错

好家伙,这不是Altuim Designer的设计风格吗?

IP核设计

一些词

-

IP(Intellectual Property):

原来的含义是指知识产权、著作权,在IC设计领域指实现某种功能的设计。

-

IP核(IP模块):

指功能完整,性能指标可靠,已验证的、可重用的电路功能模块。

-

IP复用(IP reuse)

-

简称调包

IP核与SOC设计

软IP--用VHDL等硬件描述语言描述的功能块,但是并不涉及用什么具体电路元件实现这些功能。

固IP--完成了综合的功能块。

硬IP--供设计的最终阶段产品:掩膜。

SoC是什么?

SYSTEM ON a CHIP

3 EDA设计的流程

设计输入(Design Entry)

-

分为两种:

-

原理图输入(Schematic diagrams )

-

硬件描述语言(HDL文本 输入)

-

VHDL

-

Verilog HDL

-

-

-

硬件描述语言与软件编程语言(C、PASCAL等)有本质的区别

综合(Synthesis)

将较高层次的设计描述自动转化为较低层次描述的过程。

-

行为综合:从算法表示、行为描述->寄存器传输级(RTL)

-

逻辑综合:RTL级描述->逻辑门级(包括触发器)

-

版图综合或结构综合:从逻辑门表示->版图表示,或->PLD器件的配置网表表示

综合器是能够自动实现上述转换的软件工具,是能将原理图或HDL语言描述的电路功能转化为具体电路结构网表的工具

综合 这个概念在硬件里相当于软件的编译。

软件编译器和硬件综合器有所差别:

软件编译(Compiler)->CPU指令/数据代码(01码)

硬件综合(synthesizer)->为ASIC设计提供电路网表文件

适配

适配器也称为结构综合器。

它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件。

对CPLD器件而言,产生熔丝图文件,即JEDEC文件;

对FPGA器件则产生Bitstream位流数据文件。

仿真

仿真是对所设计电路的功能的验证。

-

功能仿真(Function Simulation)

-

时序仿真(Timing Simulation)

编程(下载/配置)

把适配后生成的编程文件装入到PLD器件(可编程逻辑器件)中的过程, 或称为下载。

通常将对基于EEPROM工艺的非易失结构PLD器件的下载称为编程(Program);

将基于SRAM工艺结构的PLD器件的下载称为配置(Configure)。

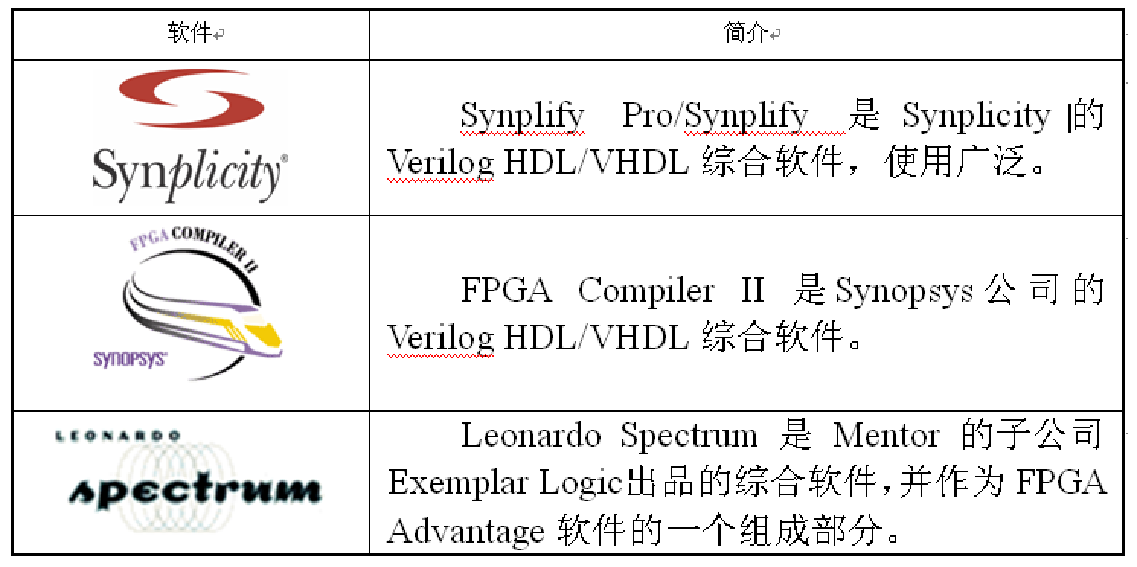

4 常用的EDA软件工具

-

集成的CPLD/FPGA开发工具

-

逻辑综合工具

-

仿真工具

-

其他设计工具

5 EDA技术的发展趋势

-

超大规模集成电路的集成度和工艺水平不断提高。

-

市场对系统的集成度不断提出更高的要求。

-

高性能的EDA工具,其自动化和智能化程度不断提高,为嵌入式系统设计提供了功能强大的开发环境。

-

计算机硬件平台性能大幅度提高,为复杂的SoC设计提供了物理基础。

浙公网安备 33010602011771号

浙公网安备 33010602011771号