第10章:VT 技术(简单了解+EPT 机制)

|

VMM:Virtual Machine Monitor,虚拟机监控器。也称为 “Hypervisior”,特权层(Ring -1),能够监控操作系统的各种行为。 CR0-CR3:控制寄存器。 CR0:控制处理器操作模式和状态 CR1:保留不用 CR2:导致页面错误的线性地址 CR3:页目录表物理内存基地址 |

VMX 功能启用时,CPU 模式分为 Root 和 non-Root 模式。只有 VMM 可以使用 Root 模式, 操作系统使用 non-Root 模式。

上图中 Guest 0 和 Guest 1 都是虚拟机,没有 VMXOFF指令,就一直处于 #VMExit 和 #VMEntry 的循环中。

记住一点,所有的虚拟操作都是以真实机为主体进行的。

创建一个典型的 VT 技术 HyperVisior 步骤:

|

· 分配 VMXON 区域和 VMCS 控制块 · 填写 VMCS 控制块,用于控制要监控什么特权指令等等一系列操作。 · 调用 VMXLaunch 指令启动虚拟机 · 当产生 VMExit 时间后调用 VMExitProc 函数处理 |

要进入 VT ,需要打开 VMX 操作模式,即使用相关的指令。

开启:VMXON -> VMXClear -> VMPTRLD -> VMWrite -> VMLaunch

关闭:VMXOFF

VMXON:开启 VMX 模式,可以执行后续的虚拟化相关指令。

VMXOFF:关闭 VMX 模式,后续虚拟化指令的执行都会失败。

VMLAUNCH:启动 VMCS指向的虚拟机 Guest OS。

VMRESUME:从 Hypervisor 中恢复虚拟机 Guest OS 的执行。

VMPTRLD:激活一块 VMCS,修改处理器当前 VMCS 指针为传入的 VMCS 物理地址。

VMCLEAR:使一块 VMCS 变为非激活状态,更新处理器当前 VMCS 指针为空。

VMPTRST:将 VMCS 存储到指定位置。

VMREAD:读取当前 VMCS 中的数据。

VMWRITE:向当前 VMCS 中写入数据。

VMCALL:Guest OS 和 Hypervisor 交互指令,Guest OS 会产生 #VMExit 而陷入 Hypervisor。

INVEPT:使 TLB 中缓存的地址映射失效。

INVVPID:使某个 VPID 所对应的地址映射失效。

一个 VMCS 就代表一个虚拟操作系统,当 VMPTRLD 指令装载 VMCS 后,就不能直接使用内存操作函数了,而需要使用上面提到的函数。

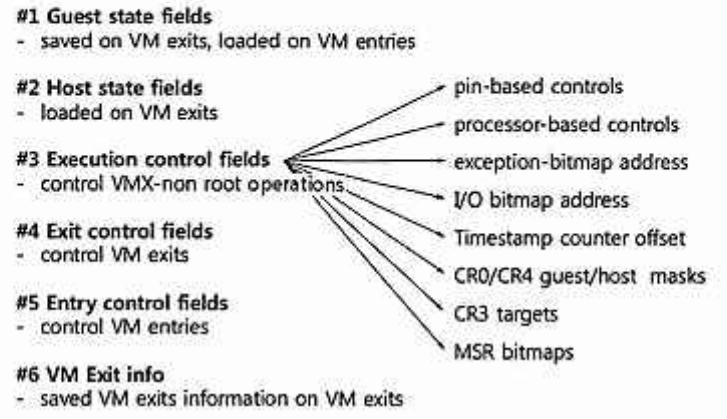

VMCS 是一个非常复杂的结构,只需要关注关键的参数即可。

在产生 #VMExit 事件时,如果出现问题,系统会发生 VMX Abort 事件。对于一个已经激活的 VMCS,Abort 事件并不会导致 VMCS 数据区被修改。VMX 退出原因指示器会指出发生 VMX Abort 事件的原因,逻辑处理器也会因此进入关闭状态。

VMCS 数据结构

|

1.虚拟机状态域 Guest-State Fields #VMEntry 时,即虚拟操作系统运行时,从这个区域加载处理器状态信息。#VMExit 时,处理器状态信息保存在这个区域。 这个区域包含了很多信息,比如各种寄存器,通用寄存器和其它类型的寄存器(MSR、GDTR.....)的部分域,处理器状态信息(处理器状态、可中断状态、VMCS 指针、PDPTE....) 2.宿主机状态域 Host-State Fields #VMExit 时,处理器状态信息从该域加载,恢复 VMM 的执行。域中存储的所有信息都与寄存器相关。例如部分 MSR、段寄存器、IDTR、GDTR... 3.虚拟机执行控制域 VM-Execution Control Fields 可以设置各种退出条件,控制 processor 在虚拟机中的行为,哪些事件会导致 #VMExit,设置 I/O 访问、MSR 寄存器访问、CR3 事件、异常等等事件,一共26个字段。 4. 虚拟机 VMEntry 控制域 VMEntry Control Fields 包含两部分:VM-Entry Controls for MSRs 和 Event Injection(interruption-information field,exception error code,instruction length 都是 32 bit) 规定了发生 #VMEntry 后的一系列操作,VMware 软件实现硬件虚拟化会用到。 5.虚拟机 VMExit 控制域 VM-Exit Control Fields 包含两部分:VM-Exit Controls For MSRs 和 VM-Exit Controls。前者指定哪些 MSRs 被存储和装载,后者指定 VM-Exit 后的操作。 6.虚拟机VM-Exit 信息域 VM-Exit Information Fields 只读区域。描述最近 VM-Exit 退出的详细原因。在某些情况下,还会有虚拟机的 Linear Address、Physical Address、Interruption Information、Interruption Error Code、IDT 向量化信息和错误码 |

EPT 机制

这篇文章给了我莫大的启发:5. EPT机制_李海伟-CSDN博客

上面的一部分是虚拟地址到物理地址的转化,下面一部分是 GPA 到 HPA 的转化。EPT 机制即是实现 GPA -> HPA 。GPA 和 HPA 都存储在内存上,只是寻址的方式不同罢了。

|

EPT:Extended Page Table,扩展页表 EPTP:Extended-Page-Table Pointer,扩展页表指针 EPT PML4T:EPT Page Map Level 4 Table , EPT PML4E 是其表项 L4 PDPT:Page-Directory-Pointer Table , PDPTE 是其表项 L3 PDT:Page-Directory Table , PDE 是其表项 L2 PT:Page Table , PTE 是其表项 L1 GPA:Guest-Physical Address,虚拟机物理地址 HPA:Host-Physical Address,真实机物理地址 EPT MMU:一块专门的用作硬件虚拟化的硬件

|

EPT 机制与 Intel CPU 上的分页机制几乎一模一样,互通的。

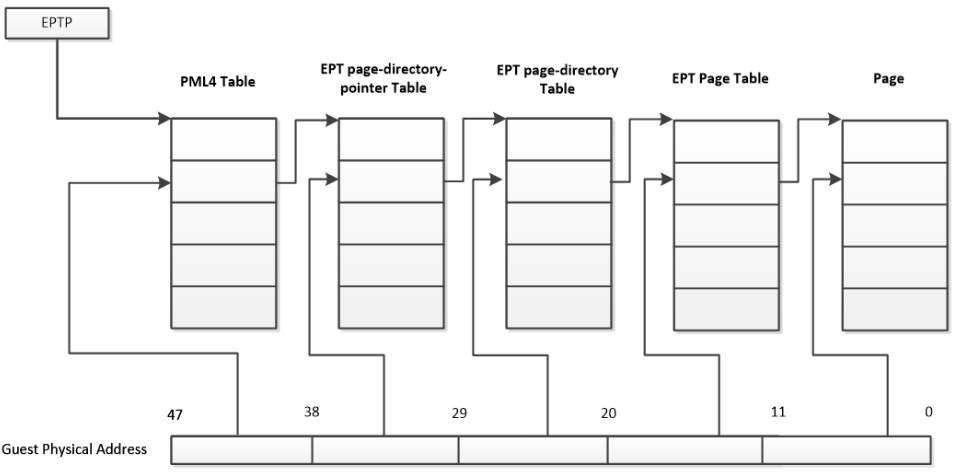

| 首先从大体上明白一点:首先通过 EPTP 可以找到 EPT PML4 :

1. 当页面选择是 4KB 时,通过5次转换找到一个 4Kb 大小的页面, EPT PML4 ——> EPT PML4E ——> PDPTE ——> PDE ——> PTE ——> Page(4KB) 2. 当页面选择是 2MB 时,通过4次转换找到一个 2MB 大小的页面,EPT PML4 ——> EPT PML4E ——> PDPTE ——> PDE ——> Page(2MB) 3. 当页面选择是 1G 时,通过3次转换找到一个 1G 大小的页面,EPT PML4 ——> EPT PML4E ——> PDPTE ——> Page(1G) 最后通过一个偏移值找到最终的 HPA 其次,在 IA32 文档中规定, 物理地址的位数最大只有 48 bits ,最多只有4级查找。 |

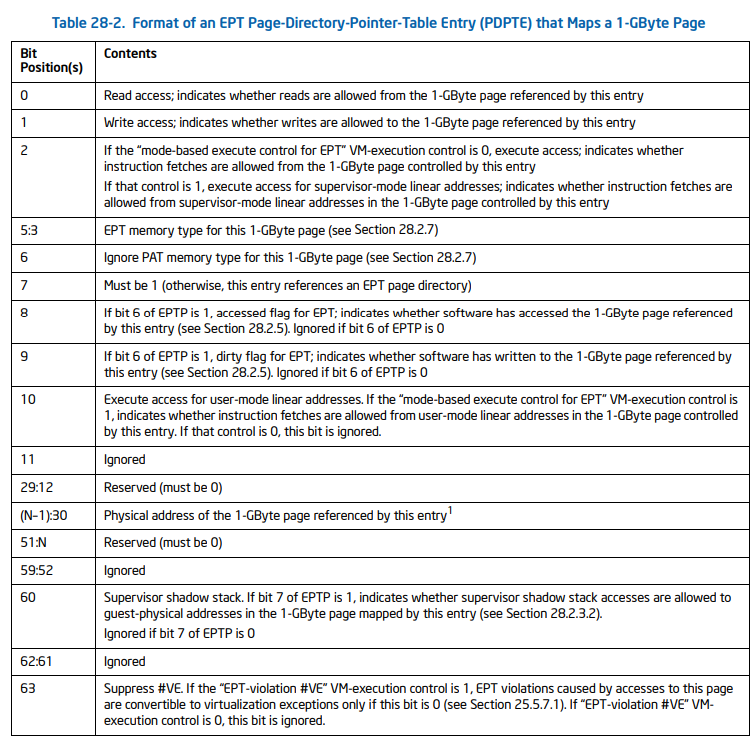

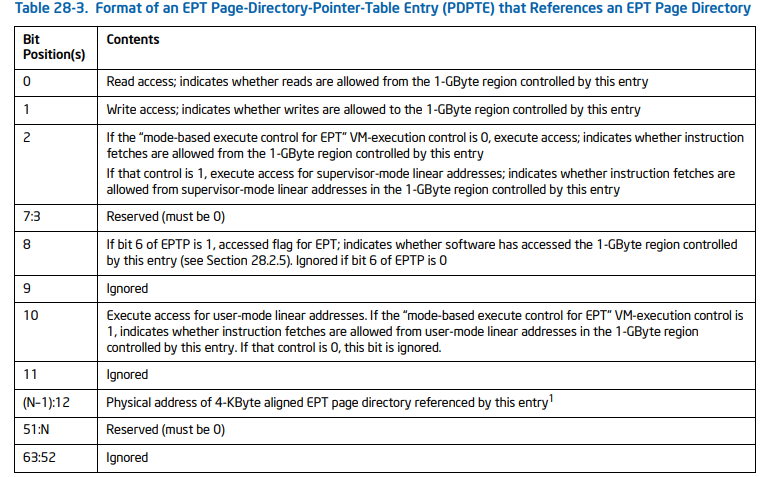

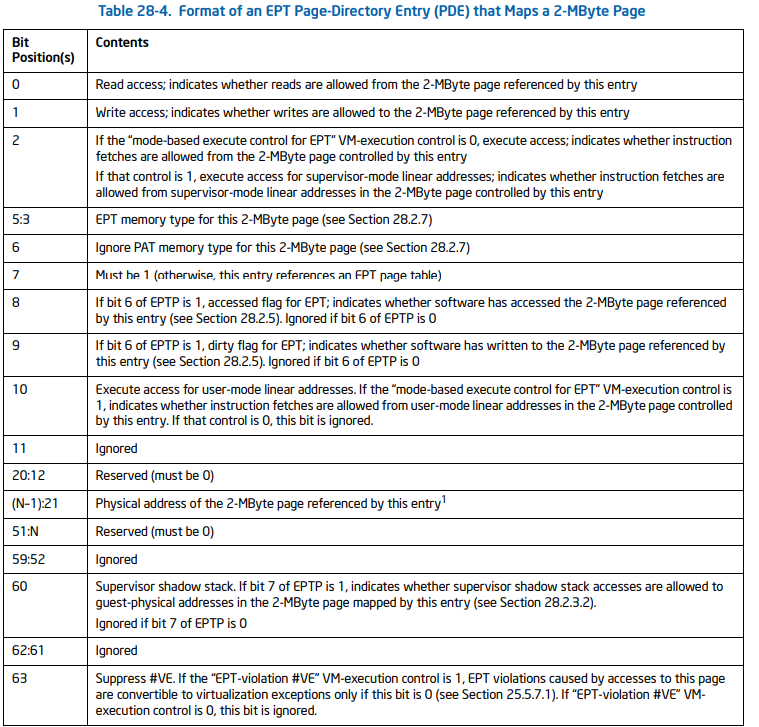

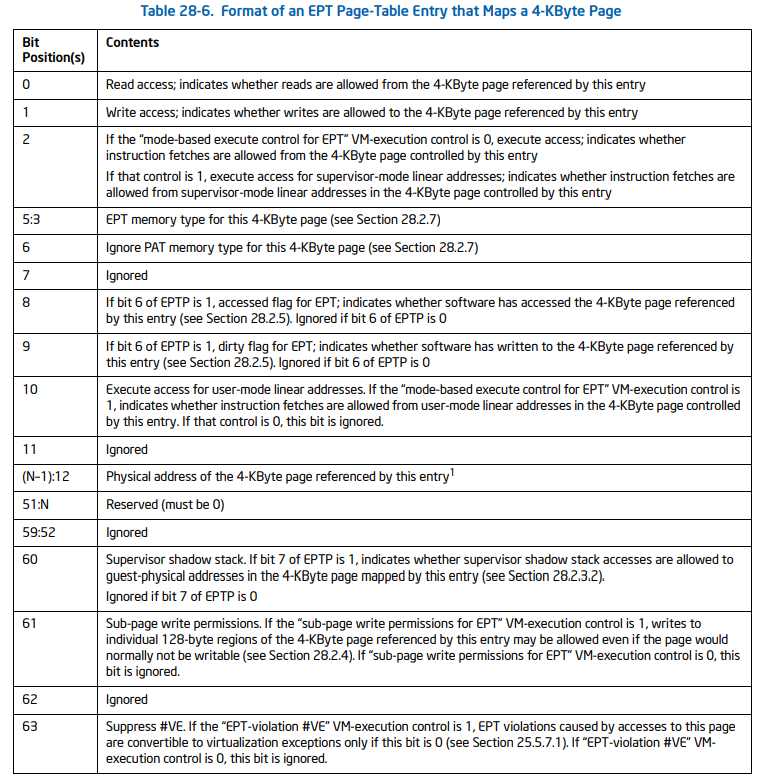

首先要了解各个结构的定义,只需要关心目前所需要的位即可。

N 是由处理器支持的物理地址宽度决定的,可以通过 CPUID 查询到支持的长度。

若后面不再找表,而是直接映射地址(1G),则 Bit 7 置 1;置 0 则继续索引,后面的表同理。

下面再来看详细的步骤(假设已经得到一个 GPA 地址 X ):

EPTP 存储在 VMCS 中,可以查找到。通过 EPTP 的 51:12 位,可以查找到 PML4 的 HPA,再通过 X 中的 47:39 位定位到具体的条目(PLM4E)。因此得到的最终的 HPA 地址如下:

— Bits 63:52 都是 0

— Bits 51:12 来自于 EPTP 的 12:51 位

— Bits 3:11 来自于 X 的 47:39 位,29 因此有 512 个条目

— Bits 2:0 都是 0

以上组成的地址(64位)即可索引到真实机物理地址上存储的 PLM4E。

PML4E 中的 51:12 不能映射地址,只能表示 PDPT 的实际物理地址。和第一步的方法相同,PDPT 的物理地址由以下组成:

— Bits 63:52 都是 0

— Bits 51:12 来自于 PML4E 的 51:12 位

— Bits 3:11 来自于 X 的 38:30 位,同样有 512 个条目

— Bits 2:0 都是 0

以上组成的地址(64位),即可索引到真实机物理地址上存储的 EPT PDPTE。

PDPTE 中的 51:12 既可以映射 1G 的页(该目录 7th bit 为 1),也可以继续向下索引,若直接映射地址则该页所在的物理地址由以下几部分组成:

— Bits 63:52 are all 0

— Bits 51:30 are from the EPT PDPTE

— Bits 29:0 are from the X (GPA 的 29:0 ),其中 12:29 全 0, 11:0 是标志位

可找到 1GB 大小的页地址。若 CPU 支持的物理地址宽度(小于等于 51)为32位则为 30:31 两个 bit 有效,索引共 4G 的页,此时 32:51 为 0。

若继续向下索引则 PDE 的物理地址由以下几部分组成:

— Bits 63:52 都是 0

— Bits 51:12 来自于 PDPTE 的 51:12 位

— Bits 11:3 来自于 X 的 29:21 位,同样有 512 个目录

— Bits 2:0 都是 0

若 EPT PDE 映射 2MB 的页(该目录 7th bit 为 1),则该页所在的物理地址(64 bits)由以下几部分组成:

— Bits 63:52 是属性标志位或 ignored

— Bits 51:21 来自 PDE

— Bits 20:0 are from the X (GPA 的 20:0 ),其中 20:12 都为 0,Bits 11:0 是标志位

管理的最小单位大小为 221 = 2 MB 。若 CPU 支持的物理地址宽度为 32 位则 31:21 为有效值,51:32 全 0 。

若继续向下索引则 PTE 的物理地址由以下几部分组成:

— Bits 63:52 are all 0.

— Bits 51:12 are from the EPT PDE.

— Bits 11:0 are from 20:12 of the X

以上所组成的64位地址,可以找到 PTE 在真实机上存储的物理地址。

PTE 只能映射一个 4KB 的页,该页的物理地址由以下几部分组成:

— Bits 63:52 are all 0.

— Bits 51:12 are from the EPT PTE.

— Bits 11:0 are from 11:0 of the X.

以上所组成的64位地址即可访问到 4KB 的页在实际物理地址中的位置。

下图是从 PML4 一直映射到 PTE 的结构图:

浙公网安备 33010602011771号

浙公网安备 33010602011771号