记一次Bug定位的过程

问题1

工作需要出bug的芯片不详细说明,该芯片的CPU含有32个中断源,一般来说,以stm32为例,中断向量表定义在startup_stm32f40_41xxx.s中,写为:

; Vector Table Mapped to Address 0 at Reset

AREA RESET, DATA, READONLY

EXPORT __Vectors

EXPORT __Vectors_End

EXPORT __Vectors_Size

__Vectors DCD __initial_sp ; Top of Stack

DCD Reset_Handler ; Reset Handler

DCD NMI_Handler ; NMI Handler

DCD HardFault_Handler ; Hard Fault Handler

DCD MemManage_Handler ; MPU Fault Handler

DCD BusFault_Handler ; Bus Fault Handler

DCD UsageFault_Handler ; Usage Fault Handler

DCD 0 ; Reserved

DCD 0 ; Reserved

DCD 0 ; Reserved

DCD 0 ; Reserved

DCD SVC_Handler ; SVCall Handler

DCD DebugMon_Handler ; Debug Monitor Handler

DCD 0 ; Reserved

DCD PendSV_Handler ; PendSV Handler

DCD SysTick_Handler ; SysTick Handler

; External Interrupts

DCD WWDG_IRQHandler ; Window WatchDog

DCD PVD_IRQHandler ; PVD through EXTI Line detection

DCD TAMP_STAMP_IRQHandler ; Tamper and TimeStamps through the EXTI line

DCD RTC_WKUP_IRQHandler ; RTC Wakeup through the EXTI line

DCD FLASH_IRQHandler ; FLASH

DCD RCC_IRQHandler ; RCC

DCD EXTI0_IRQHandler ; EXTI Line0

DCD EXTI1_IRQHandler ; EXTI Line1

DCD EXTI2_IRQHandler ; EXTI Line2

DCD EXTI3_IRQHandler ; EXTI Line3

DCD EXTI4_IRQHandler ; EXTI Line4

DCD DMA1_Stream0_IRQHandler ; DMA1 Stream 0

DCD DMA1_Stream1_IRQHandler ; DMA1 Stream 1

DCD DMA1_Stream2_IRQHandler ; DMA1 Stream 2

DCD DMA1_Stream3_IRQHandler ; DMA1 Stream 3

DCD DMA1_Stream4_IRQHandler ; DMA1 Stream 4

DCD DMA1_Stream5_IRQHandler ; DMA1 Stream 5

DCD DMA1_Stream6_IRQHandler ; DMA1 Stream 6

DCD ADC_IRQHandler ; ADC1, ADC2 and ADC3s

DCD CAN1_TX_IRQHandler ; CAN1 TX

DCD CAN1_RX0_IRQHandler ; CAN1 RX0

DCD CAN1_RX1_IRQHandler ; CAN1 RX1

DCD CAN1_SCE_IRQHandler ; CAN1 SCE

DCD EXTI9_5_IRQHandler ; External Line[9:5]s

DCD TIM1_BRK_TIM9_IRQHandler ; TIM1 Break and TIM9

DCD TIM1_UP_TIM10_IRQHandler ; TIM1 Update and TIM10

DCD TIM1_TRG_COM_TIM11_IRQHandler ; TIM1 Trigger and Commutation and TIM11

DCD TIM1_CC_IRQHandler ; TIM1 Capture Compare

DCD TIM2_IRQHandler ; TIM2

DCD TIM3_IRQHandler ; TIM3

DCD TIM4_IRQHandler ; TIM4

DCD I2C1_EV_IRQHandler ; I2C1 Event

DCD I2C1_ER_IRQHandler ; I2C1 Error

DCD I2C2_EV_IRQHandler ; I2C2 Event

DCD I2C2_ER_IRQHandler ; I2C2 Error

DCD SPI1_IRQHandler ; SPI1

DCD SPI2_IRQHandler ; SPI2

DCD USART1_IRQHandler ; USART1

DCD USART2_IRQHandler ; USART2

DCD USART3_IRQHandler ; USART3

DCD EXTI15_10_IRQHandler ; External Line[15:10]s

DCD RTC_Alarm_IRQHandler ; RTC Alarm (A and B) through EXTI Line

DCD OTG_FS_WKUP_IRQHandler ; USB OTG FS Wakeup through EXTI line

DCD TIM8_BRK_TIM12_IRQHandler ; TIM8 Break and TIM12

DCD TIM8_UP_TIM13_IRQHandler ; TIM8 Update and TIM13

DCD TIM8_TRG_COM_TIM14_IRQHandler ; TIM8 Trigger and Commutation and TIM14

DCD TIM8_CC_IRQHandler ; TIM8 Capture Compare

DCD DMA1_Stream7_IRQHandler ; DMA1 Stream7

DCD FSMC_IRQHandler ; FSMC

DCD SDIO_IRQHandler ; SDIO

DCD TIM5_IRQHandler ; TIM5

DCD SPI3_IRQHandler ; SPI3

DCD UART4_IRQHandler ; UART4

DCD UART5_IRQHandler ; UART5

DCD TIM6_DAC_IRQHandler ; TIM6 and DAC1&2 underrun errors

DCD TIM7_IRQHandler ; TIM7

DCD DMA2_Stream0_IRQHandler ; DMA2 Stream 0

DCD DMA2_Stream1_IRQHandler ; DMA2 Stream 1

DCD DMA2_Stream2_IRQHandler ; DMA2 Stream 2

DCD DMA2_Stream3_IRQHandler ; DMA2 Stream 3

DCD DMA2_Stream4_IRQHandler ; DMA2 Stream 4

DCD ETH_IRQHandler ; Ethernet

DCD ETH_WKUP_IRQHandler ; Ethernet Wakeup through EXTI line

DCD CAN2_TX_IRQHandler ; CAN2 TX

DCD CAN2_RX0_IRQHandler ; CAN2 RX0

DCD CAN2_RX1_IRQHandler ; CAN2 RX1

DCD CAN2_SCE_IRQHandler ; CAN2 SCE

DCD OTG_FS_IRQHandler ; USB OTG FS

DCD DMA2_Stream5_IRQHandler ; DMA2 Stream 5

DCD DMA2_Stream6_IRQHandler ; DMA2 Stream 6

DCD DMA2_Stream7_IRQHandler ; DMA2 Stream 7

DCD USART6_IRQHandler ; USART6

DCD I2C3_EV_IRQHandler ; I2C3 event

DCD I2C3_ER_IRQHandler ; I2C3 error

DCD OTG_HS_EP1_OUT_IRQHandler ; USB OTG HS End Point 1 Out

DCD OTG_HS_EP1_IN_IRQHandler ; USB OTG HS End Point 1 In

DCD OTG_HS_WKUP_IRQHandler ; USB OTG HS Wakeup through EXTI

DCD OTG_HS_IRQHandler ; USB OTG HS

DCD DCMI_IRQHandler ; DCMI

DCD CRYP_IRQHandler ; CRYP crypto

DCD HASH_RNG_IRQHandler ; Hash and Rng

DCD FPU_IRQHandler ; FPU

__Vectors_End

__Vectors_Size EQU __Vectors_End - __Vectors

AREA |.text|, CODE, READONLY

其中的XX_Handler为中断服务函数,对中断服务函数进行实现后即可使用,我们开发芯片程序时常用的一种设计思路是这样的:

- 主程序中定义一个全局变量

flag用于记录是否有外部输入需要处理,打开中断,执行后台任务并检测输入flag - 进入中断后关闭中断并执行中断服务函数

- 中断服务函数中对

flag进行赋值,标记触发来源 - 中断服务函数打开中断,退出

- 主程序检测到输入

flag,执行相关高优先级任务后,继续执行后台任务,等待下一次外部输入

按照上面的设计思路,假设我们以TIM3_IRQHandler中断为例,在主函数中这样实现:

unsigned int flag = 0;

int main(void)

{

flag = 0

while(flag==0)

{

;

}

//do something for IRQ

}

在中断服务函数中对flag进行修改表示触发了中断:

void TIM3_IRQHandler(void)

{

flag = 1;

TIM_ClearITPendingBit(TIM3, TIM_IT_Update); //清除中断标志位

}

运行程序后的结果是这样(举例说明):程序在进入中断服务函数后对flag进行置位并返回但是并未退出while循环,即flag的修改没有起作用。

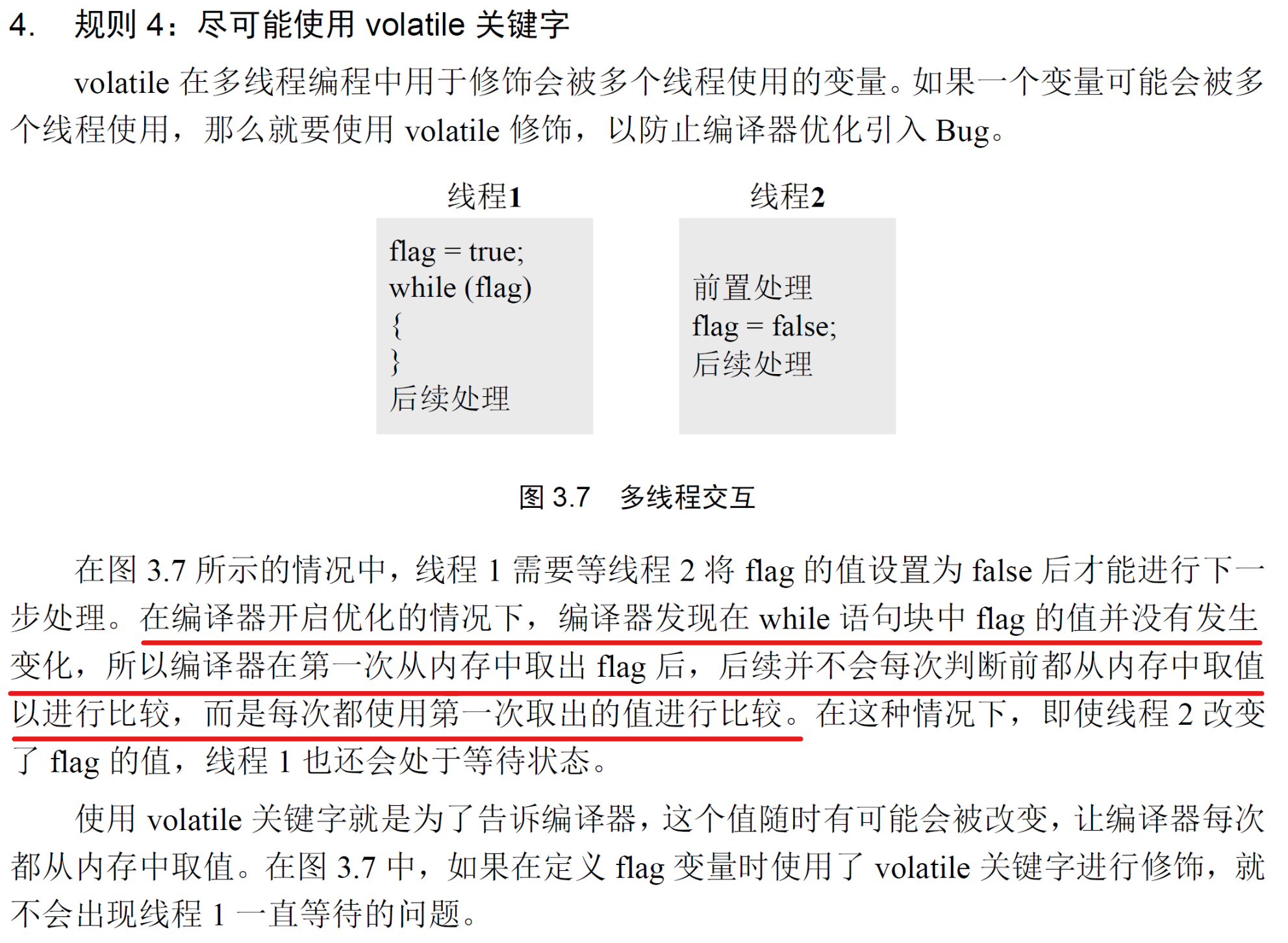

这里最直接的原因是在汇编程序中比较的两个寄存器的值并未修改,即C代码在编译后对结果进行了优化,参考:周立功著 软件单元测试入门与实践 23页:

因此最直接的办法是用volatile关键字对变量进行修饰,当然也有其他办法,出现问题的直接因素在于flag=0和while(flag==0)被编译器直接优化掉了,这里可以写一个伪函数对flag进行一个操作绕开编译器的优化判断,但是增加了额外的开销,并不合适:

flag = 0;

fake_func(&flag);

while(flag==0);

//do something

问题2

中断是由通信单元产生的,在解决了中断无响应的问题后出现了上电复位后打印输出不稳定的现象,且发生次数和时间不固定。由于数据是在配置时钟后发出,中间无其他操作,初步认为是配置时钟造成的原因,芯片采用内部时钟,因此增加约10ms延时后输出稳定不再发生乱码,原因应该是PLL需要锁定时间,因此不能在配置PLL后直接执行与时序有关的操作。

这里再记录一个小技巧,如何在芯片手册说明不明确的情况下找到中断源。当确定一个中断触发后调用了中断服务函数的时候,先将所有可能的中断服务函数都写出来,然后依次关闭和打印,直到确定相应的中断来源

浙公网安备 33010602011771号

浙公网安备 33010602011771号