ISA的折中

ISA和微结构之间的权衡

什么是ISA

ISA是指令集,是一种归约,规定了如何使用硬件,是硬件的抽象。(是一系列规定)

无论怎么实现底层硬件,程序员看到的执行结果与定义指令设计应当一致。

什么是微结构

负责实现ISA规定的操作

ISA与微体系结构的区别

微体系结构要在满足特定的设计限制和目标情况下实现ISA。

判断

ADD指令的操作码。属于ISA。

通用寄存器的数目。属于ISA。

到寄存器文件的端口数目。属于微体系结构。

执行MUL指令的周期数。微体系结构。

机器决定是否采用流水线执行。微体系结构。

设计点

一系列的设计需要考虑,导致了需要在ISA和微体系结构之间权衡

价格,性能,功耗等等。

Tradeoffs(计算机体系结构的关键)

折中的级别

ISA级别的折中

微体系结构级别的折中

系统和任务级别的折中:如软硬件接口

ISA设计原则

指令

组成

操作码:指令的功能。

操作数:被指令操作的数。

寻址模式决定了如何获取操作。

例如

RA RB RC:三操作数,如两个操作数相加存储到第三个操作数

RA RB:两操作数,如load指令,基地址加 + 偏移

RA:单操作数,如直接访存。

Number:特权指令

Unused 指令:用于保留,方便扩展

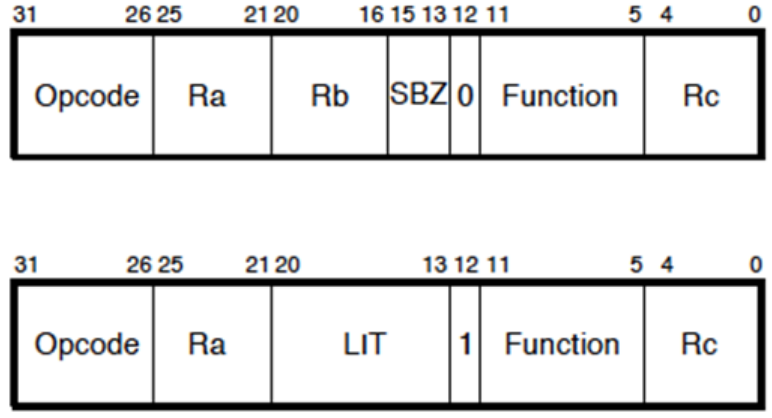

指令中的转向位

第12位表示译码方式,标签前面12位应该编译成寄存器还是其他的。

第12位为0表示,Rb作为源寄存器的操作数

第12为为1表示,<20:13>部分被解释为0到255之间的正整数,且是64位的0扩展。

ISA级别折中的方案

指令排序模型

决定控制流还是数据流

指令处理方式

指定操作数的数量和指令操作的执行方式

0-address: 堆栈机 (push A, pop A, op)

1-address: 累加器 (ld A, st A, op A)

2-address: 2操作数机器 (one is both source and dest)

3-address: 3操作数机器 (source and dest are separate)

Stack Machine(堆栈机)

所有元素在栈中。

操作数存在数据栈中,栈顶元素参与计算。

只支持两操作数,对于向量运算难以实现。

指令类别

操作指令:处理数据,获取数据,计算结果,存储结果。隐式顺序数据流

数据移动指令:在内存,寄存器,IO设备之间移动指令。隐式顺序数据流

控制流指令:改变指令执行的顺序。

数据类型

Integer, floating point, character, binary, decimal, BCD

ISA中有高级数据类型,好处是减轻了程序员的负担;缺点是底层微架构负担重

语义鸿沟(sematic gap)

也就是可读性,指令集越复杂,提供的指令种类越多,其可读性越好;而越精简的指令集,其许多功能需要软件实现,可读性就更差。

越接近高级语言,语义鸿沟越小,但是指令越复杂。(如复杂指令集CISC)

越接近低级语言,语义鸿沟越大,指令越简单。(如精简指令集SISC)

语义鸿沟大

每条指令都规定了机器中的整套控制信号。

编译器生成控制信号。

语义鸿沟小

ISA与高级语言相似。

存储结构

地址空间:内存中有多少唯一可识别的位置。

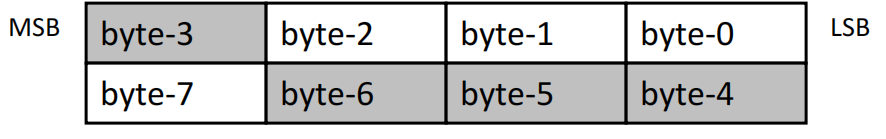

可寻址性:每一个可识别的位置可以存储多少数据。需要思考的问题如,位可寻址,字节可寻址,64位可寻址,32位可寻址,大尾端or小尾端。

影响最大的位放在高位,就是大尾端

影响最大的为放在低位,就是小尾端

更多寻址模式的优缺点

可以将高级别结构更好的映射到底层,编译器,微架构需要做更多工作。

寄存器

关键问题

数量多少

每个寄存器大小

有寄存器的好处

因为程序具有数据局部性,同一个数据在一段时间内可能会被多次访问。

ISA的 load-store结构 与 内存-内存结构

load-store结构:操作指令只在寄存器上操作。要通过load-stroe从内存中加载或存储数据。

memory-memory结构:操作指令可以在内存上操作。

与IO设备连接方式

内存映射IO:将内存区域映射到IO设备,I/O操作主要是对这些位置加载和存储

特殊IO指令:专门指令映射如X86中IN和OUT指令,处理芯片的端口。

要权衡哪种方式更加通用。

特权模式

各个模式分别能执行什么指令

异常和中断处理

指令出现问题,遵循什么程序?外部设备请求时,遵循什么程序?矢量中断or非矢量中断

虚拟内存

让内存看起来比实际内存大得多。

访问保护

复杂指令还是简单指令

复杂指令

一个指令可以做更多的工作。

优点

编码紧凑,编码占用位置小,内存利用率高。(因为是专门编写的)。

缺点

编译器能做优化的机会更少,硬件复杂度更高。

简单指令

一个指令只能处理少数工作,但是可以用其构造复杂指令。

指令长度trade-off

固定长度(统一解码也是这样)

所有指令长度固定。

好处

在硬件中容易解码单个指令。

容易并行解码。

缺点

指令中会浪费多余的位

ISA难以扩展

可变长度(非统一解码也是这样)

指令长度不固定。

好处

更紧凑

缺点

解码单个指令更复杂。

难以并行解码。

权衡

码长 和 硬件复杂性 之间。

ISA的 可扩展性 和 可读性 之间

更紧凑的码 和 更容易解码 之间权衡

寄存器个数的权衡

寄存器个数的影响

-

-

-

- 用于编码寄存器地址的位数。(寄存器越多,其寄存器地址所需的位数也就越多)

- 保存在快速存储中的值的数量(寄存器文件)

- 寄存器文件的大小、访问时间、功耗

-

-

寄存器数量多

编译器可以更好的分配寄存器

更大的指令尺寸

更大的寄存器文件大小

寻址模式

寻址模式决定了如何获取到一个指令的操作数。

更多的寻址模式

好处

帮助更好的编程构造(如基于array的访问,基于指针的访问)

缺点

但是使得结构设计更难

编译器的选择太多

MIPS对齐访问与非对齐访问

对齐访问

对齐访问不能跨边界

如访问3,4,5,6

计算机访问的最小单位是Byte

如访问0前半部分和1的后半部分,就无法去取。

非对齐访问

当跨边界的时候

LWL取低位,LWR取高位。

拼在一起。

但是速度很慢。

内部本质上还是对齐访问

X86可随意访问,但是需要程序员负责

LD/ST指令会自动划分数据边界。程序员不需要担心

微体系结构

指令处理过程——冯诺依曼模型

处理一个指令之前的体系结构状态A -> 处理一个指令之后的体系结构状态A'

ISA决定给定的状态A应该变成什么样的状态A'。(定义一个有限状态机决定状态;从ISA角度看,A到A'没有中间状态。)

微体系结构决定如何将状态A变成状态A'。(可以选择没有中间状态,对程序员不可见,提高速度。若选择有中间状态,速度慢)

指令是按照控制单元的方向一步一步执行的

指令周期:处理一个指令时的一系列步骤,通常包含5个步骤。

单周期机器

每个指令只有一个时钟周期,也就是5个步骤需要1个时钟周期完成。

在指令执行结束会产生所有的状态更新。

缺点:最慢的指令决定了整个周期

多周期机器

单个指令被分解为多个周期执行,也就是5个步骤可以使用多个时钟周期完成,事实上每阶段需要多个时钟周期完成。

指令执行期间会产生状态更新。

指令执行结束会产生体系结构状态更新。

优点:单个指令中,最慢的一个stage决定整个周期

指令执行步骤

取指令

解码

执行

load/store

写会结果

数据通路角度看体系结构变换

转换是由一系列功能单元组成,这些单元被告知对数据做什么

指令处理包含两个组件:

数据路径:由 处理和转换数据的信号的硬件组成。

控制逻辑:由 决定控制信号的硬件组成。

单周期和多周期

都有控制信号和数据信号

单周期中,控制信号在处理数据信号的同一时钟周期内生成。所有与指令相关的都在一个周期内处理完。

多周期中,下一个周期的控制信号提前一个周期生成。好处是控制处理的延迟可以和路径操作的延迟重叠。

本文来自博客园,作者:Laplace蒜子,转载请注明原文链接:https://www.cnblogs.com/RedNoseBo/p/17191650.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号