Cortex-M3初探

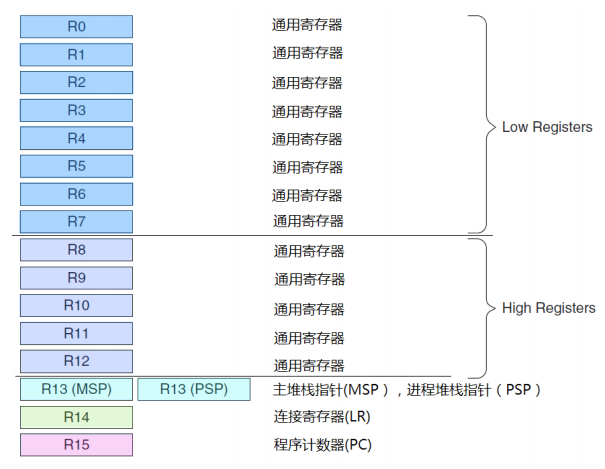

寄存器组

Cortex-M3处理器拥有R0-R15的寄存器组,其中R0-R12为通用寄存器;R13作为堆栈指针SP(SP主堆栈指针MSP和进程堆栈指针PSP);R14为连接寄存器;R15为程序计数器。

R0-R12:通用寄存器

R0-R12都是32位的通用寄存器,主要用于暂存数据和中间计算结果,在函数调用过程中函数的参数以及在多任务系统中任务的上下文信息通常通过R0-R3进行保存。

R13:两个堆栈指针 SP

Cortex-M3有两个堆栈指针,在任一时刻只能使用其中一个。

主堆栈指针(MSP):复位后缺省使用的堆栈指针,用于操作系统内核及异常处理例程(中断服务例程使用的永远都是MSP)。

进程堆栈指针(PSP):由用户的应用程序代码使用。

R14:连接寄存器 LR

LR寄存器主要用于存储函数调用的返回地址,当执行函数调用指令,当前函数地址会被存储到LR寄存器中,这样在函数执行结束后,处理器就可以使用LR寄存器中的地址返回到调用该函数的地方。在发生异常处理时处理器也会将当前地址存储到LR寄存器中,以便在异常处理结束后返回到异常发生的地方继续执行。

R15:程序计数寄存器 PC

PC寄存器存储当前正在执行的指令的地址,它是处理器执行指令的关键,每执行一条指令,PC寄存器的值自动增加指向下一条要执行的指令。

注意区分一下LR寄存器和PC寄存器:LR寄存器是用于存储函数调用或异常处理的返回地址,它的更新与程序函数调用和异常处理直接相关;PC寄存器负责控制和管理程序的指令执行流程,它的更新是由处理器硬件自动管理的,它直接控制了程序的执行顺序和指令的流动。

特殊功能寄存器

Cortex-M3在内核上还搭载了若干特殊功能寄存器,如程序状态字寄存器(xPSR)、中断屏蔽寄存器组(PRIMASK、FAULTMASK、BASEPRI)、控制寄存器(CONTROL)。

xPSR寄存器

记录ALU标志(0标志,进位标志,负数标志,溢出标志)、执行状态、当前正在服务的中断号。

PRIMASK寄存器

该寄存器用于屏蔽所有可编程中断,当然不可编程中断如NMI、硬(hard)fault是不可编程的所以无法屏蔽。

FAULTMASK寄存器

该寄存器也可用于屏蔽中断,但相比于PRIMASK,该寄存器会屏蔽除NMI之外的所有中断,即便是硬(hard)fault也会被屏蔽掉。

BASEPRI寄存器

屏蔽优先级小于等于某个值的中断,如设置为5则表示屏蔽掉优先级小于等于5往后的所有中断,优先级比5大的则不会屏蔽。该寄存器写0表示不屏蔽任何中断。

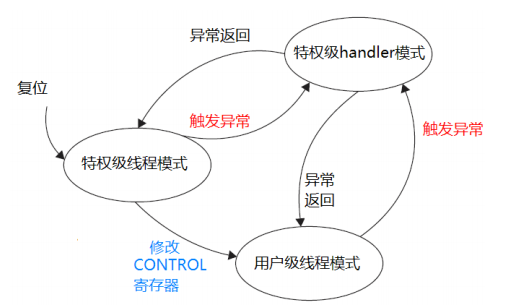

CONTROL寄存器

定义特权状态(特权级还是用户级),并且决定使用哪一个堆栈指针(MSP还是PSP)。

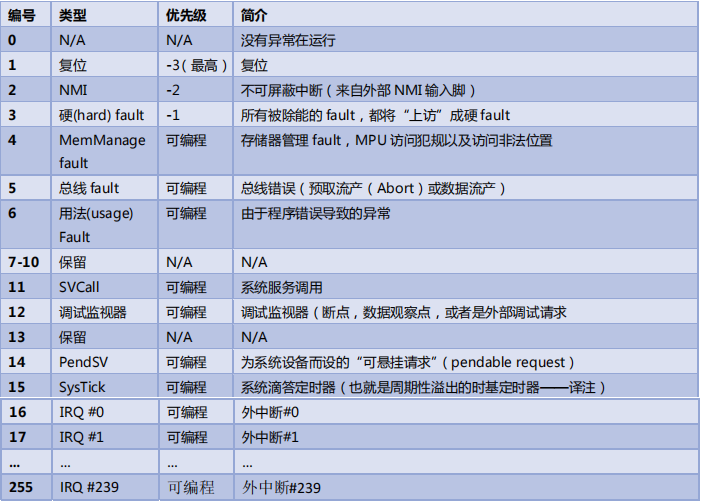

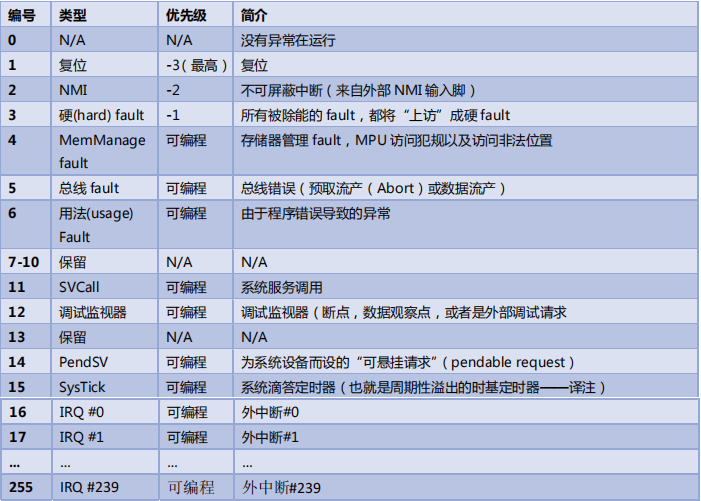

以下为Cortex-M3异常类型

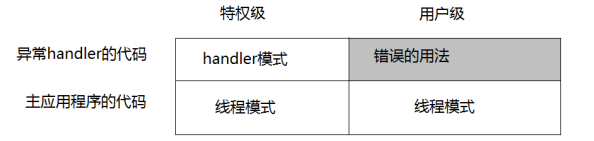

操作模式与特权级别

Cortex-M3支持两种处理器模式和两个特权操作。

两种处理模式为:handler模式和线程模式。引入两种模式的本意是用于区分普通的应用程序代码和异常服务例程代码。

两种特权级别为:特权级和用户级。

在CM3运行主程序时(线程模式),既可以使用特权级也可以使用用户级,但是异常服务例程必须在特权级下执行。复位后处理器默认进入线程模式、特权级。在特权级下程序可以访问所有范围的存储器(如果有MPU内存管理单元则要在MPU规定的禁地之外),并且可以执行所有指令。

用户级切换为特权级的流程

用户级程序不能通过简单的修改CONTROL寄存器的值就进入特权级,它必须先进行“申诉”:执行一条系统调用指令SVC,这将会触发SVC异常由异常服务例程接管,如果批准了进入,则异常服务例程修改CONTROL寄存器才能从用户级进入特权级(要明白异常服务例程是在特权级下执行的,也就是说只有在特权级下进行修改CONTROL寄存器才能从用户级进入特权级)。

操作系统的内核通常都是在特权模式下运行,因为需要访问一些特殊的存储器、寄存器。

内建的嵌套向量中断控制器 NVIC

NVIC与内核是紧耦合的,它不属于某一款芯片的外设,其属于内核,所以如果大家去查阅相关如中文参考手册能找到的描述其实是不多的。因为类似中文参考手册大多介绍的是某一系列单片机的基本外设,NVIC不属于某一系列芯片的外设,它属于内核。

NVIC提供以下功能:

可嵌套的中断管理

向量中断支持

动态的优先级调整支持

中断延迟大大缩短

中断可屏蔽

可嵌套的中断支持

当一个异常发生时,硬件会自动比较该异常的优先级是否比当前异常优先级更高,如果更高,处理器会中断当前的中断服务例程,而服务新来的异常---即抢占。

向量中断支持

当开始响应一个中断后,CM3会自动定位一张向量表,并且根据中断号从向量表中找到中断服务例程的入口,然后跳转过去执行。

动态优先级调整支持

软件可以在运行时更改中断的优先级,如果在某个中断服务例程中修改了自己对应的中断优先级,而这个中断又有新的实例处于悬起中,也不会自己打断自己。

中断延迟大大缩减

Cortex-M3为了缩减中断延迟引入了好几个新特性,包括自动现场保护和恢复,咬尾中断和晚到中断,用于缩短中断嵌套时的ISR间的延迟。

咬尾中断简单来说就是在上一个中断执行完毕后不进行POP相关的寄存器,而是下一个异常继续使用上一个异常已经PUSH好的成果,形成首位紧密衔接的情况,所以叫做咬尾中断。

晚到中断就是如果在响应某一低优先级异常#1的早期检测到了更高优先级异常#2,只要#2不是太晚到就能以晚到中断的方式处理。即#1进行入栈结束后执行#2的服务例程,相当于#1帮#2做了入栈动作(徒做嫁衣了)。

中断可屏蔽

即可以屏蔽优先级低于某个阈值的中断(通过设置BASEPRI寄存器),也可以进行全体封杀(通过设置PRIMASK或FAULTMASK)。操作系统中的临界区操作常常使用到BASEPRI寄存器屏蔽某些中断以实现临界操作。

中断和异常

CM3支持16-4-1=11中系统异常(保留了4+1个档位),外加240个外部中断输入。CM3中取消了FIQ(快速中断请求,用于处理一些高优先级、对响应时间要求极高的中断事件),因为有了更好的机制---中断优先级管理和嵌套中断支持。CM3的所有中断机制都是由NVIC实现的。

要注意,虽然CM3支持多达256个中断,但具体使用的数量多少是由芯片生产商来决定的。

浙公网安备 33010602011771号

浙公网安备 33010602011771号