手把手教你Nucleistudio+Vivado协同仿真教程

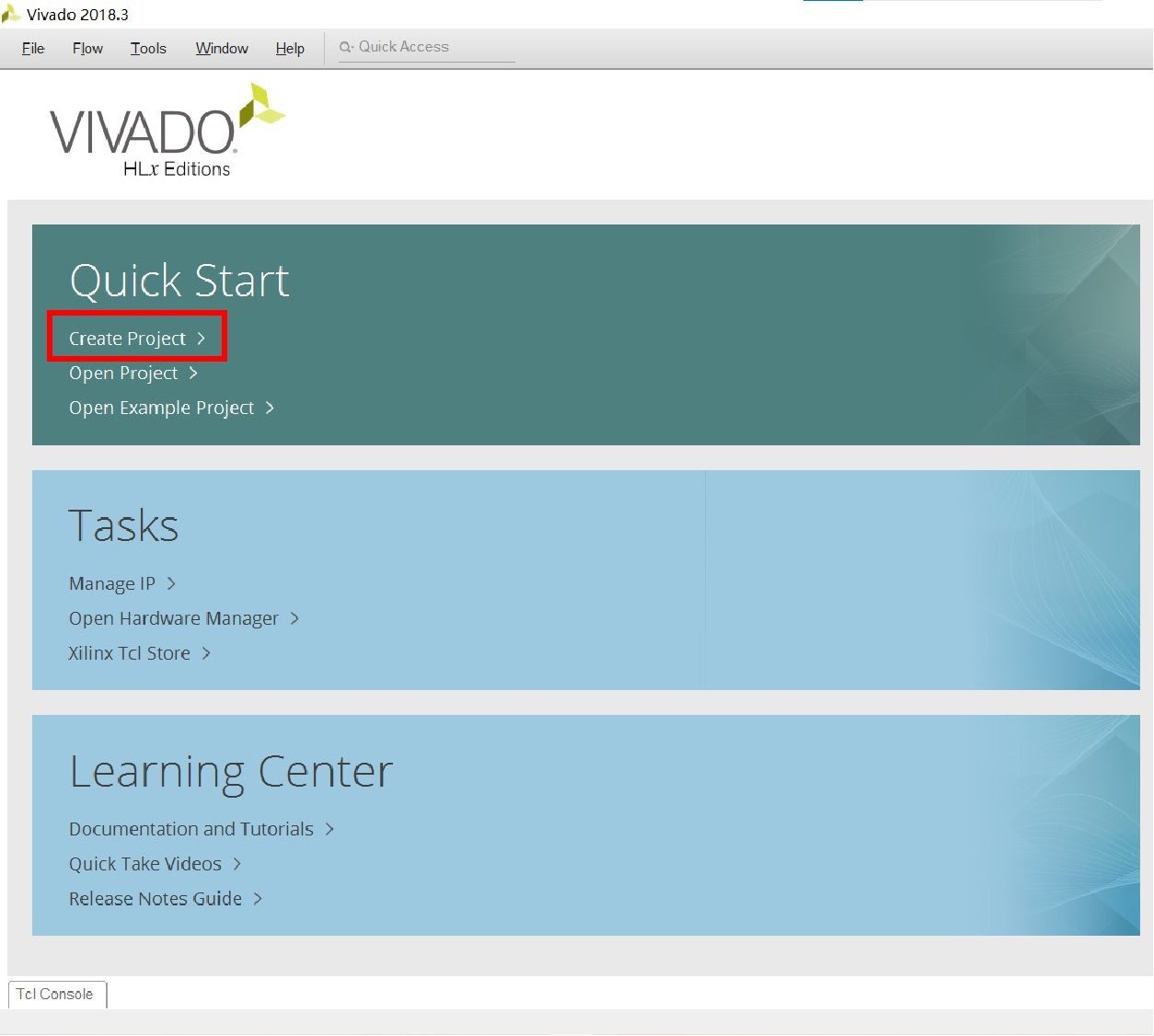

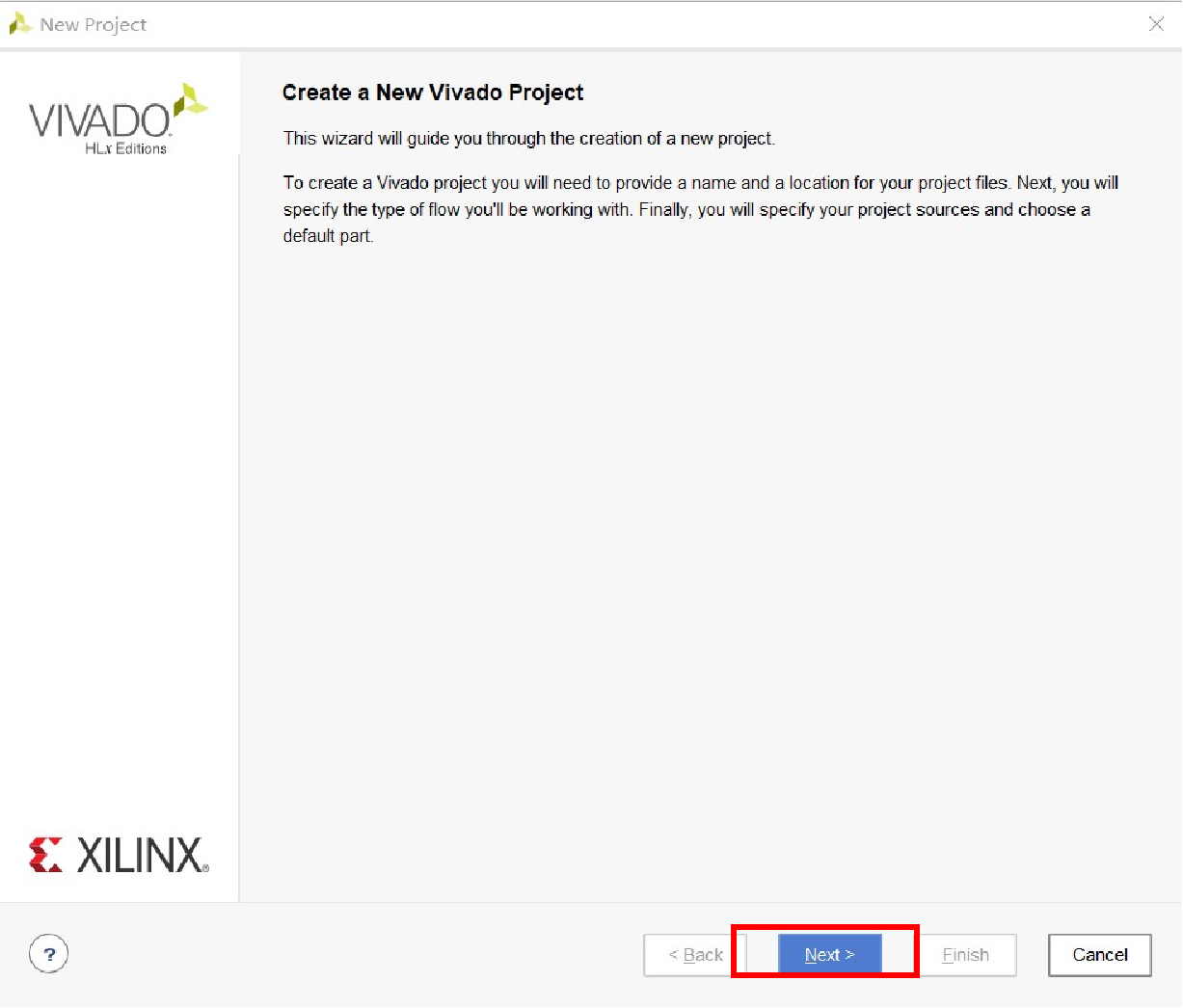

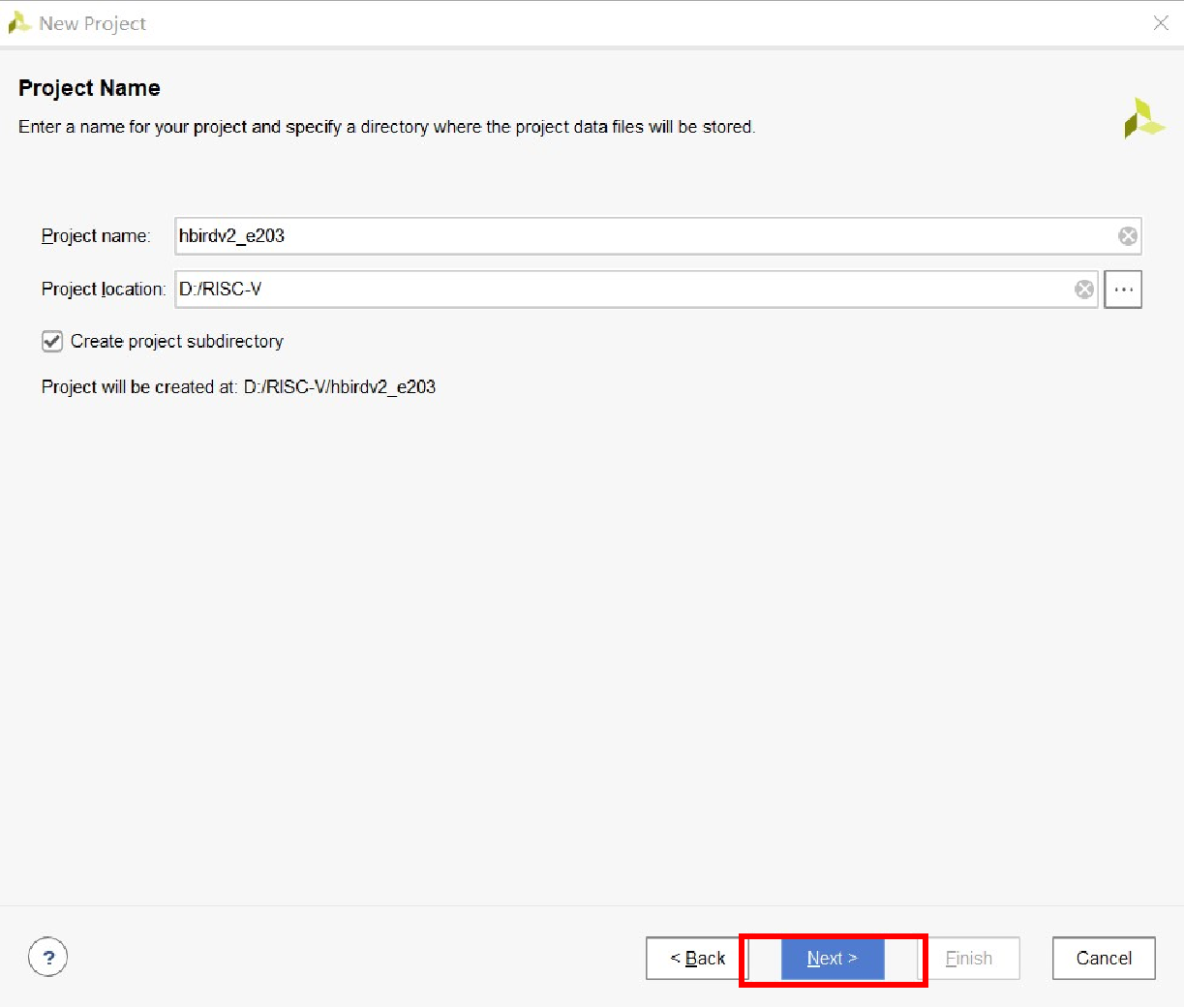

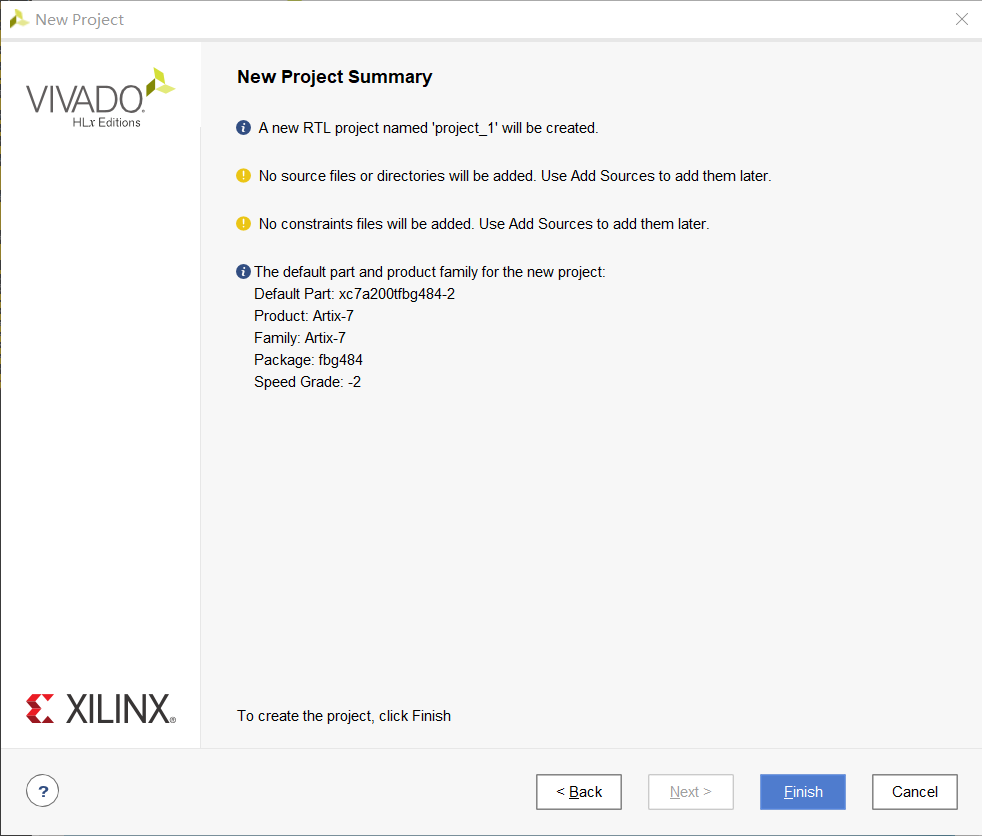

创建Vivado工程

- 1.创建工程:

在Vivado中创建工程,命名随意,路径随意;

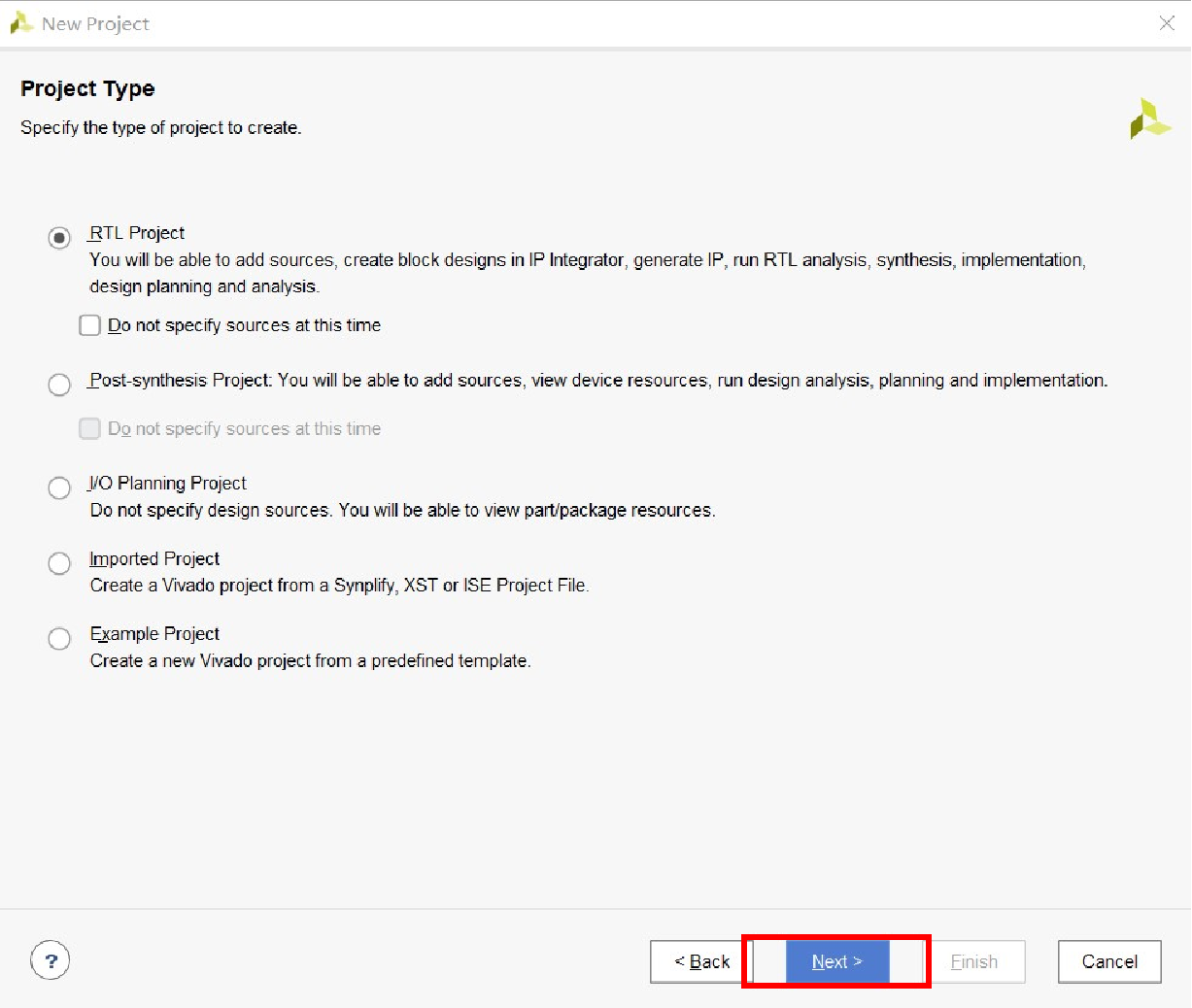

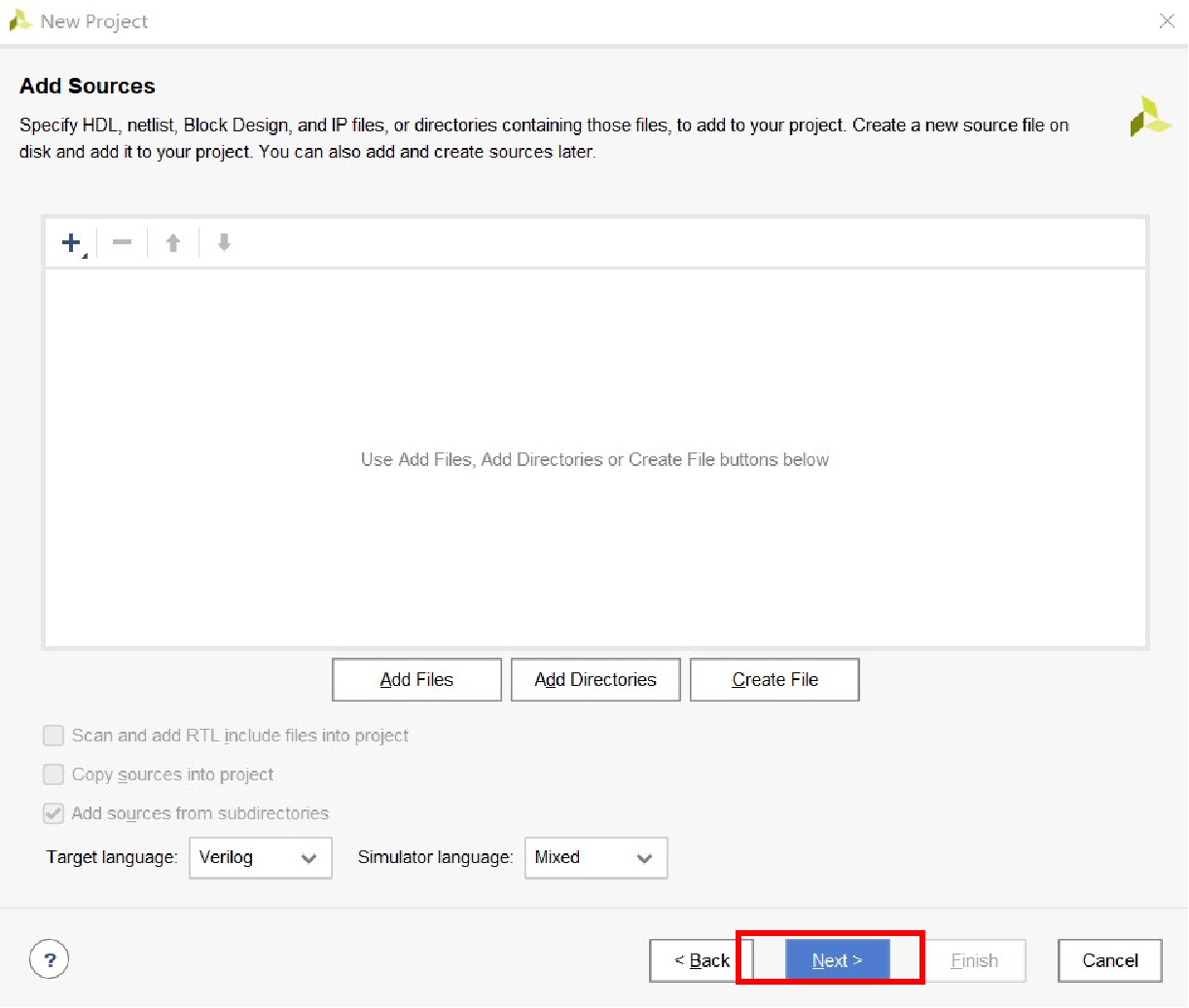

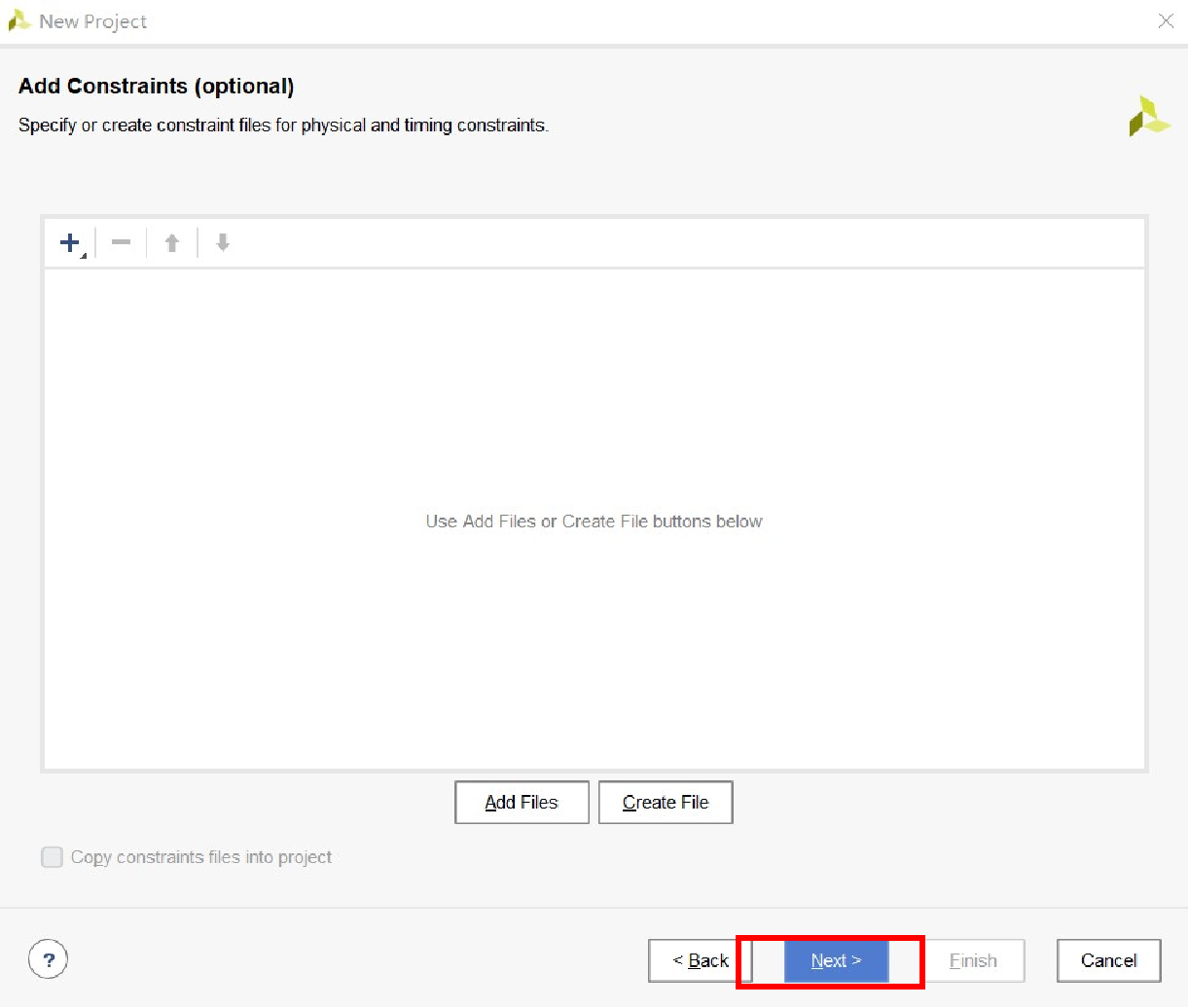

- 2.配置工程:

这里可以选择是否添加源文件等,我们先不添加;

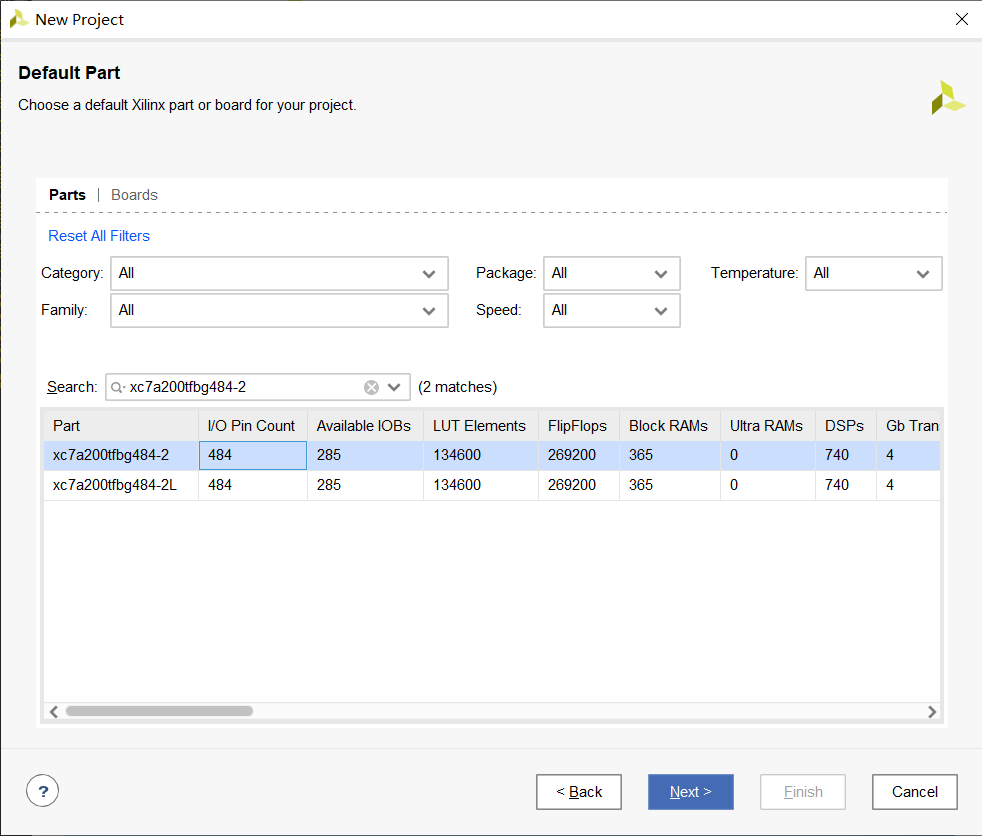

- 3.选择FPGA核心:

选择MCU200T对应的FPGA核心xc7a200tfbg484-2

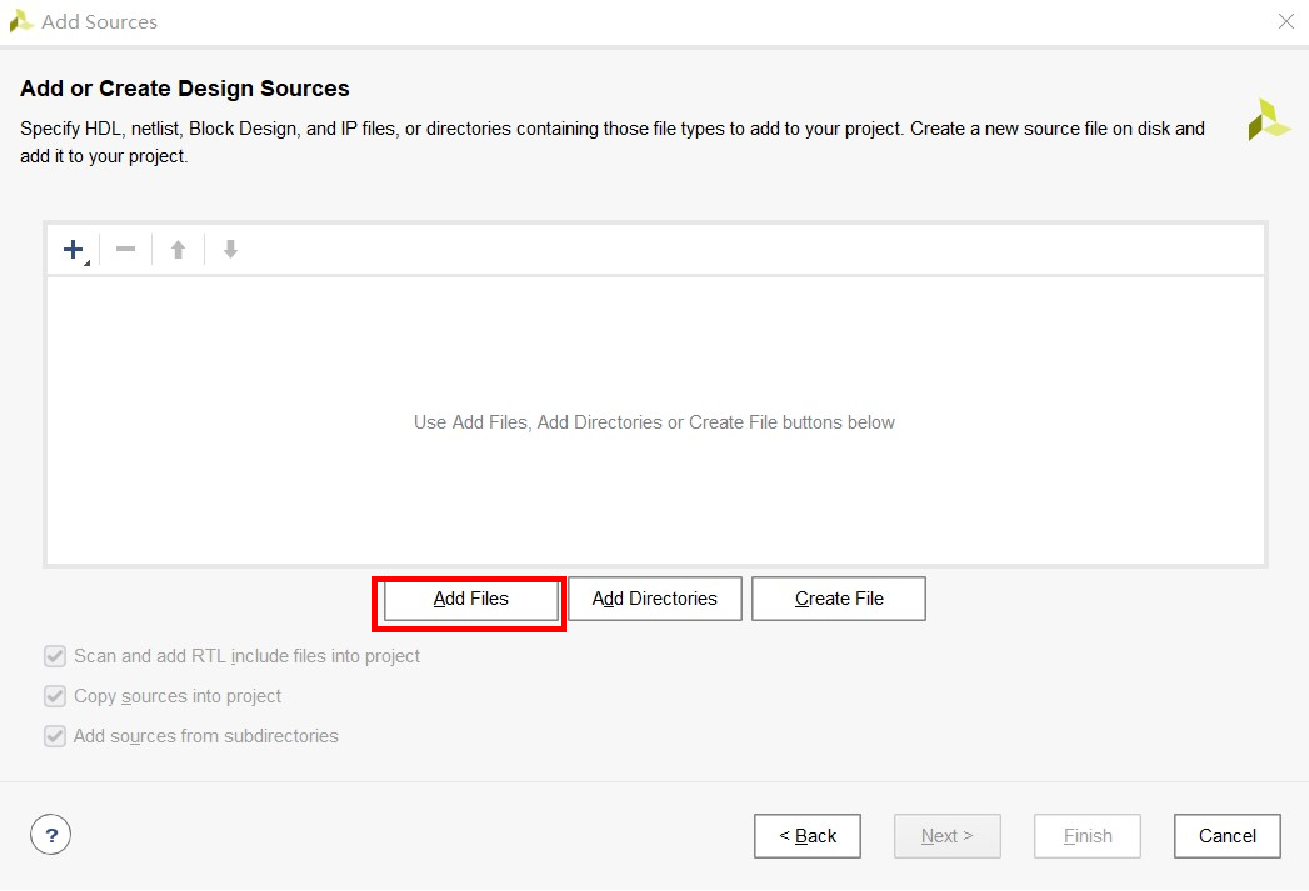

- 4.添加源文件:

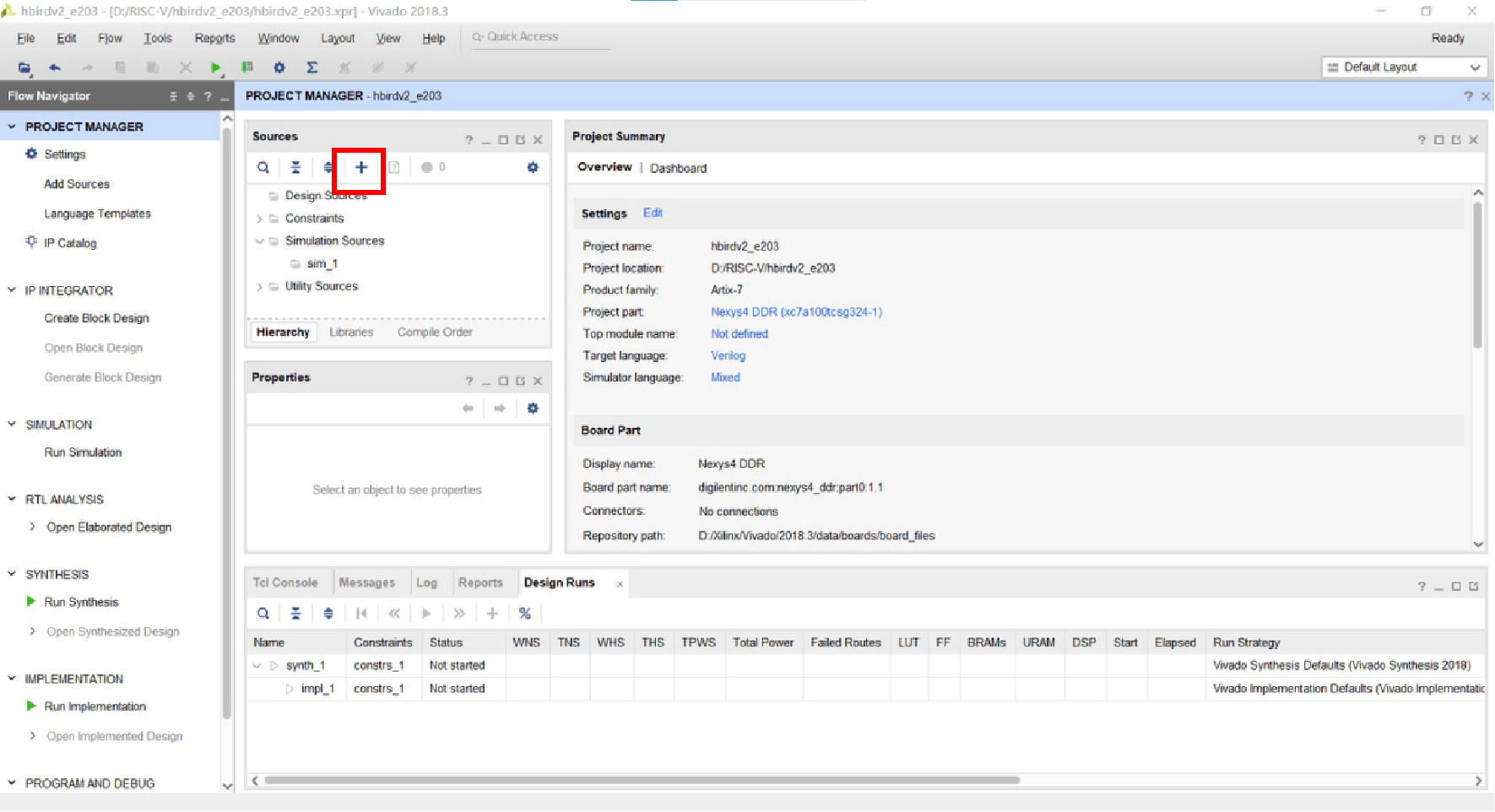

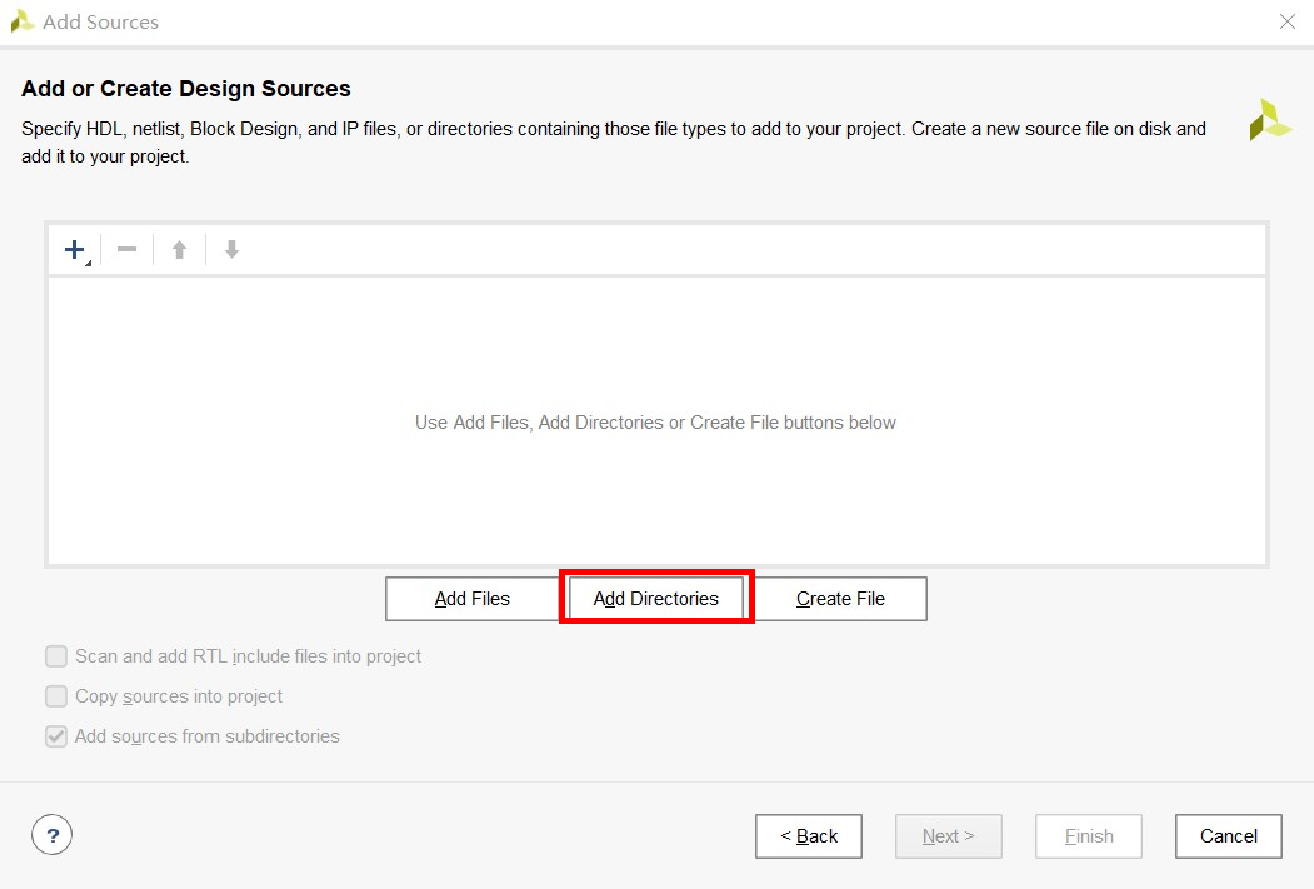

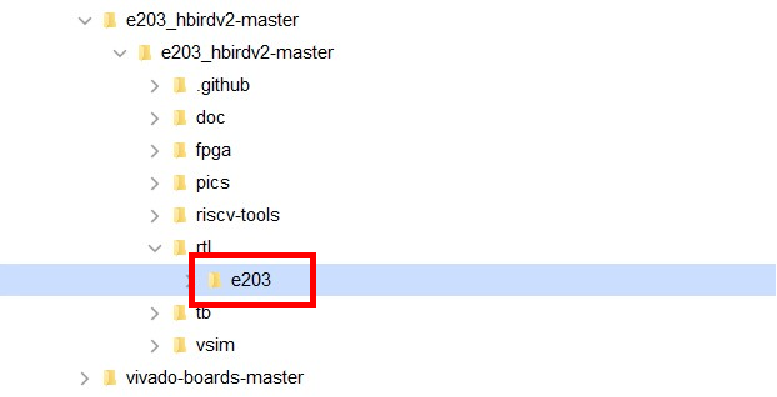

创建工程完成后,单击"+",添加从https://github.com/riscv-mcu/e203_hbirdv2下载得到的源文件,这里我们选择添加的是文件夹e203(路径为e203_hbirdv2/rtl/e203),Finish完成添加,那两个勾建议可以勾选,会将添加的源文件拷贝到我们的工程目录下,防止对原始文件造成改动;

- 5.添加头文件:

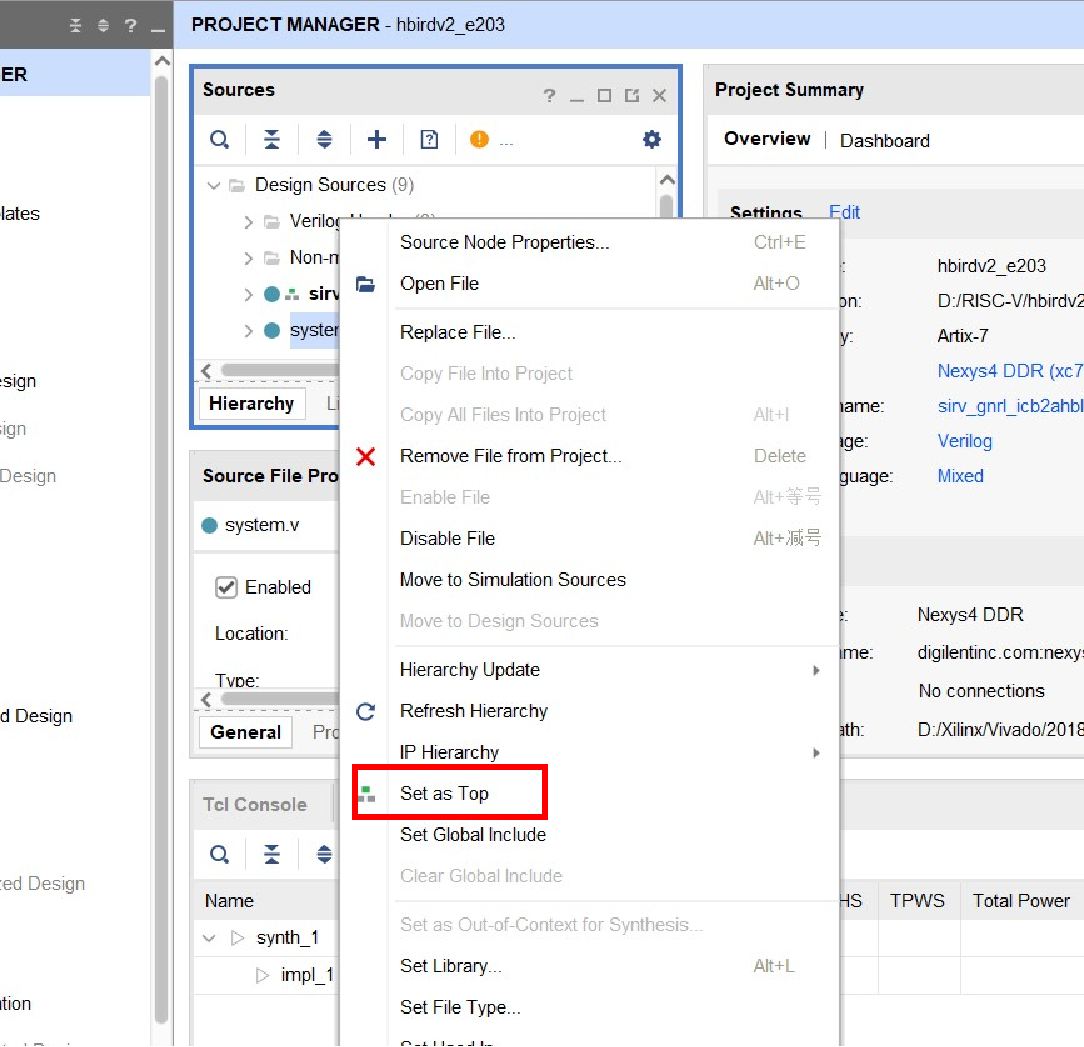

同上操作,找到MCU对应的system.v文件(路径为e203_hbirdv2-master\fpga\mcu200t\system.v);

- 6.设置头文件:

添加完成后,右键点击system.v将其设置为头文件;

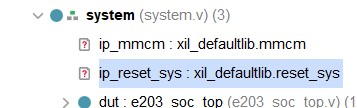

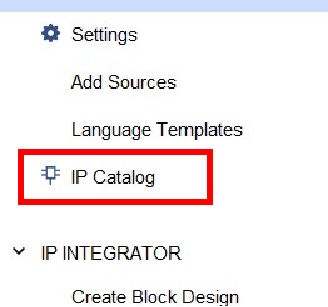

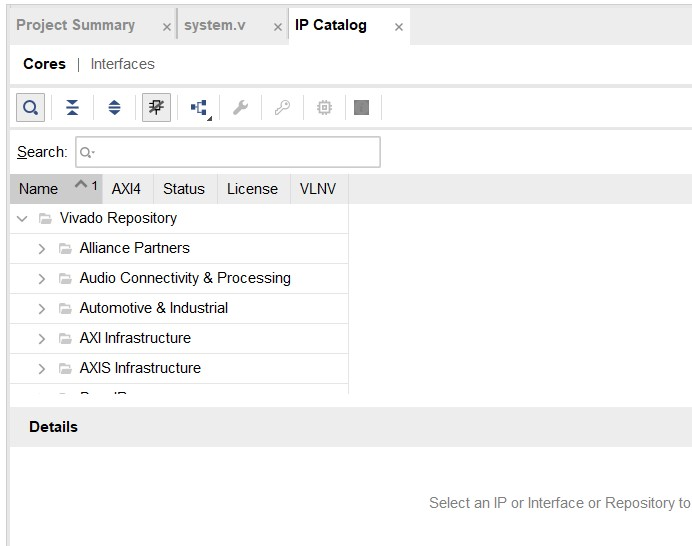

- 7.调用IP核:

这时,我们会观察到有两个文件有问题,这是由于e203中调用了相应的IP核,我们也要在工程中对应添加;

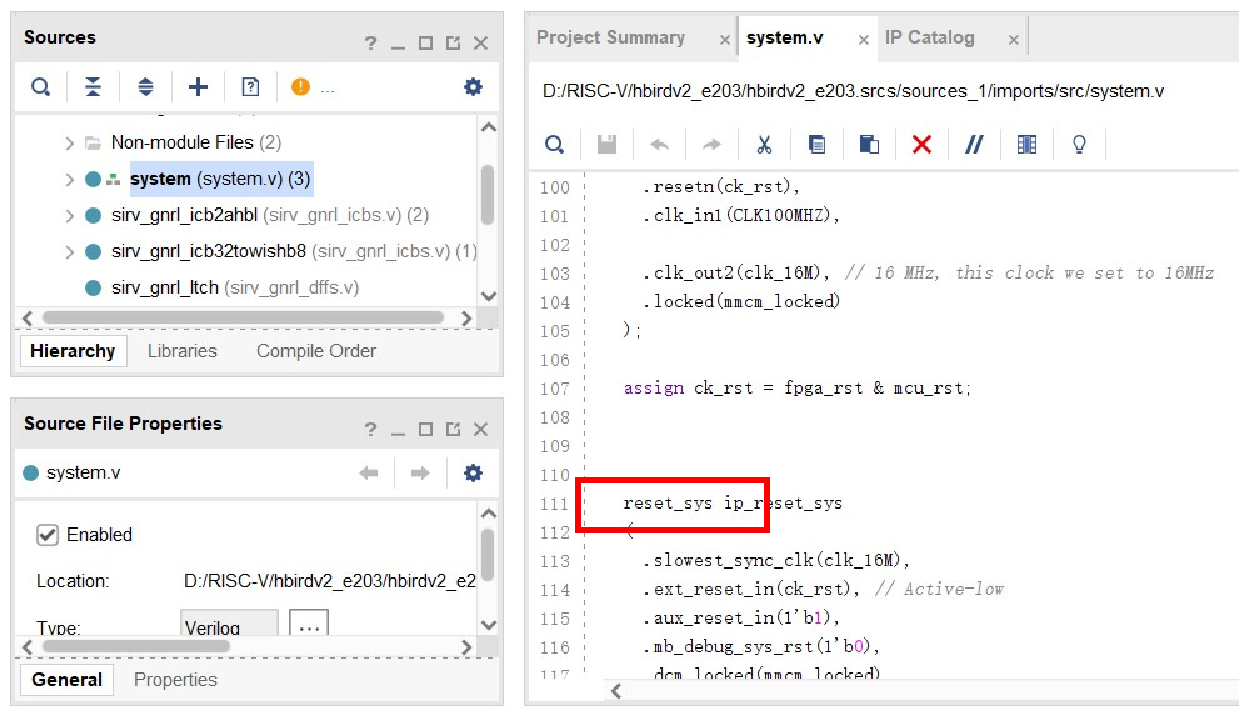

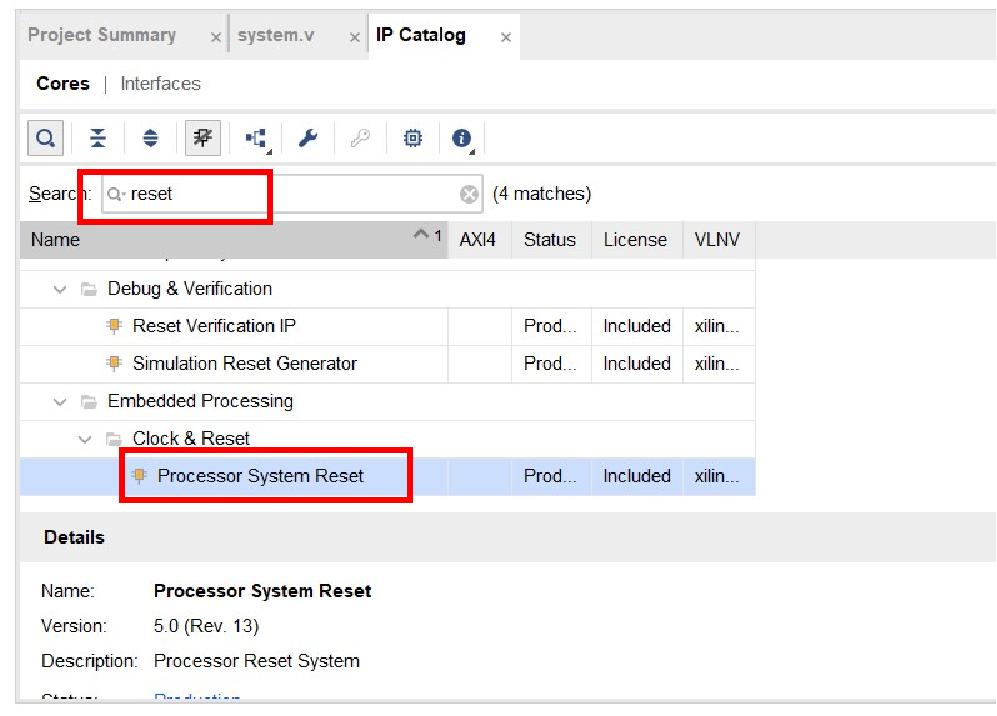

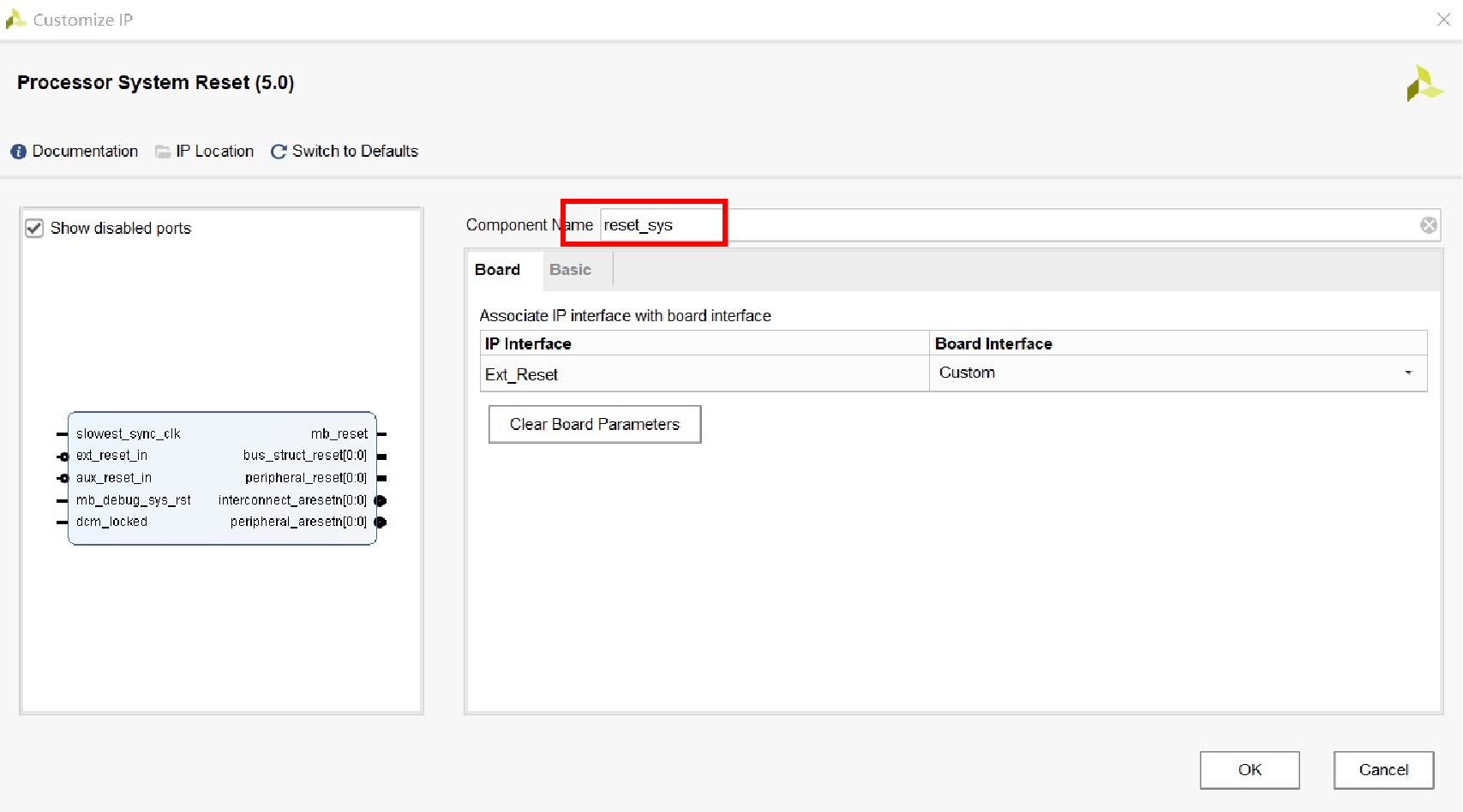

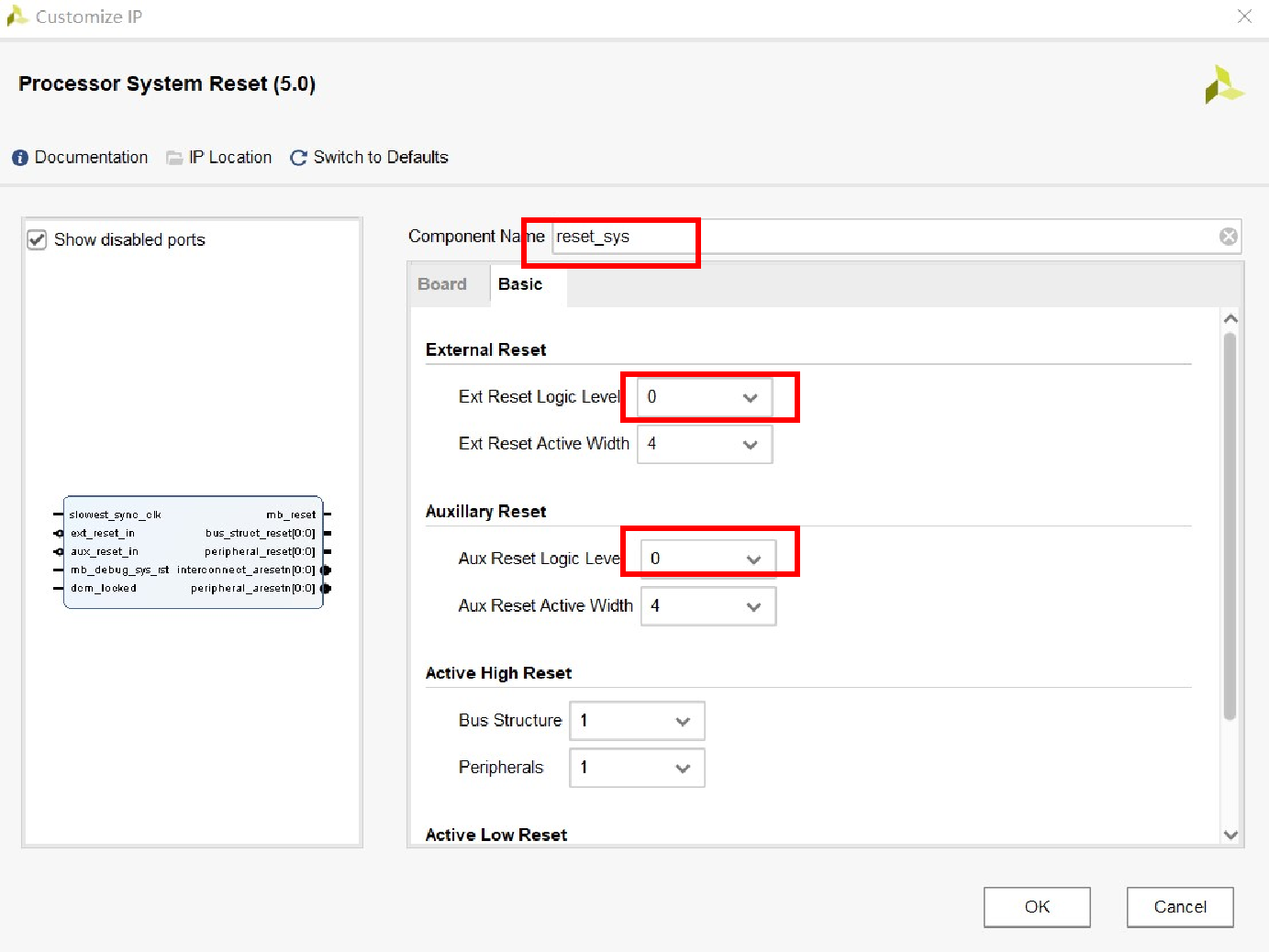

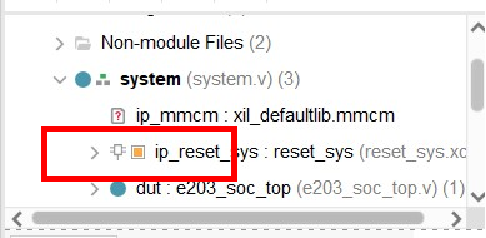

- 8.添加reset_sys:

在IP目录中找到对应IP核Processor System Reset,双击将名字改为system.v中的对应名字reset_sys。注意!这里一定要保持名称一致!后修改其复位的优先级为最高,即可完成IP核的调用;

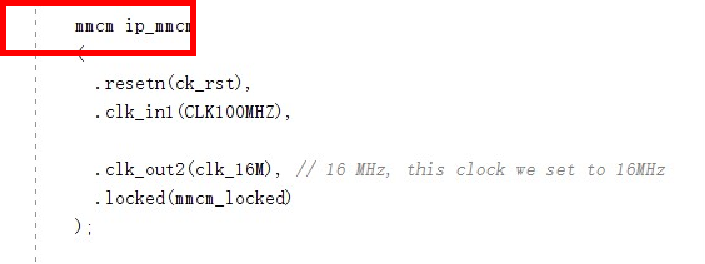

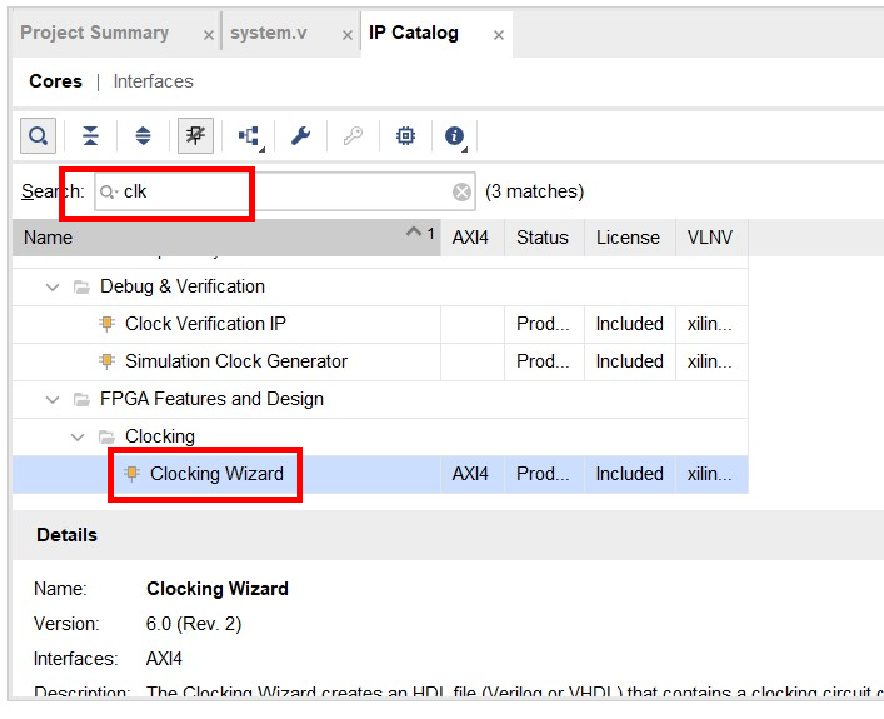

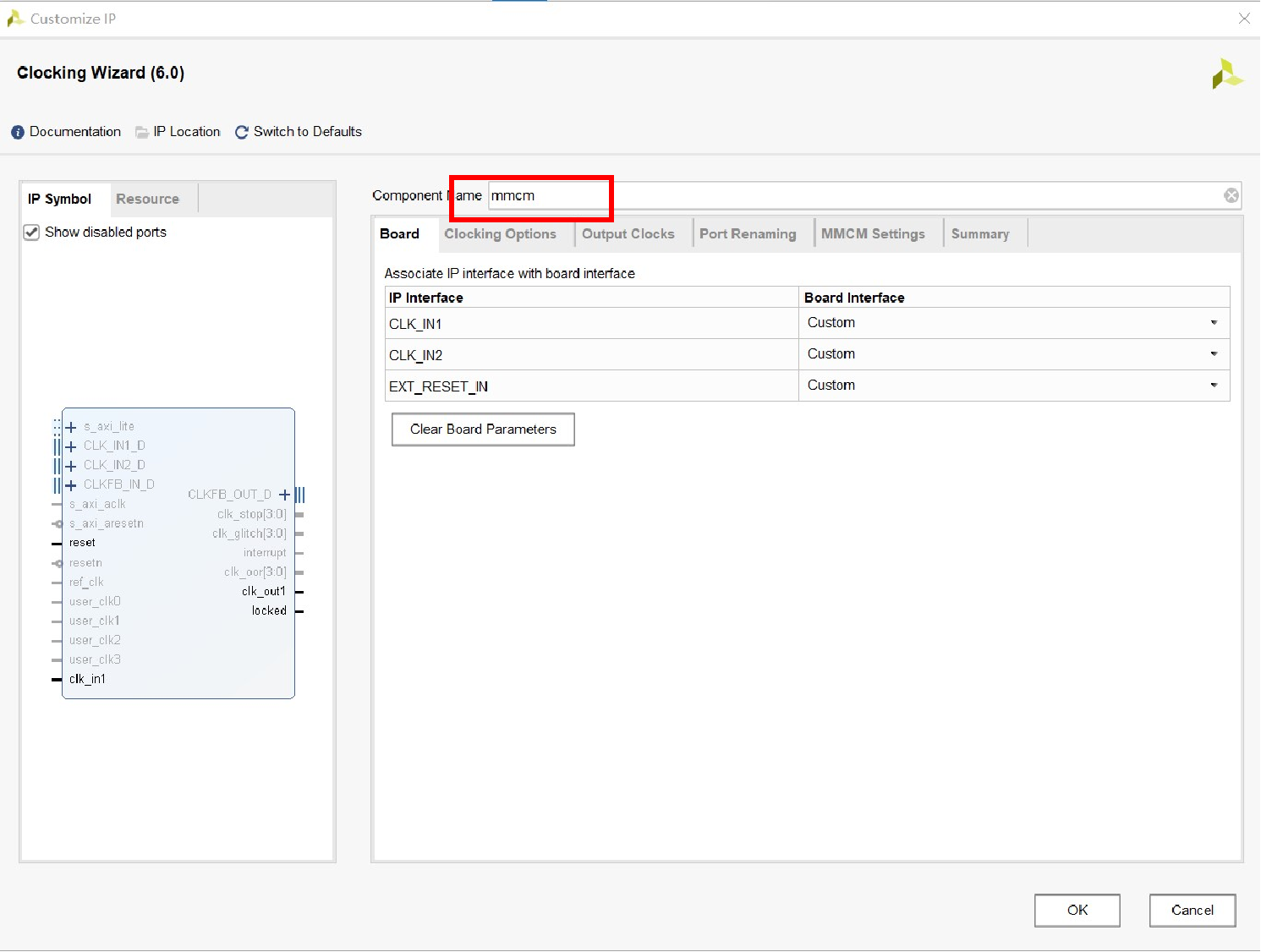

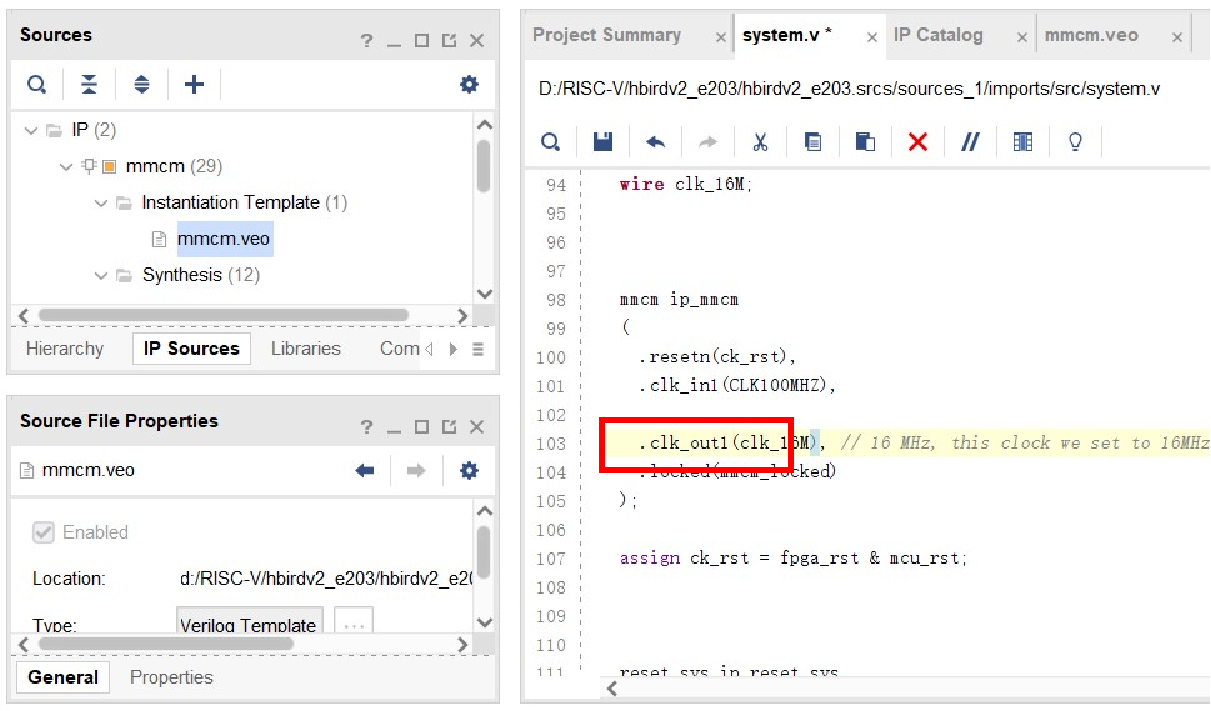

- 9.添加clk:

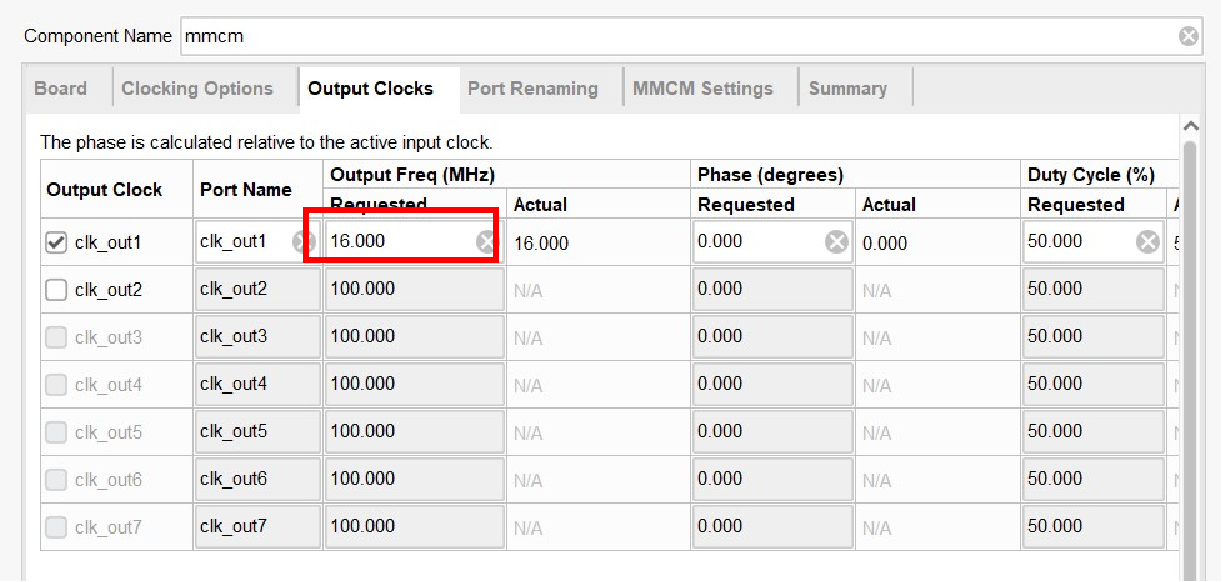

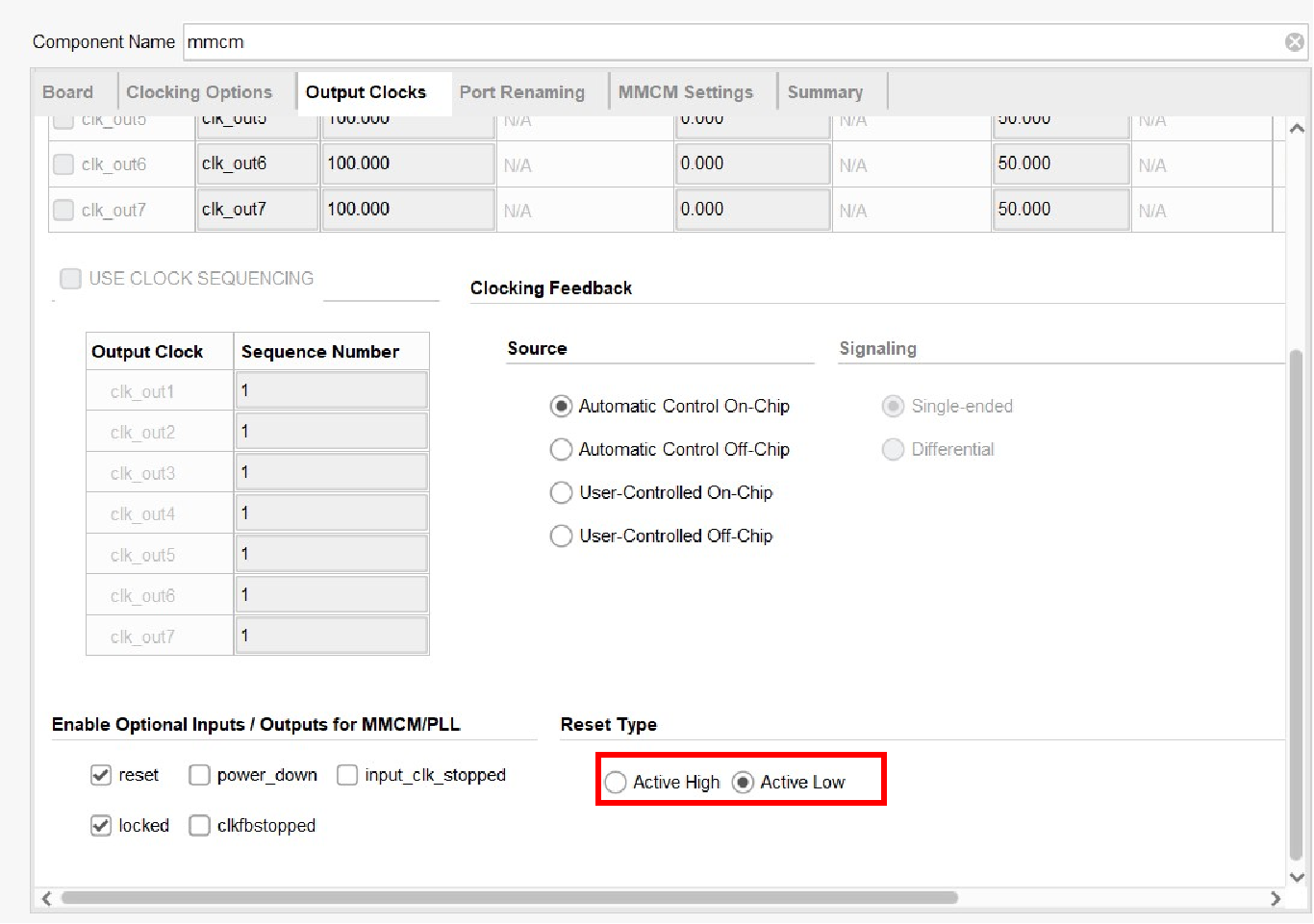

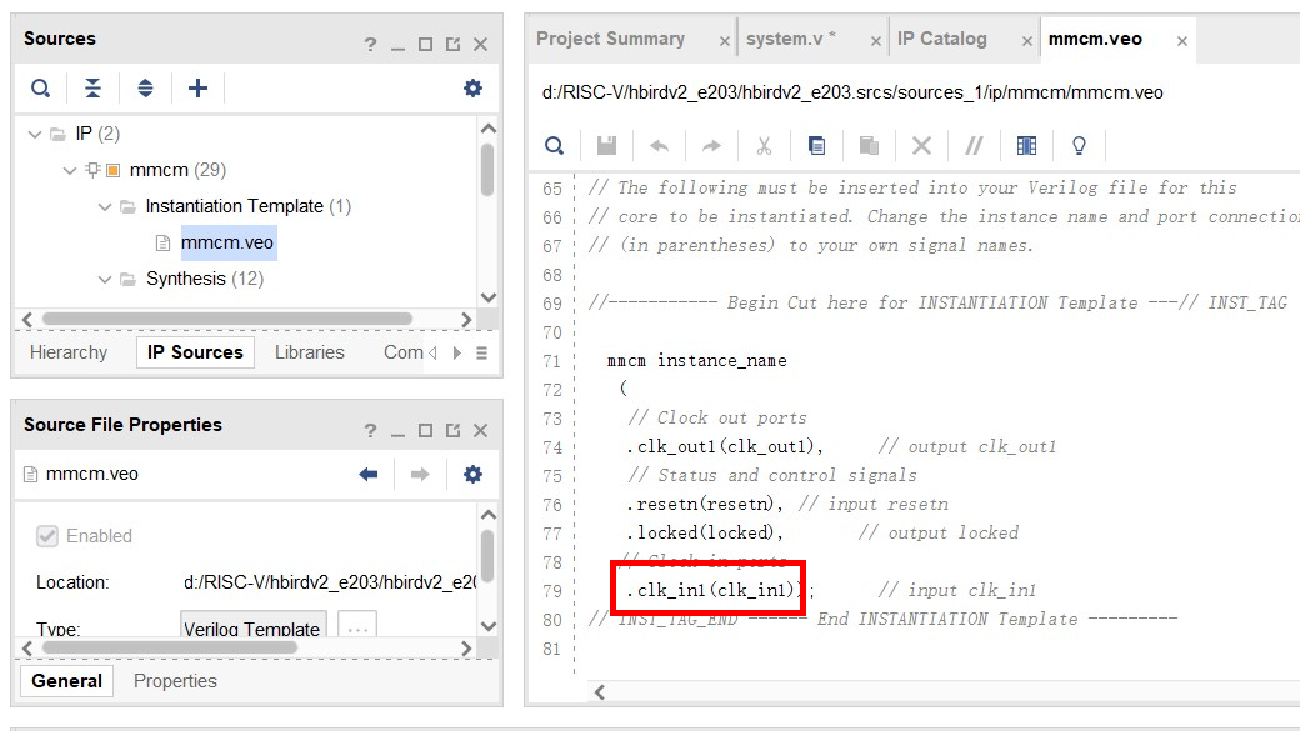

在IP目录中找到对应IP核Clocking Wizard,同上操作,将名改为mmcm,修改生成时钟频率为16M,改变复位方式为低电平复位,即可完成IP核的调用;同时应注意这里IP核调用的例化名称应与system.v中保持一致。

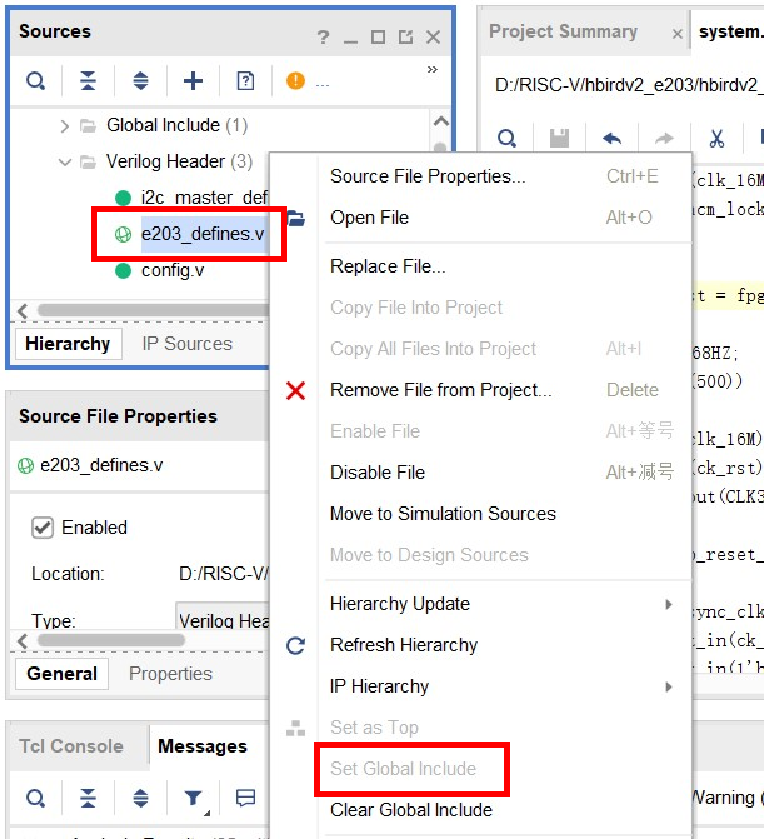

- 10.修改顶层定义文件:

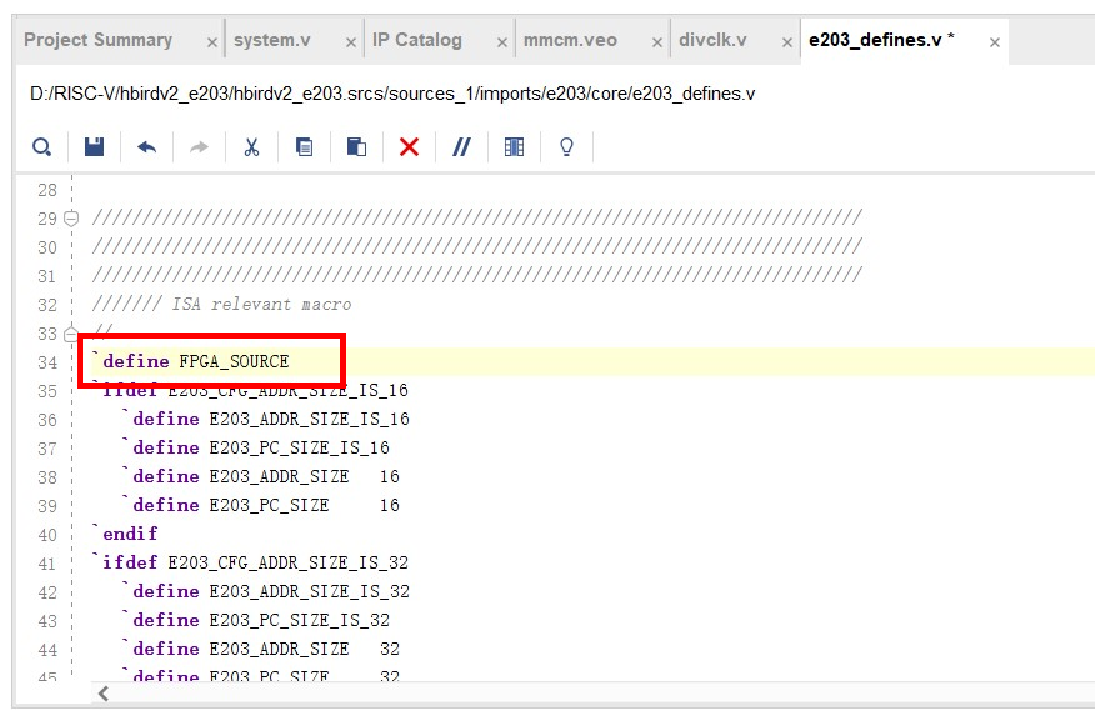

右键单击e203_defines.v,将其设为global define,并在其文件头添加语句:`define FPGA_SOURCE。完成后查看Elaborated Design,若此时报错无法打开e203_defines.v文件,可以在SourceFileProperties中将其对应文件类型改为Verilog Header

NucleiStudio创建工程

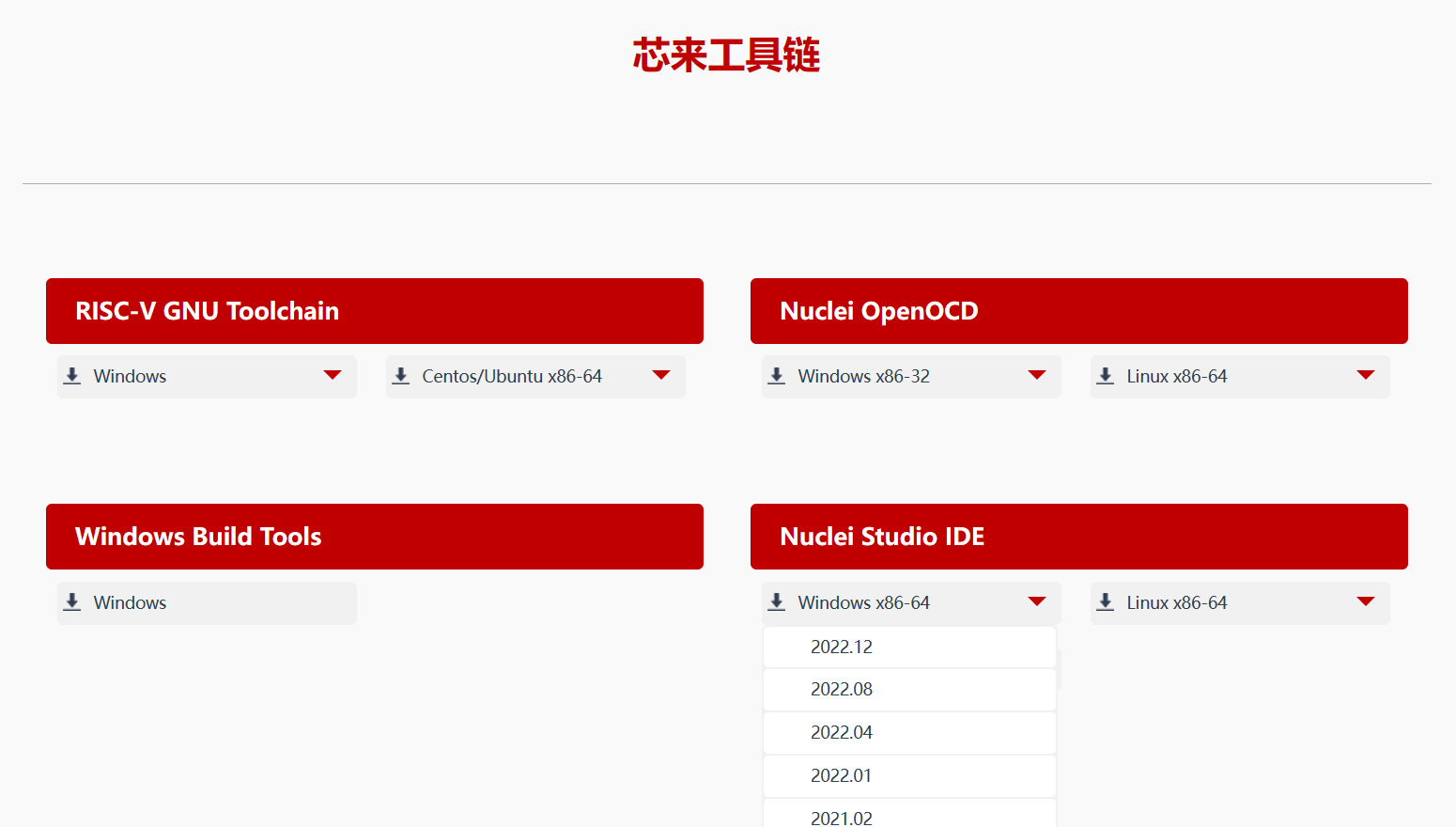

- 1.安装NucleiStudio:

- 2.配置JDK:

下载完成后,直接解压NucleiStudio压缩包,双击exe文件即可运行。如果没有成功打开,可参考以下过程进行JDK的配置:

NucleiStudio将JRE、Eclipse、GNU MCU Eclipse 插件、RISCV-V 交叉工具链、Windows Build Tools打包在了一起。所以NucleiStudio 本质上还是Eclipse,而是基于Java开发的,所以需要Java的软件开发工具包——JDK。

双击jdk-8u152-windows-x64.exe,选择安装目录,然后下一步

完成后,单击"计算机-属性-高级系统设置",单击"环境变量",新建:变量名为:JAVA_HOME,变量值为安装目录下的jdk文件夹

配置PATH,变量名:Path,变量值:%JAVA_HOME%\bin

新建CLASSPATH,变量名:CLASSPATH,变量值:.;%JAVA_HOME%\lib\dt.jar;%JAVA_HOME%\lib\tools.jar

测试是否安装成功:window+R打开cmd窗口,输入javac出现如下说明配置成功

- 3.启动NucleiStudio

启动后,会让选择workstation,找一块自己满意的地方放就行。

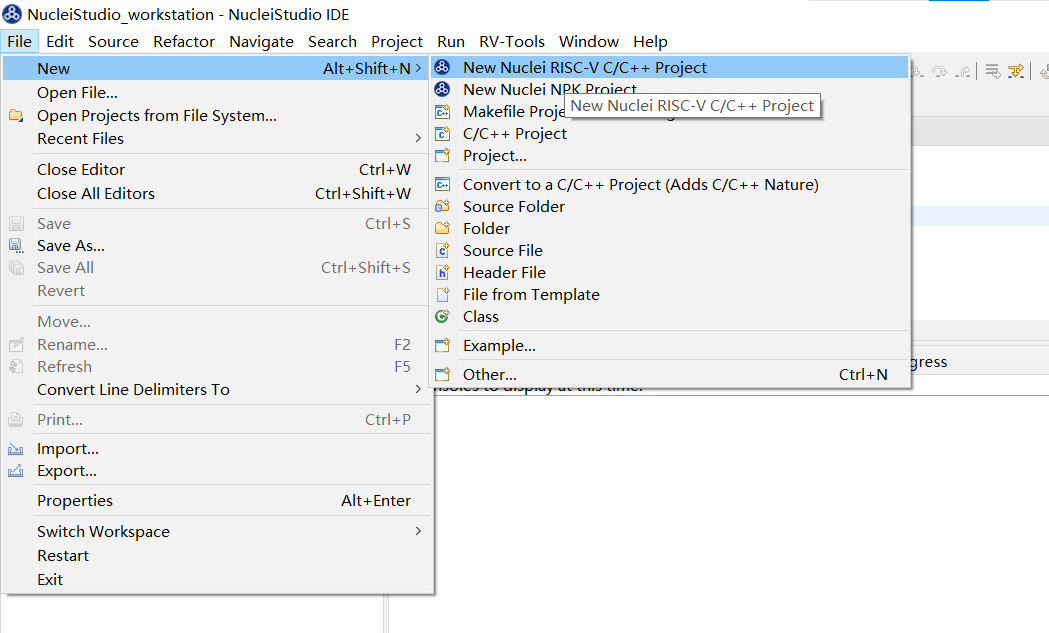

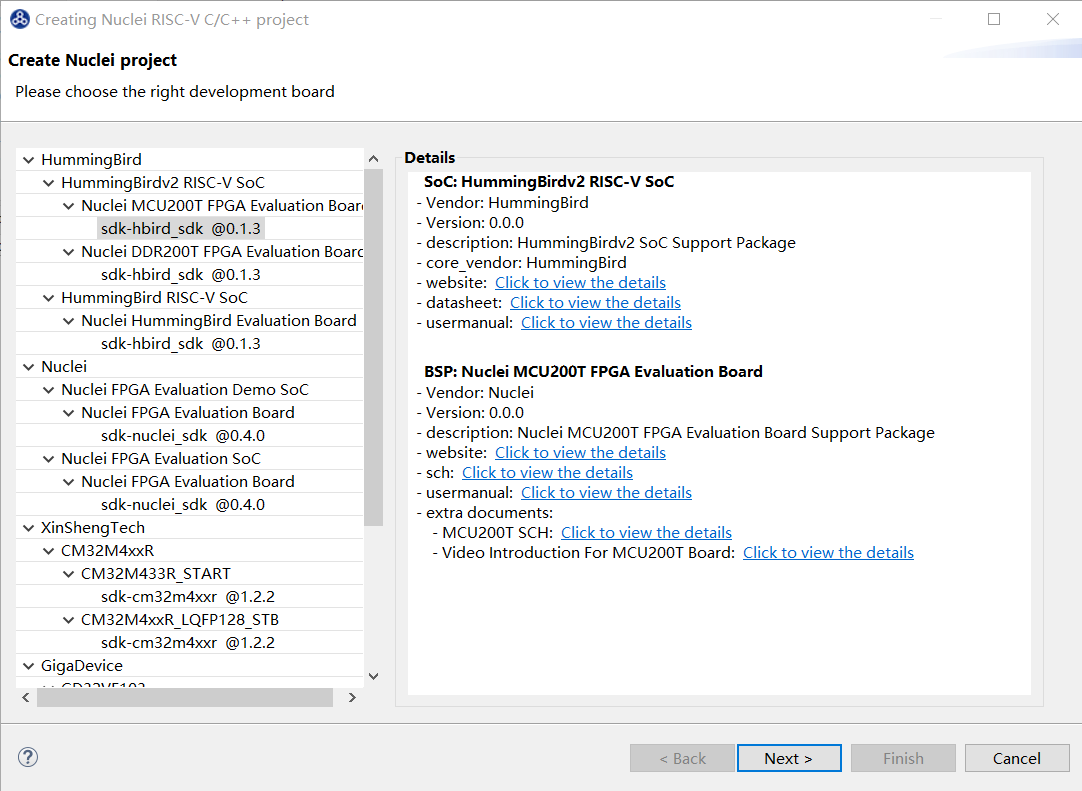

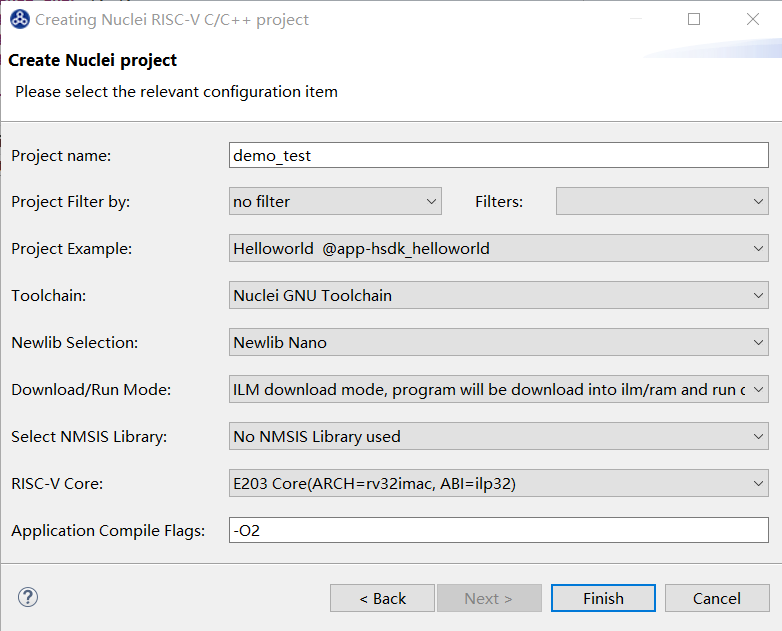

按照以下步骤新建Helloworld例程👇

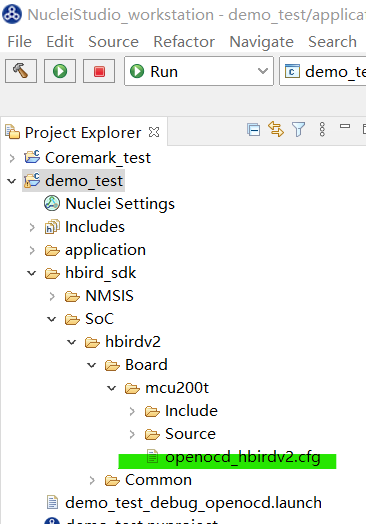

因为前面建立工程时我们选择的是ILM启动,即从内部ROM启动,故需要修改 .cfg 配置文件,位置如下👇

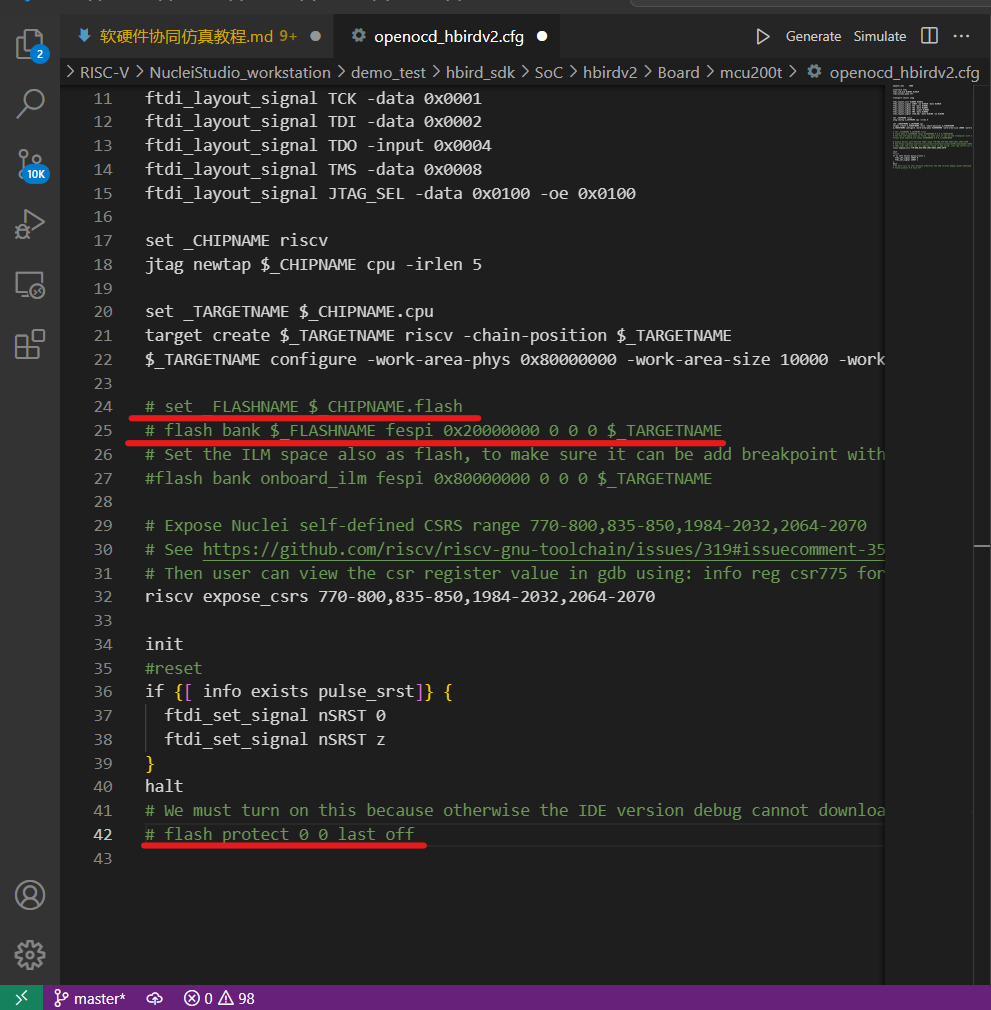

双击打开后,将划线的flash启动部分注释掉

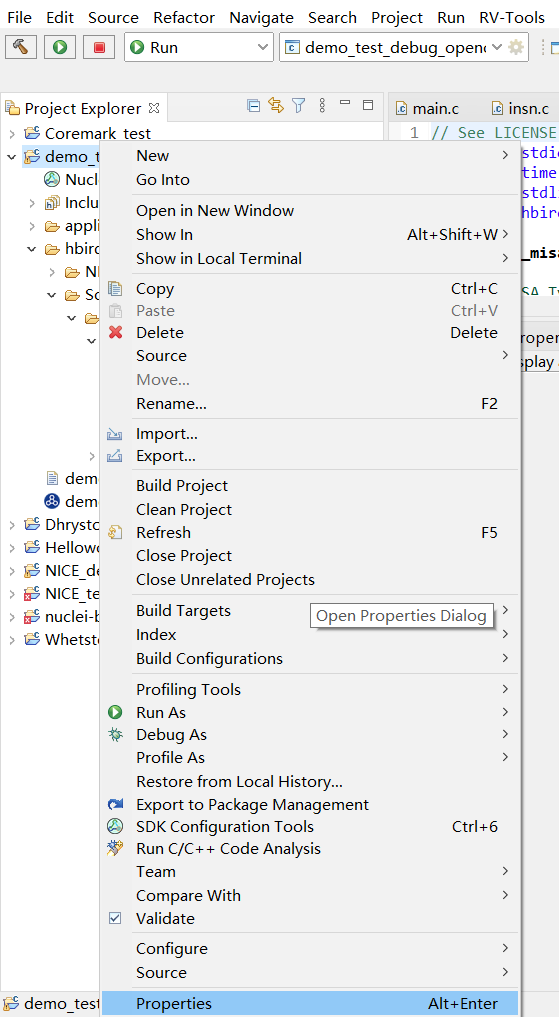

然后修改Build选项,使反汇编生成机器指令文件:右键工程,点击properties

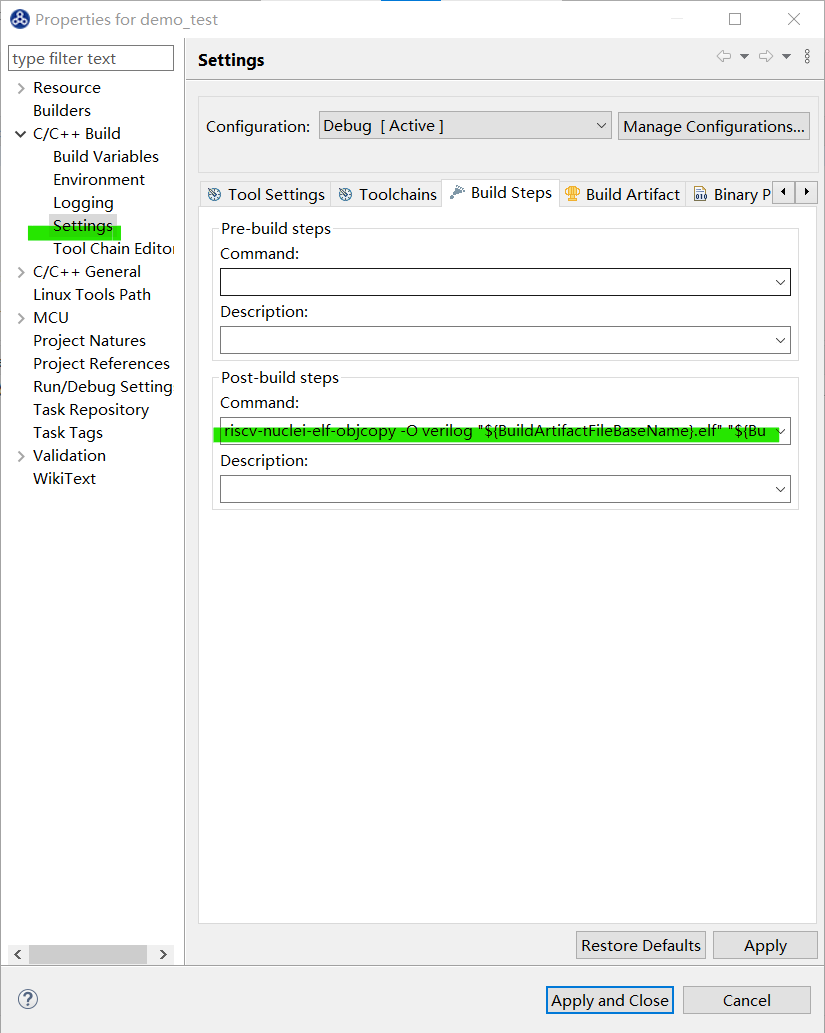

在C/C++ Build/Setting中添加如下指令:

riscv-nuclei-elf-objcopy -O verilog "${BuildArtifactFileBaseName}.elf" "${BuildArtifactFileBaseName}.verilog";sed -i 's/@800/@000/g' "${BuildArtifactFileBaseName}.verilog"; sed -i 's/@00002FB8/@00002000/g' "${BuildArtifactFileBaseName}.verilog";

最后点击锤子🔨即可编译整个工程

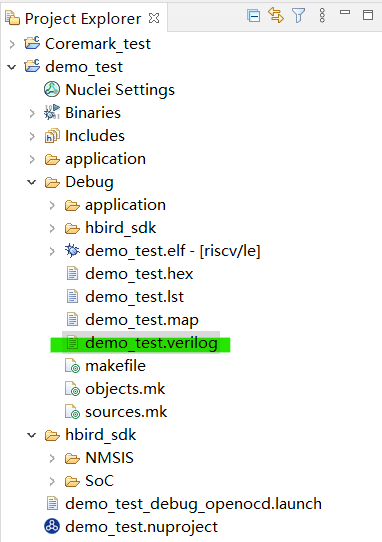

编译完成后,我们会在工程目录下发现生成了.verilog文件,此即为我们仿真需用到的文件,可以将改文件复制保存在tb目录下

联合仿真

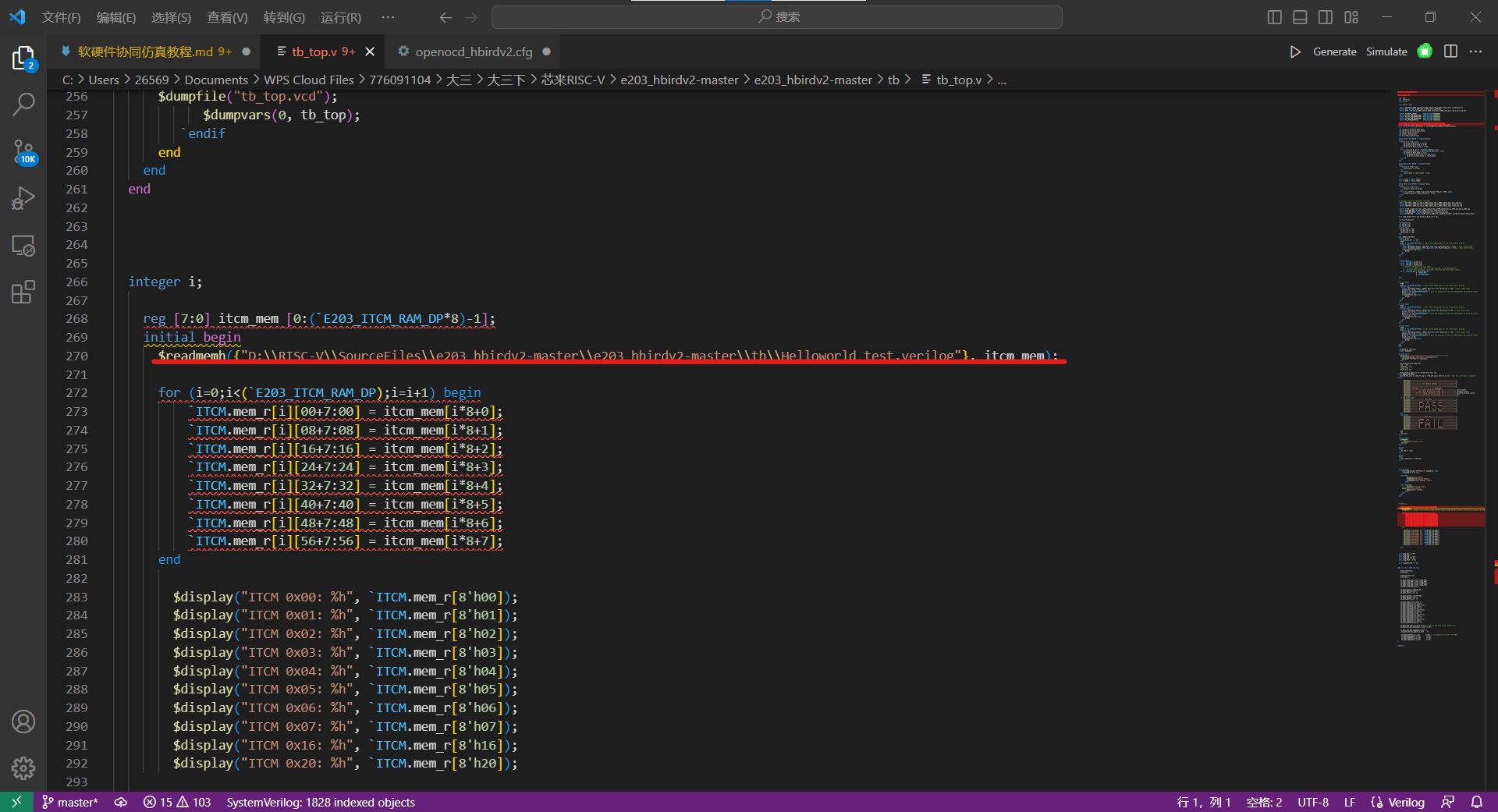

在我们前面创建的Vivado工程中添加仿真文件(e203_hbirdv2-master\e203_hbirdv2-master\tb\tb_top.v),然后修改我们要验证的仿真文件对应路径,

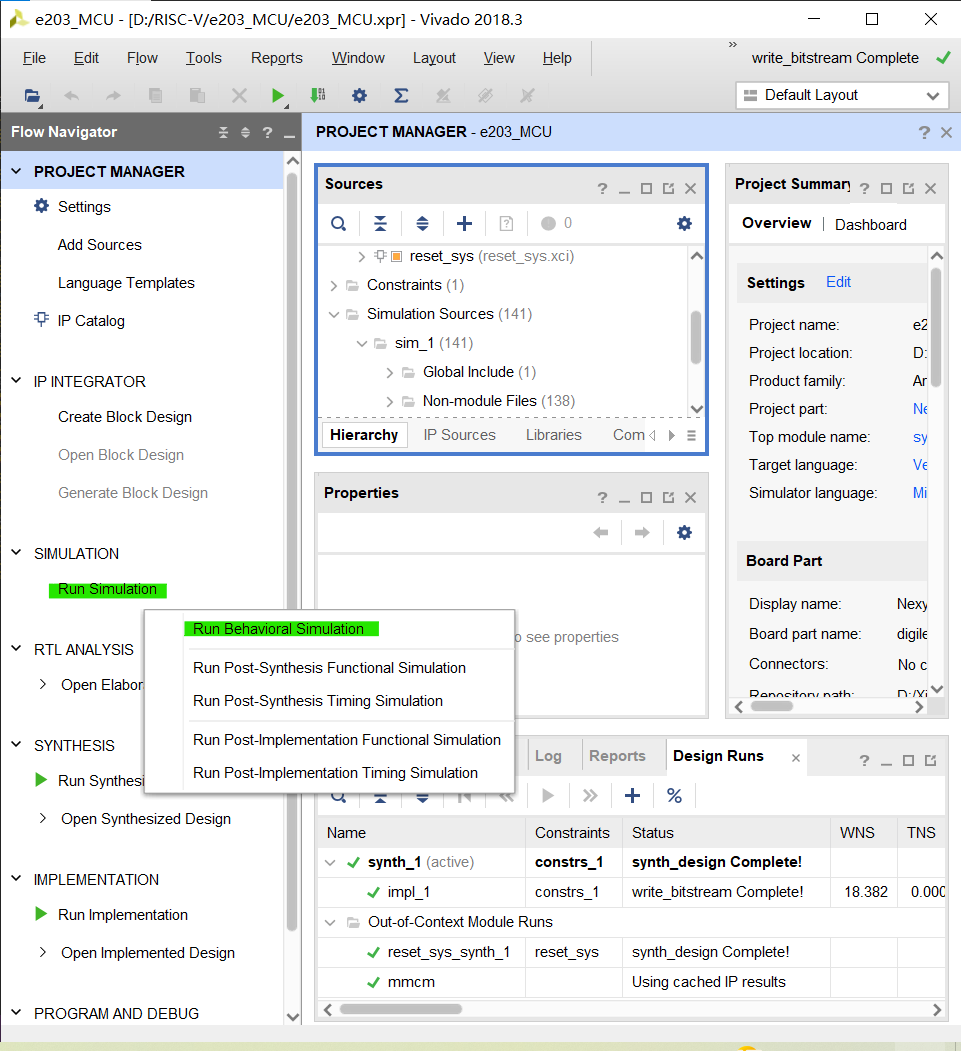

最后在Vivado中进行行为级仿真即可得到我们想要验证的结果

Nucleistudio+Vivado协同仿真教程

Nucleistudio+Vivado协同仿真教程

浙公网安备 33010602011771号

浙公网安备 33010602011771号