数电第一周总结_by_yc

数电第一周总结

重点:Verilog建模方式

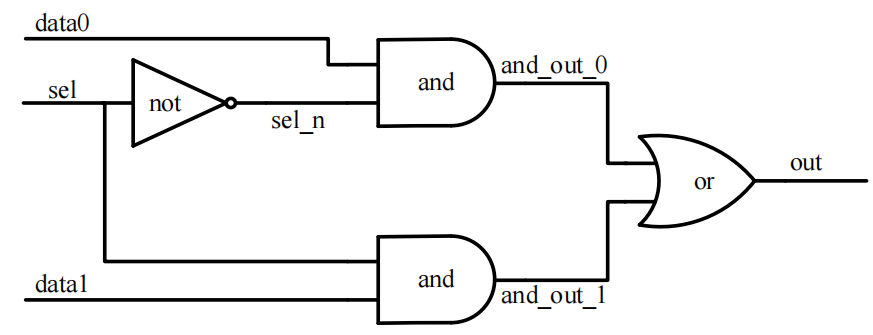

- 结构级建模: 需基于电路原理图

module mux(

input data0,

input data1,

input sel,

output out);

wire sel_n, and_out0, and_out1; //需要对所有线进行命名

not U1(sel_n, sel); //括号内变量的顺序为(输出量,输入量)

and U2(and_out0, sel_n, data0);

and U3(and_out1, sel, data1);

or U4(and_ou0, and_out1);

endmodule

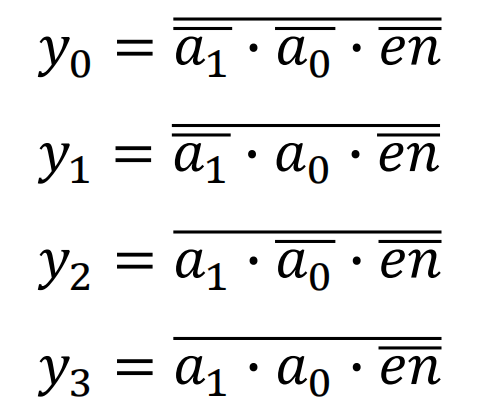

- 数据流建模: 可以根据电路原理图或代数表达式等进行电路的设计

module decoder(

input a0,

input a1,

input en

output [3:0]y); //注意数组(?)的写法

assign y[0] = ~(~a1 & ~a0 & ~en); //assign后直接接代数表达式

assign y[1] = ~(~a1 & a0 & ~en);

assign y[2] = ~(a1 & ~a0 & ~en);

assign y[3] = ~(a1 & a0 & ~en);

endmodule

- 补充:

对于综合的理解:从高级别的描述自动转换成较低级别的描述的自动化方法,即将RTL描述转化成电路原理图的过程。

数电第一周总结

数电第一周总结

浙公网安备 33010602011771号

浙公网安备 33010602011771号