Sigrity中板级TDR仿真的问题和注意事项

这几天在研究使用Sigrity/Generator仿真PCB的TDR,发现了点问题,记录之。仿真步骤,可以参考其帮助文档。

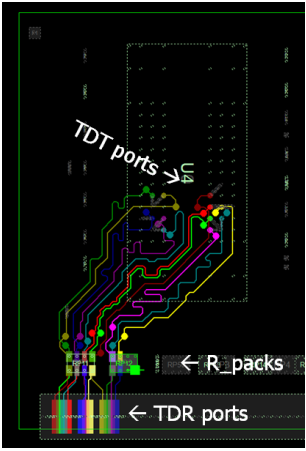

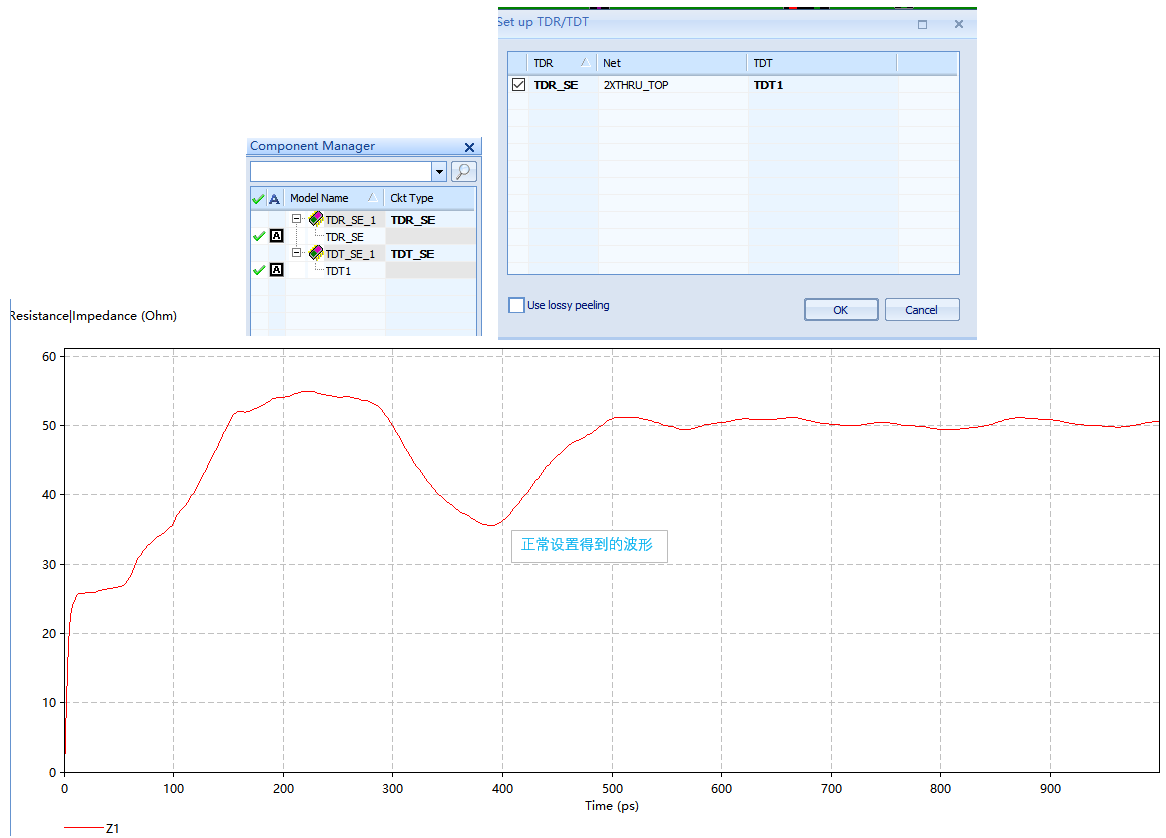

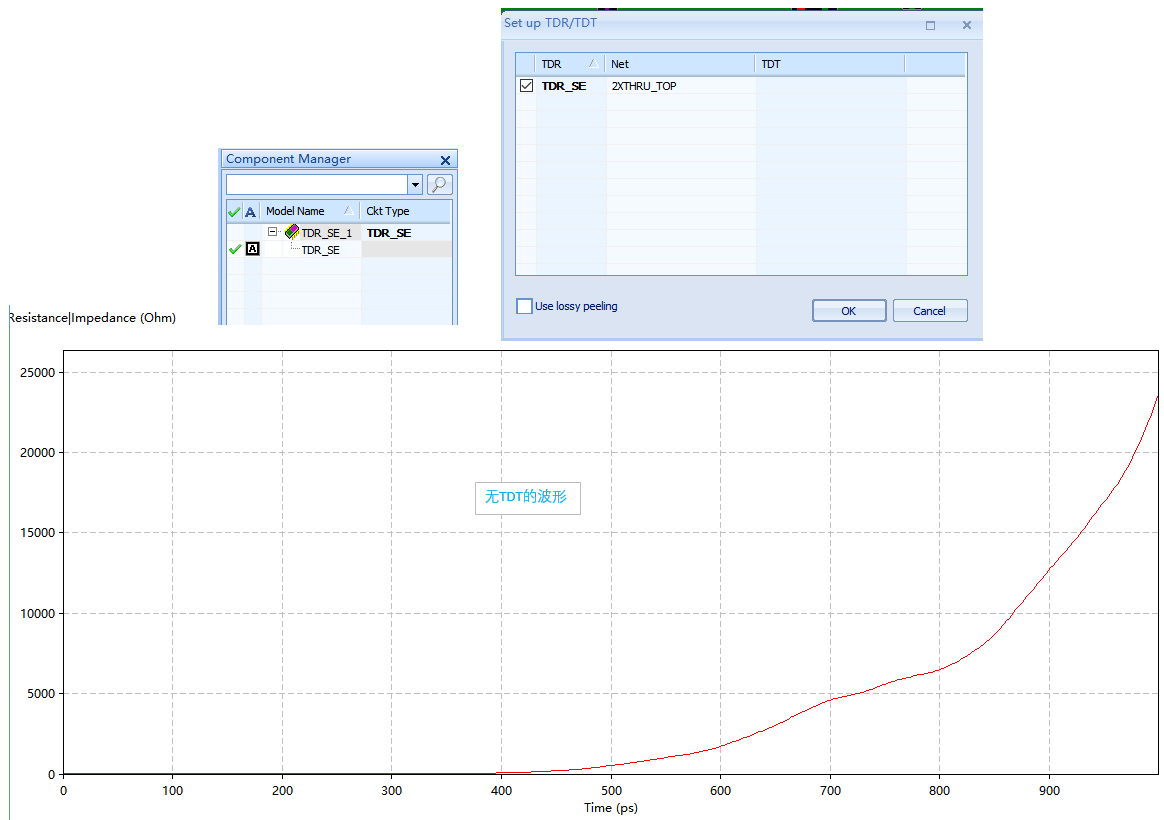

1. 想要仿真TDR必须要设置TDR和TDT,而且这两个分别位于不同的两端,不然得到的TDR波形看起来会很奇怪

2. 正常设置得到波形

3. 未设置TDT或者未加入TDT端口的波形,其实真的波形是OK的,只是仿真时间一长,后面的大阻抗,会直接将前面那一小段50Ω曲线显示看起来接近0Ω

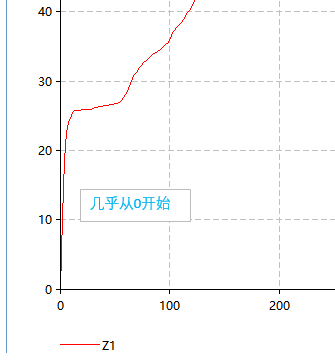

4. 即使正常的波形,看起来也有奇怪,为什么前面有一段是几乎从0开始的?如果真要参考,这一段要舍弃才行

浙公网安备 33010602011771号

浙公网安备 33010602011771号