多个电容并联阻抗峰值

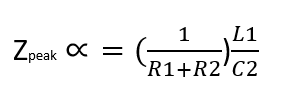

最近在看《PDN设计之电源完整性》一书,发现第五章5.5节处的内容挺违反直觉的,公式如下

R1-----------电容1的ESR

R2-----------电容2的ESR

L1------------电容1的ESL

C2------------电容2容值

从公式来看,增加电容的ESR,可以减少并联电容的并联谐振峰值阻抗!减少ESL,增加C2容值也是能减低并联峰值阻抗,但是增加ESR跟我一直来的直觉相反!并且书中提到,两个电容值在0.5~2倍之间,峰值阻抗下降很快,很多关于硬件的资料中,在增加去耦电容以10倍的间距增加电容,从此书中的曲线来看,0.5~2倍间的容值更好!

书中节尾也给出了3中减低并联谐振峰值的方法,如下:

1. 让两个电容值接近

2. 降低每个电容的ESL

3. 提高每个RLC电容的ESR,即每个电容的ESR