【FPGA】顺序语句

顺序语句概述

特点:执行顺序和书写顺序基本一致

出现的位置:只能出现在进程和子程序中,子程序包括函数(function)和过程(procedure)

顺序语句种类

-

顺序信号/变量赋值语句

-

IF-THEN 语句

-

CASE 语句

-

LOOP 语句

-

RETURN语句

-

NULL语句

顺序信号/变量赋值语句

进程中的顺序信号赋值语句:

signal<=expression;

End process时更新多次赋值,以最后一次赋值为准

进程中的顺序变量赋值语句:

variable:= expression; 立刻更新 多次赋值,以最后一次赋值为准

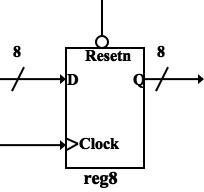

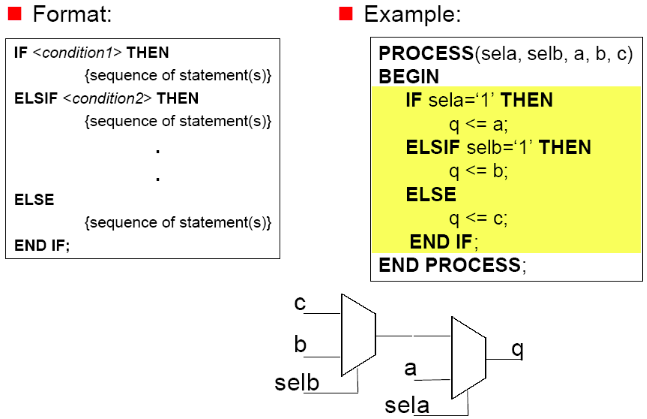

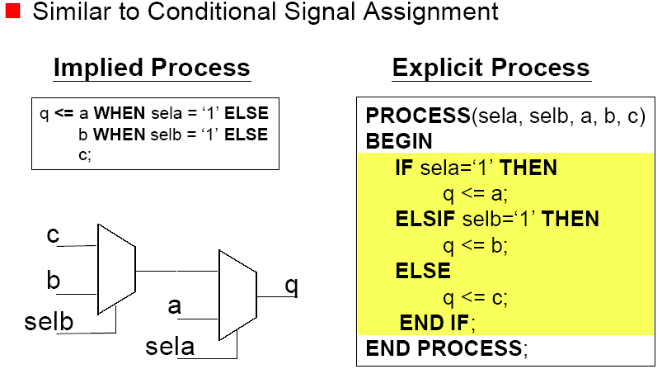

IF-THEN 语句

从上到下按照顺序评估条件 存在优先级

若第一个条件满足,可以执行对应的顺序语句。其他的都不再执行。

如果所有的条件都不满足,将执行ELSE之内的语句。 可以嵌套使用。

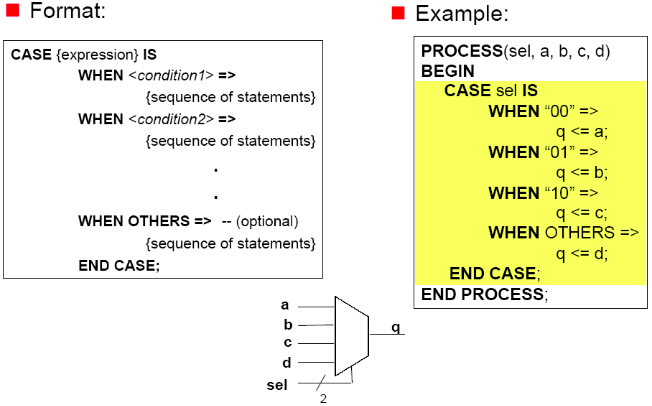

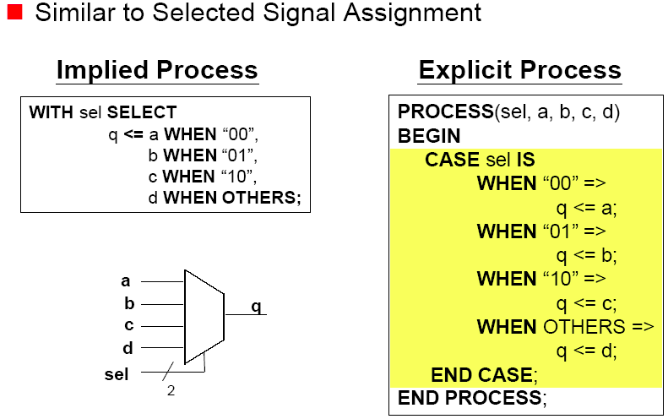

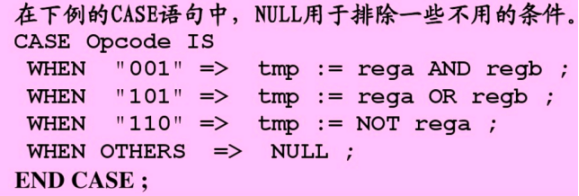

CASE 语句

条件只被评估一次 没有优先级 ;

必须包括所有的条件(可以没有when others,但是必须包含所有条件)

WHEN OTHERS 语句包括了没有指定的所有条件

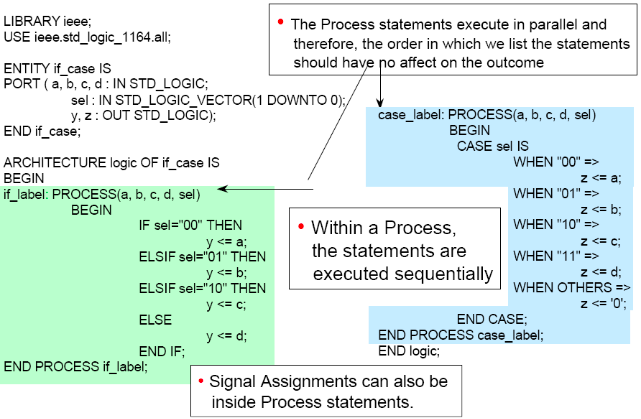

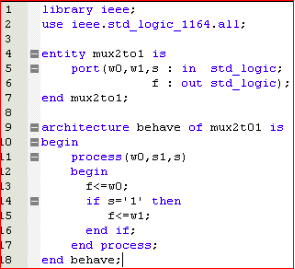

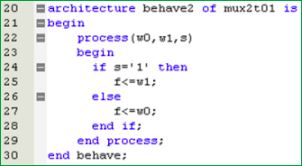

IF语句和CASE语句之例

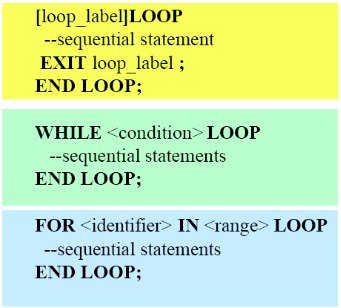

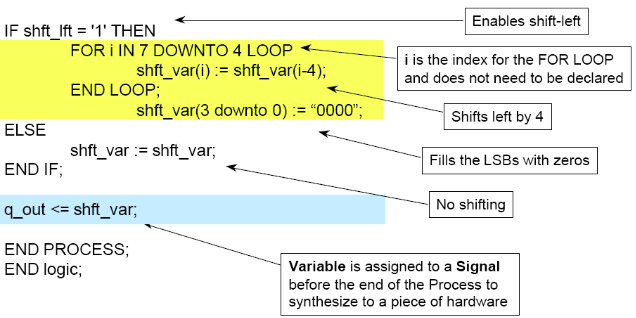

LOOP语句

无限 Loop Loop = while(True)

将无限执行,

除非EXIT 语句存在

WHILE LOOP = if( *** ){ while(True) }

条件满足,则循环

FOR LOOP = for( *** ; *** ; *** );

迭代 loop

Format:

注意:

VHDL综合器不支持无法事先确定循环次数的LOOP语句。因此,无限loop,while loop循环语句不可综合。

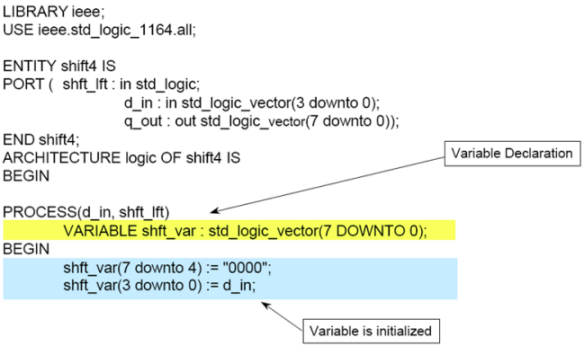

4-bit Left Shifter

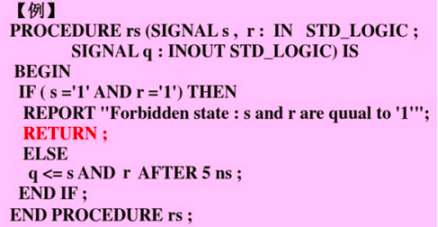

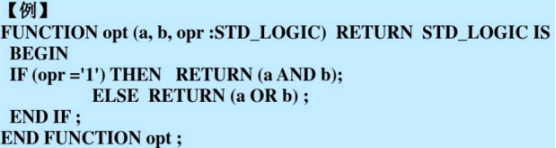

RETURN语句

Return语句是一段子程序结束后,返回主程序的语句

格式

Return;--只能用于过程,它后面不要有表达式

Return 表达式;--只用于函数,它后面必须有表 达式,函数结束必须用return语句

NULL语句

空操作

格式 NULL;

顺序语句总结

在一个进程中,可以有多个语句,需要考虑的问题

-

当敏感表中的信号发生变化, 此进程将被激活

-

一旦被激活,在进程中的所有语句都将顺序执行一次

-

进程中对信号的任何赋值在进程之外是不可见的,直到进程执行结束,才会更新信号

-

如果有多个语句对同一个信号赋值,只有最后一个是可见的,或有效的

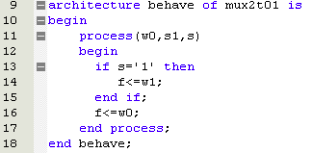

讨论Signal赋值语句

(注意:图1,图3,敏感表里中间的s1应改成w1)

Conditon1: f<= w0;

该赋值语句直到进程结束才会执行 若之后有另外的赋值给f,那么默认赋值将会被重写

Conditon2:

if statement 只会执行其中一种情况,f不会被重写

Conditon3 :

首先评估if语句,然后对f赋值 最后的结果是f始终为w0,多次赋值以最后一次为准

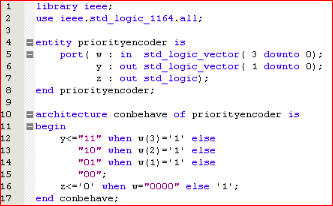

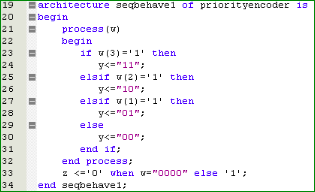

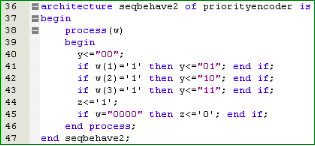

优先级编码器(3种写法)

when语句

if... elsif .... else 语句:

if 语句:

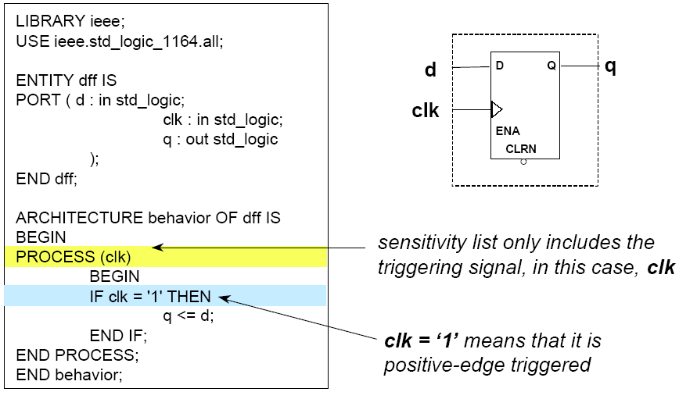

D触发器(clk=‘1’)

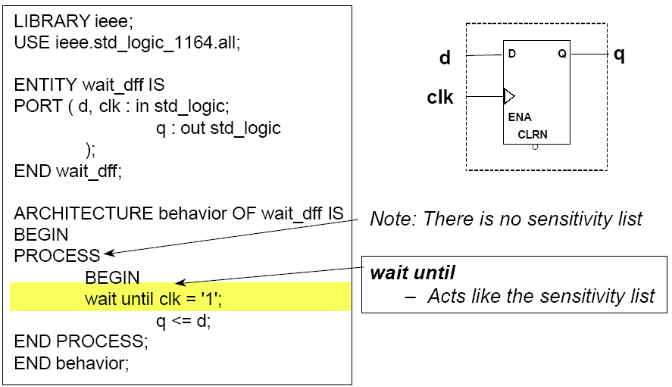

D触发器- “WAIT”

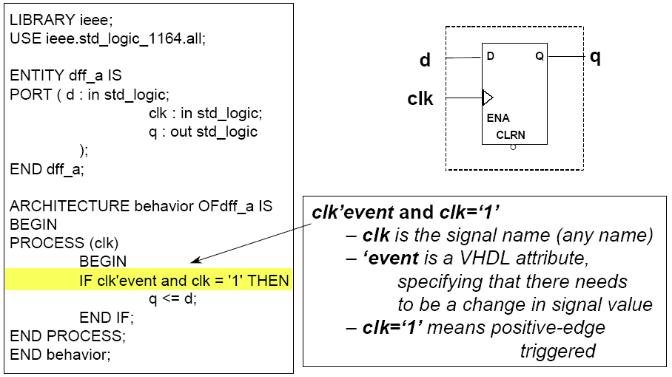

D 触发器(CLK )

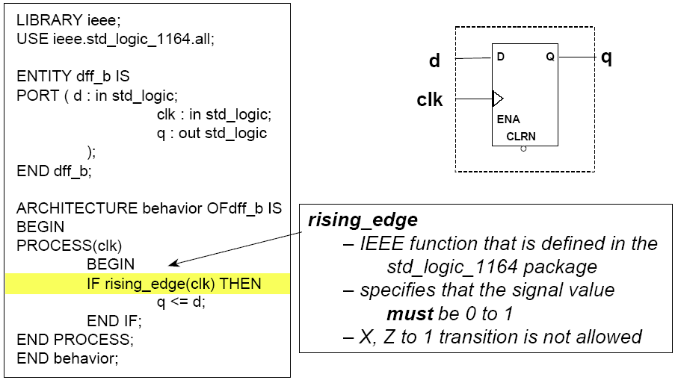

D触发器(上升沿)

注意:rising_edge(clk) 里面clk必须是std_logic;这个是函数本身设置的.

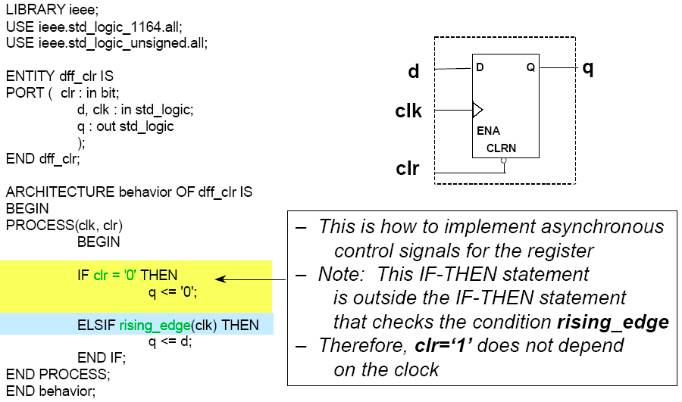

同步和异步

异步 放置在上升沿描述语句之前

同步 放置在上升沿描述语句之后

D触发器异步清零

D触发器同步清零

LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY flipflop_ar IS PORT ( D, Resetn, Clock : IN STD_LOGIC ; Q : OUT STD_LOGIC) ; END flipflop_ar ; ARCHITECTURE behavioral OF flipflop_ar IS BEGIN PROCESS ( Resetn, Clock ) BEGIN IF rising_edge(Clock) THEN IF Resetn = '0' THEN Q <= '0' ; ELSE Q <= D ; END IF ; ENDIF; END PROCESS ; END behavioral ;

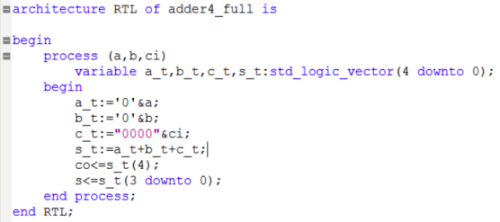

使用异步reset的8-bit寄存器

LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY reg8 IS PORT ( D : IN STD_LOGIC_VECTOR(7 DOWNTO 0) ; Resetn, Clock : IN STD_LOGIC ; Q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ) ; END reg8 ; ARCHITECTURE behavioral OF reg8 IS BEGIN PROCESS ( Resetn, Clock ) BEGIN IF Resetn = '0' THEN Q <= "00000000" ; ELSIF rising_edge(Clock) THEN Q <= D ; END IF ; END PROCESS ; END behavioral ;`

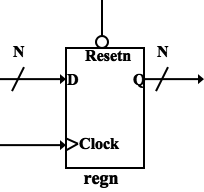

使用异步reset的N-bit寄存器

LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY regn IS GENERIC ( N : INTEGER := 16 ) ; PORT ( D : IN STD_LOGIC_VECTOR(N-1 DOWNTO 0) ; Resetn, Clock : IN STD_LOGIC ; Q : OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0) ) ; END regn ; ARCHITECTURE behavioral OF regn IS BEGIN PROCESS ( Resetn, Clock ) BEGIN IF Resetn = '0' THEN Q <= (OTHERS => '0') ; ELSIF rising_edge(Clock) THEN Q <= D ; END IF ; END PROCESS ; END behavioral ;

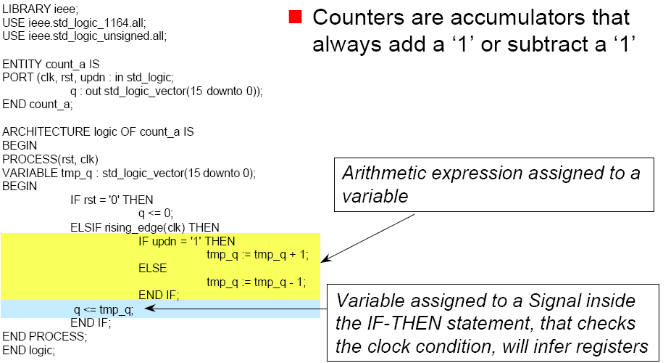

使用变量的计数器

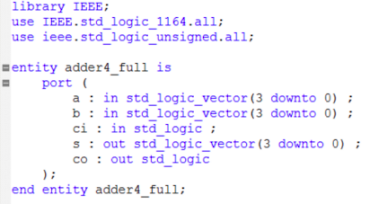

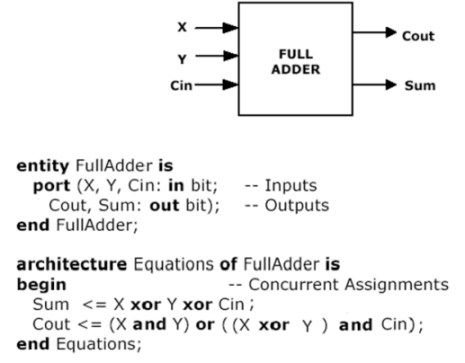

全加器-数据流描述

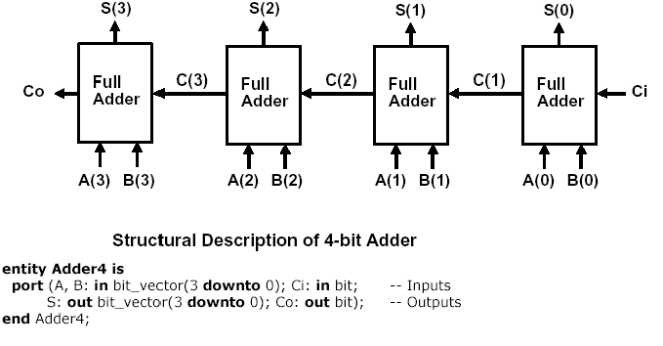

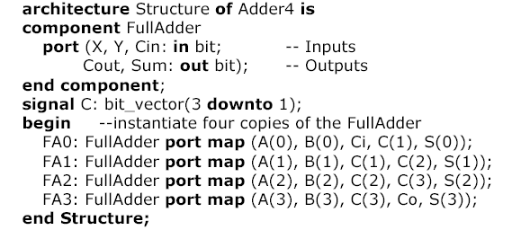

4-bit 进位加法器

结构化描述

行为描述