使用Verdi理解RTL design

使用Verdi理解RTL design

接触到一些RTL代码,在阅读与深入理解的过程中的一些思考记录

协议与设计框图

认真反复阅读理解相关协议与设计框图,一个design的设计文档中,设计框图展示了这个设计的核心框架,包括协议的整体框架、作者的设计思路和design的组成结构等。

- 1.根据协议理解设计框图

- 2.根据设计框图理解module

- 3.根据设计框图初步追踪输入输出关键信号

理解Schematic及module间的关系

结合设计框图,使用Verdi的Schematic功能,整体理清各个module间的连接关系,各个module的数据交互关系。

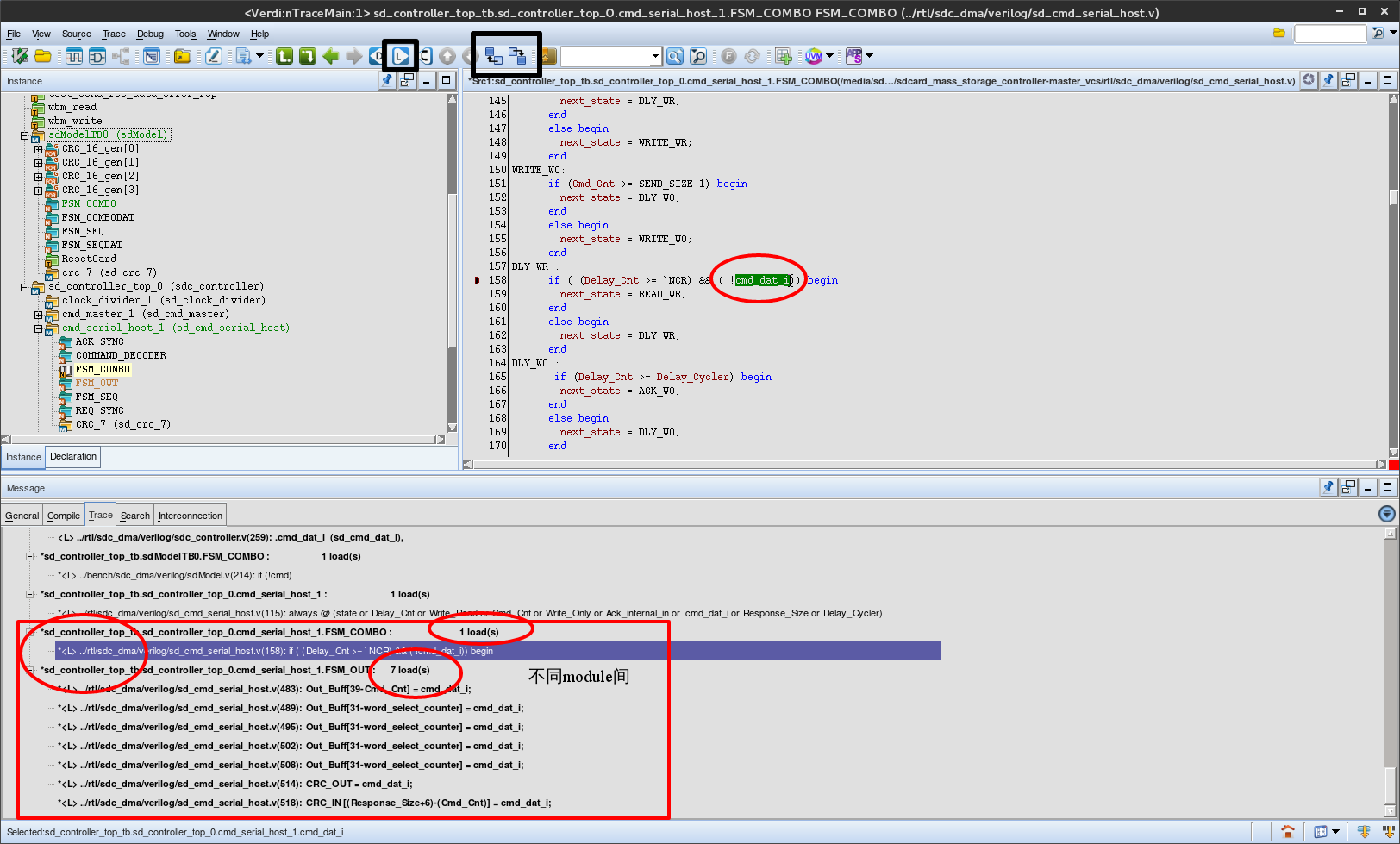

擅用Trace功能

1.Driver

2.Load

3.Connectivity4.Show Previous

5.Show Next6.Show Previous in Hierarchy

7.Show Next in Hierarchy

8.Forward History

9.Backward History

细节请参考verdi的Verdi3.pdf手册

理解module划分

依据对RTL的分析与琢磨,信号的顺藤摸瓜与端口/module间的数据流动,深入体会这个module划分的深意。

代码风格与RTL基础模块

1.基本的Verilog语句块(assign/if-else/always/case)

2.组合逻辑

3.时序逻辑

4.FSM有限状态机阅读

边猜边仿真

1.可以依据端口输入输出及协议猜测RTL的大致意图。

2.根据设计文档的寄存器描述,使用Verdi追踪(trace)RTL。

2.结合仿真结果,追踪理解信号。

参考资料

[1]. verdi3.pdf(Verdi安装目录doc下)

形而上者谓之道 形而下者谓之器。

浙公网安备 33010602011771号

浙公网安备 33010602011771号