riscv co-sim:riscv cpu开发集成simulator仿真

riscv co-sim:riscv cpu开发集成simulator仿真

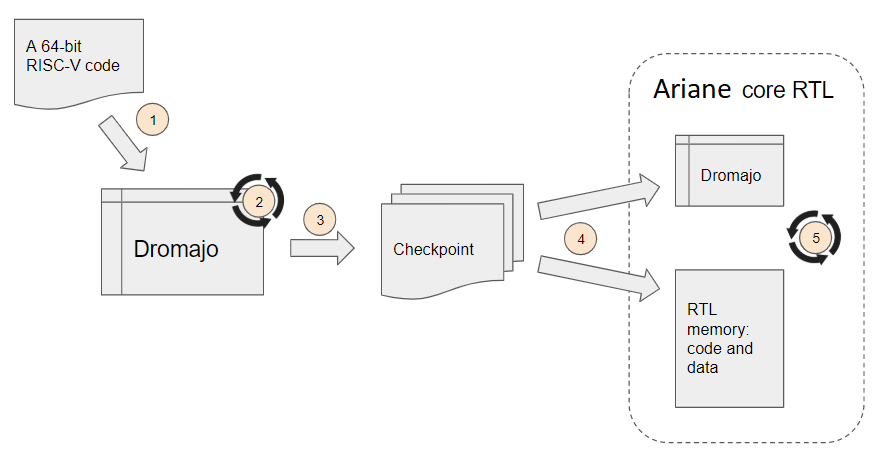

1. 原理

a. 确定对比粒度

仿真对比的粒度需要simulator(eg.dromajo、spike)与RTL内核共同状态确定

simulator与RTL存在的相同状态(simulator维护的变量与RTL的寄存器状态)越多,对比项可以越多,也越精细,同样代价越大

一般而言,我们维护程序在提交指令后可见的架构寄存器相同(仅在指令提交时进行对比),即可保证simulator与RTL内核行为一致

如果simulator更加精细,流水线与RTL一致,每级流水线内都有相对应的状态,我们可以做到每个周期都进行对比,比较对应流水线的状态

RTL trace interface

将RTL内部需要跟踪对比的信号拽到testbench中

| 关键信号 | 含义 |

|---|---|

| valid | 指令提交,架构寄存器已经更新 |

| core input signals | 输入到core内进行计算处理的数据,即影响架构寄存器变化的信号 |

| core state signals | 架构寄存器或者其他需要与simulator对比的信号 |

simulator step interface

提取simulator中单步执行的核心函数,包括输入的形式参数,返回的结果

DPI interface & TestBench

将simulator的单步执行接口使用DPI接口封装,使TestBench可见

在TestBench中调度。监控valid信号,有效启动捕获RTL接口上的信号,并将信息通过DPI接口注入到simulator 单步执行接口中

simulator执行后将返回结果与RTL的结果进行对比,结果一致即可确认RTL与simulator行为一致,如此循环往复对比

另外,一般而言,simulator与RTL是螺旋更迭的,可以不断增加simulator与RTL对比的状态,以使两者有更多checkpoint,这样在simulator上跑的所有case能快速在RTL环境移植与debug

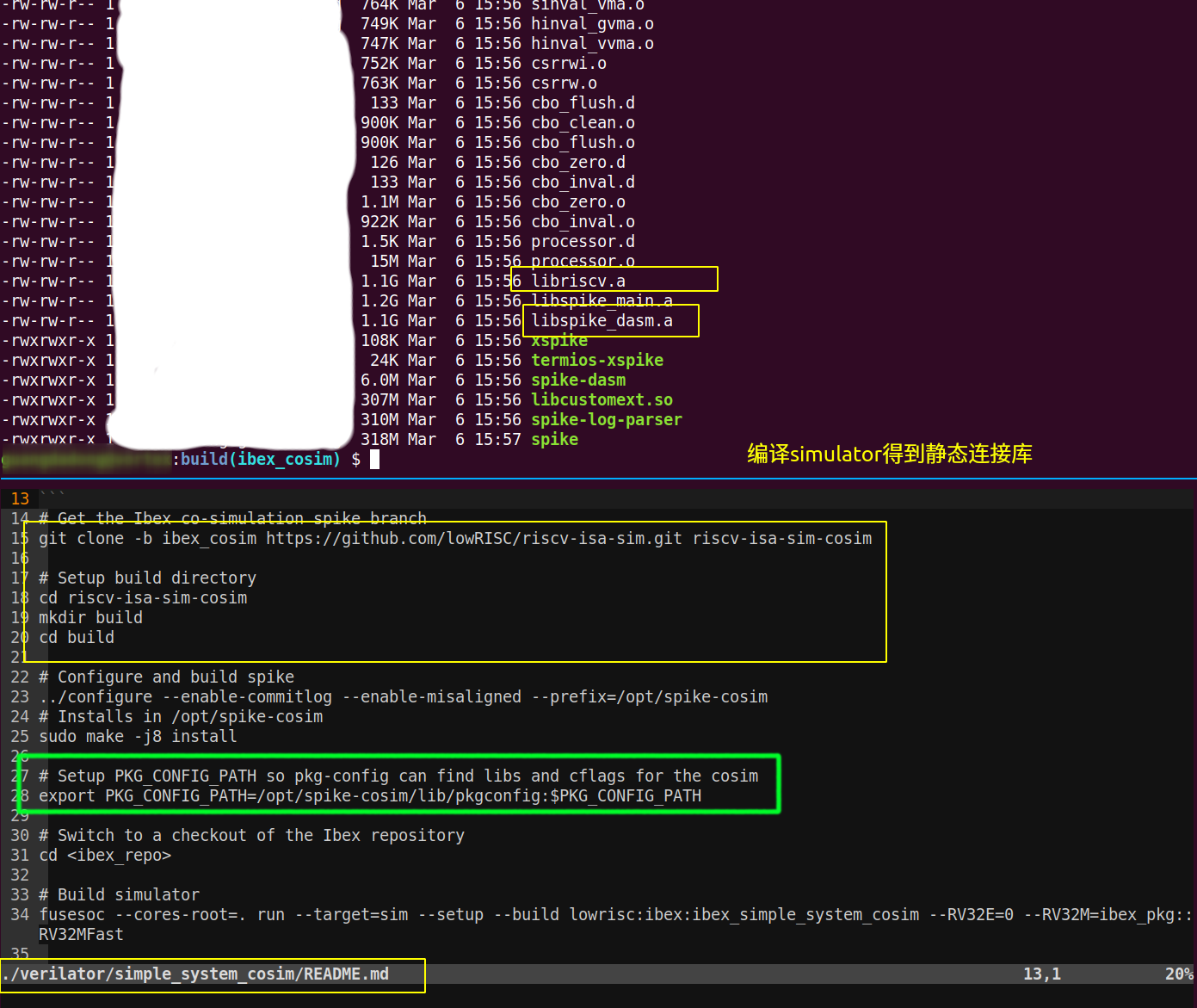

b. 系统构建

simulator编译生成共享库文件

编译simulator,获得静态链接库(linux上一般以.a为后缀)

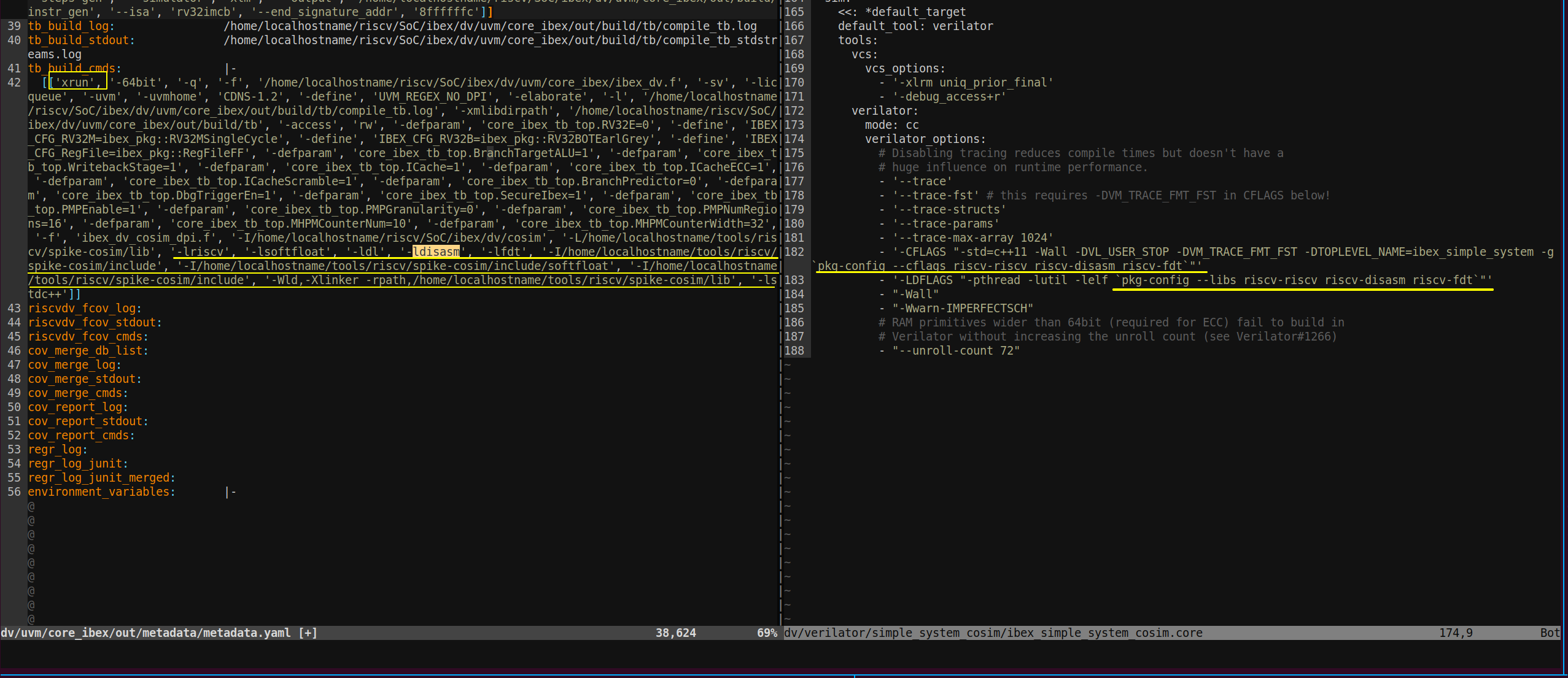

emulator编译

使用RTL仿真工具(如vcs、verilator、xrun等)将riscv内核、simulator编译得到的静态链接库以及带有对比的TestBench进行编译,得到可执行的emulator

c. run tests

使用生成的emulator加载二进制文件进行RTL仿真与关键状态对比

2. 案例:ibex

-

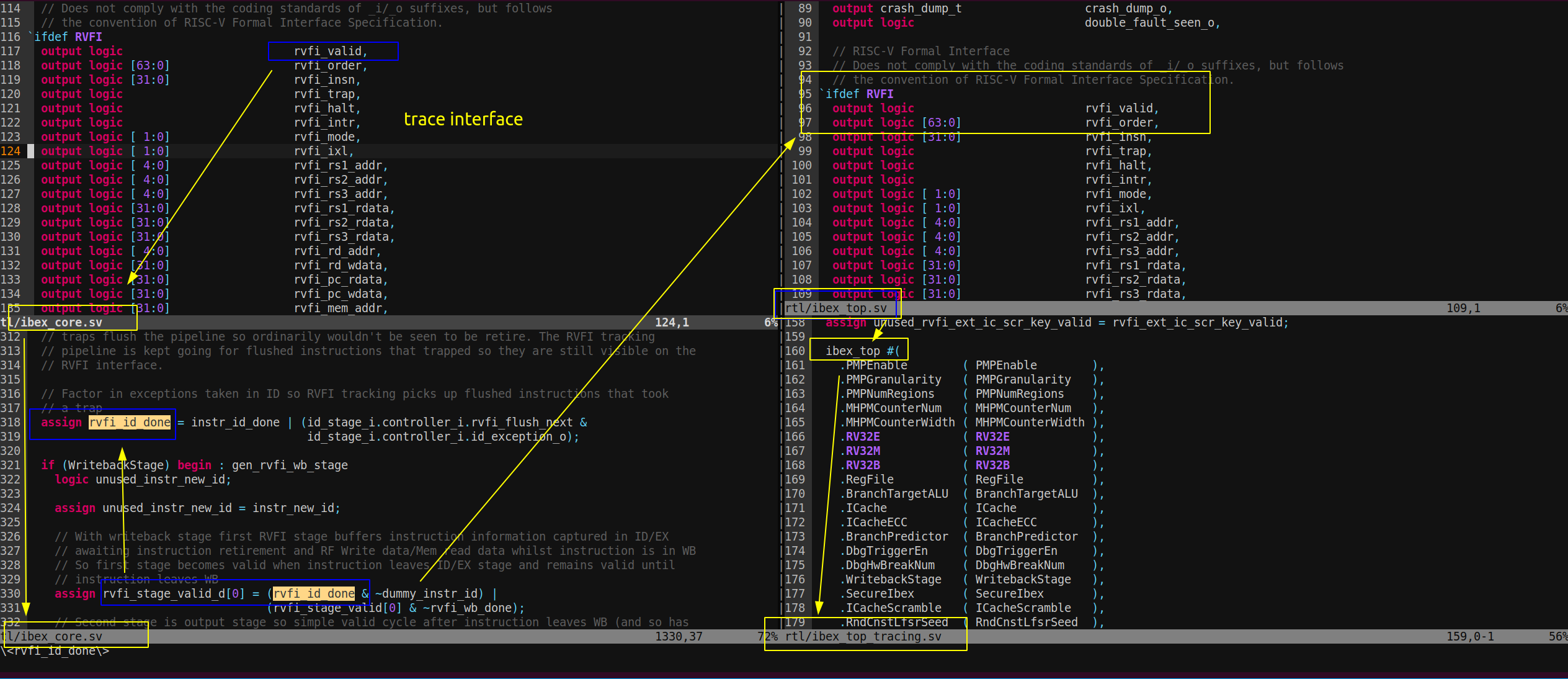

RTL trace interface

![image]()

-

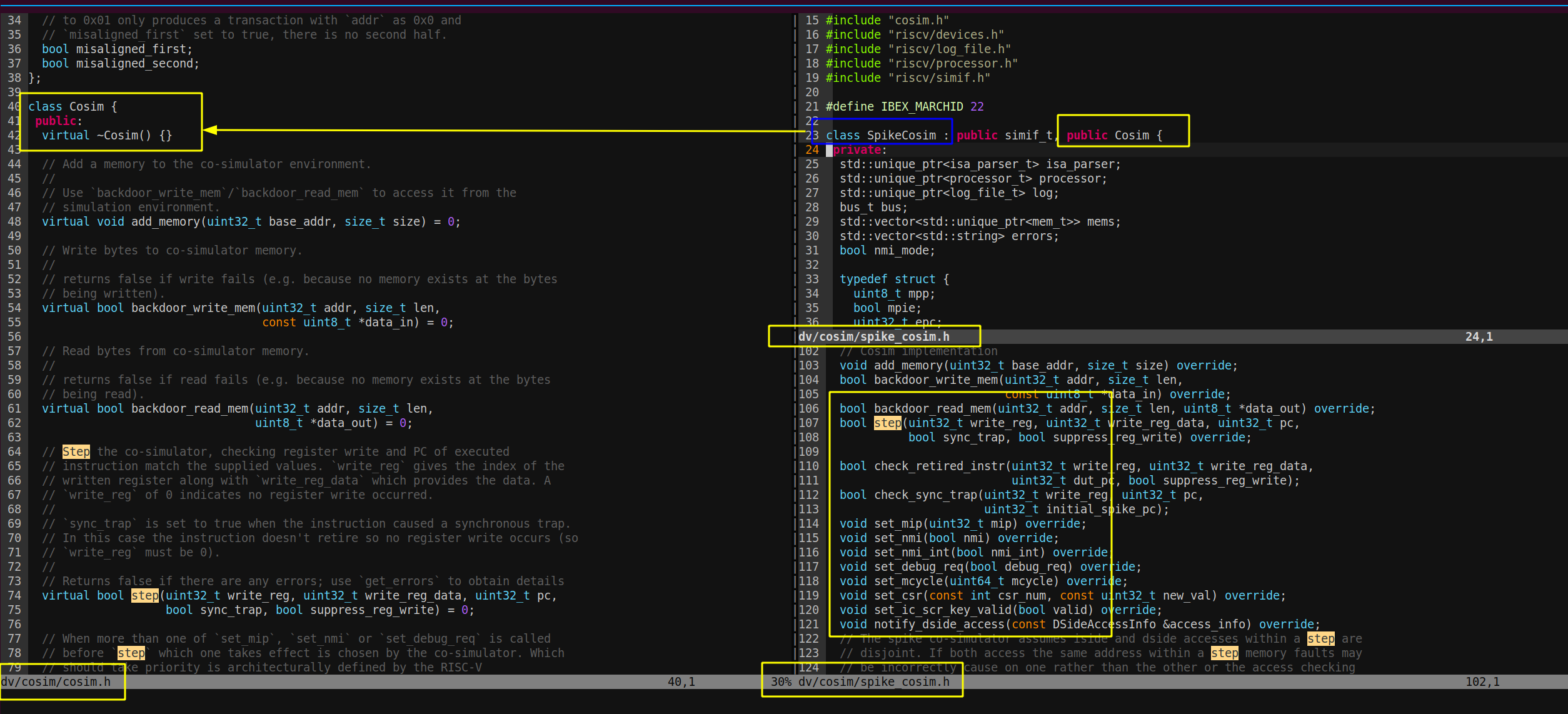

simulator step interface

![image]()

-

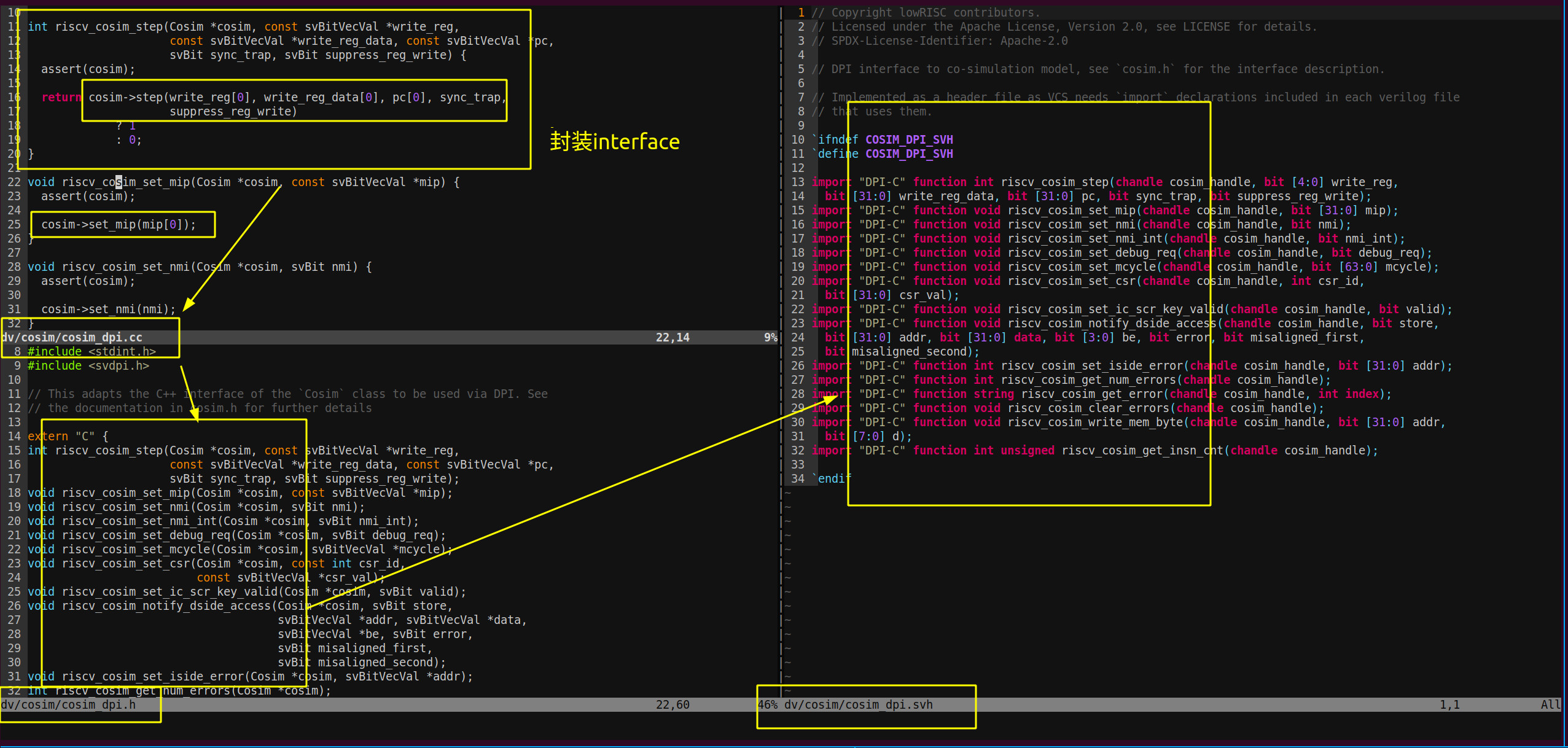

DPI interface & TestBench

![image]()

-

simulator编译生成共享库文件

![image]()

-

emulator编译

![image]()

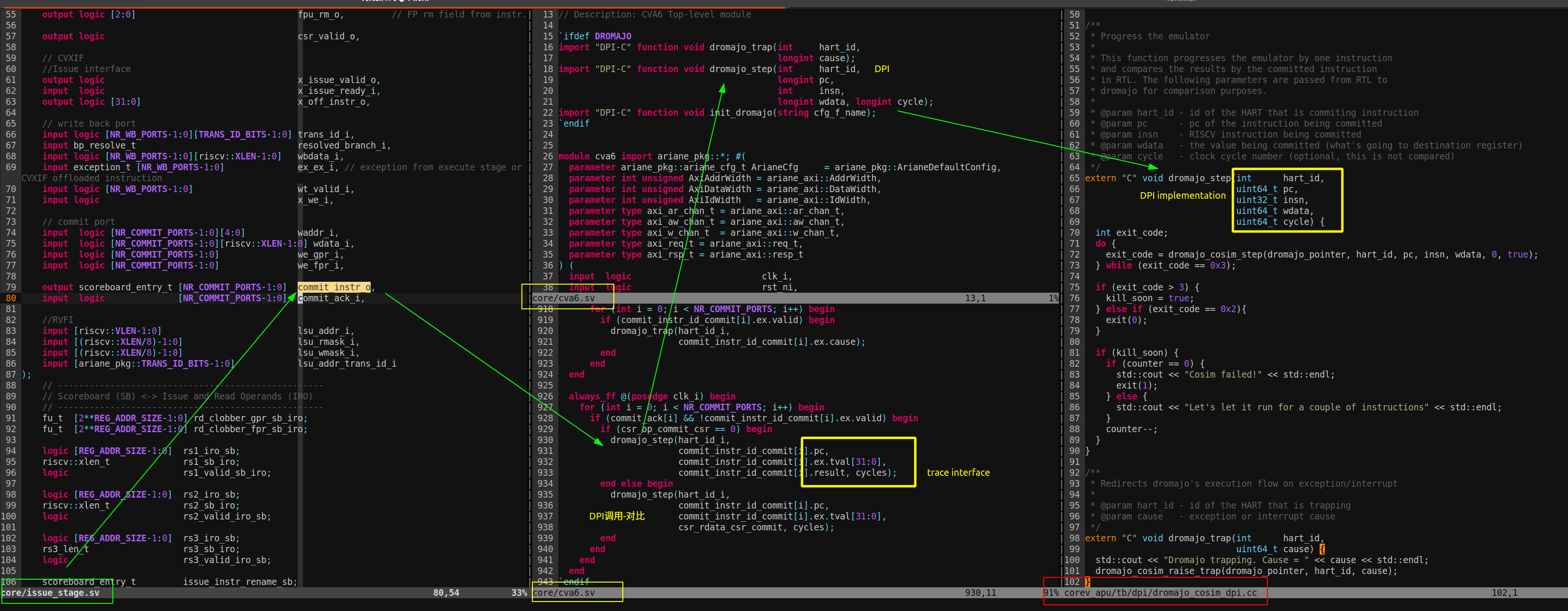

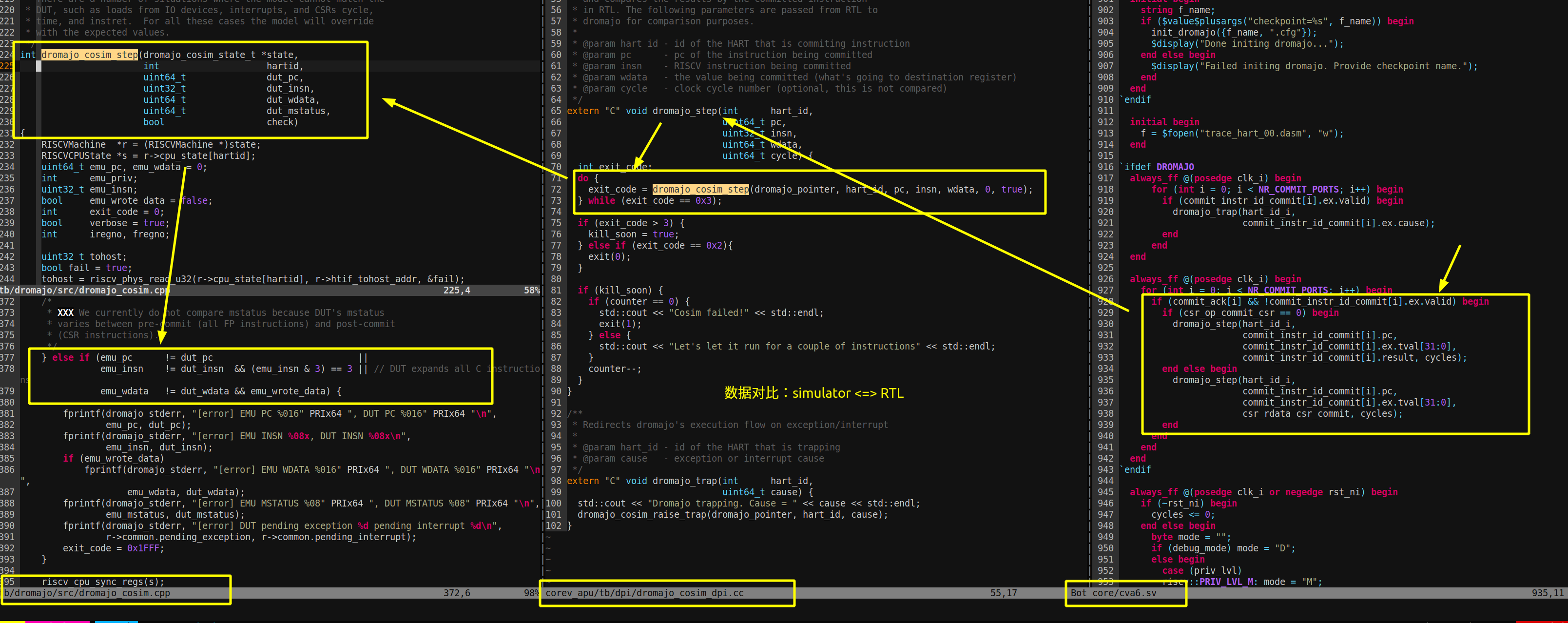

3. 案例:cva6

-

dpi interface

![image]()

-

data compare

![image]()

-

emulator编译

![image]()

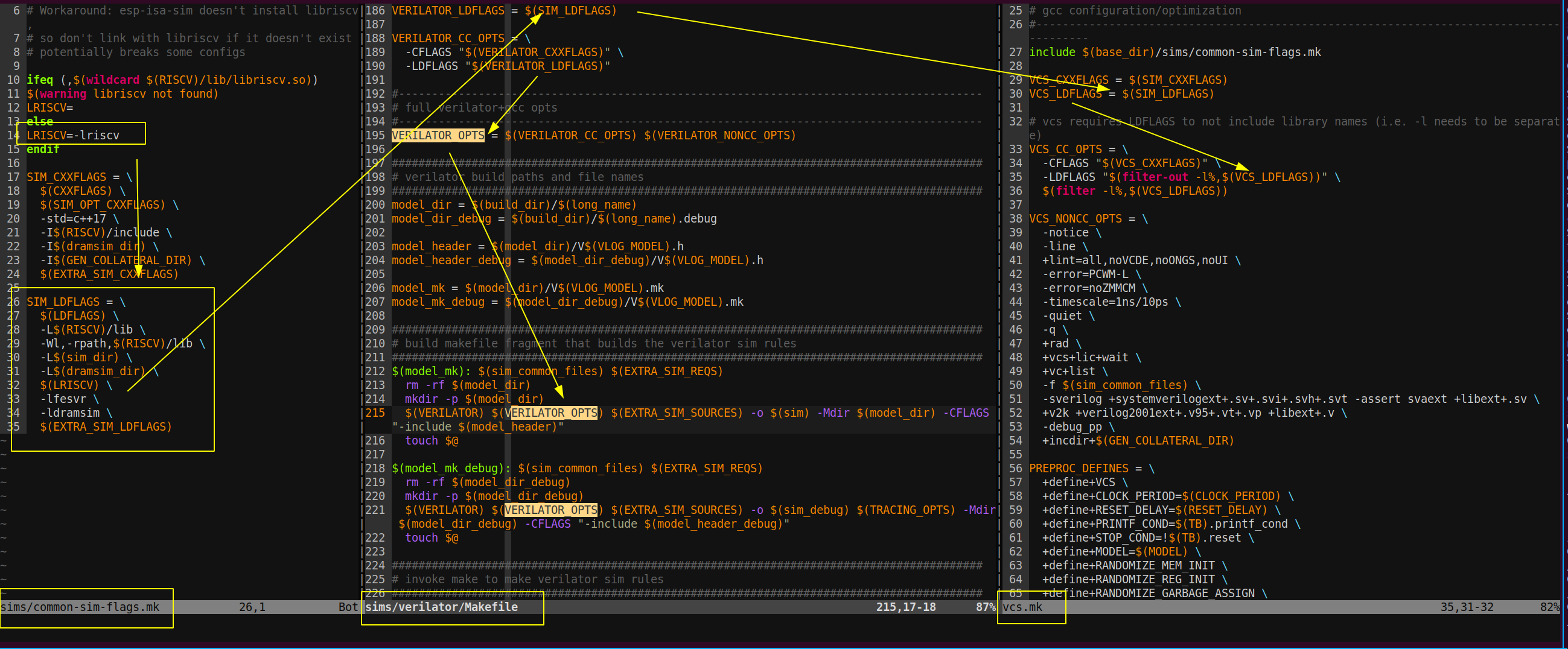

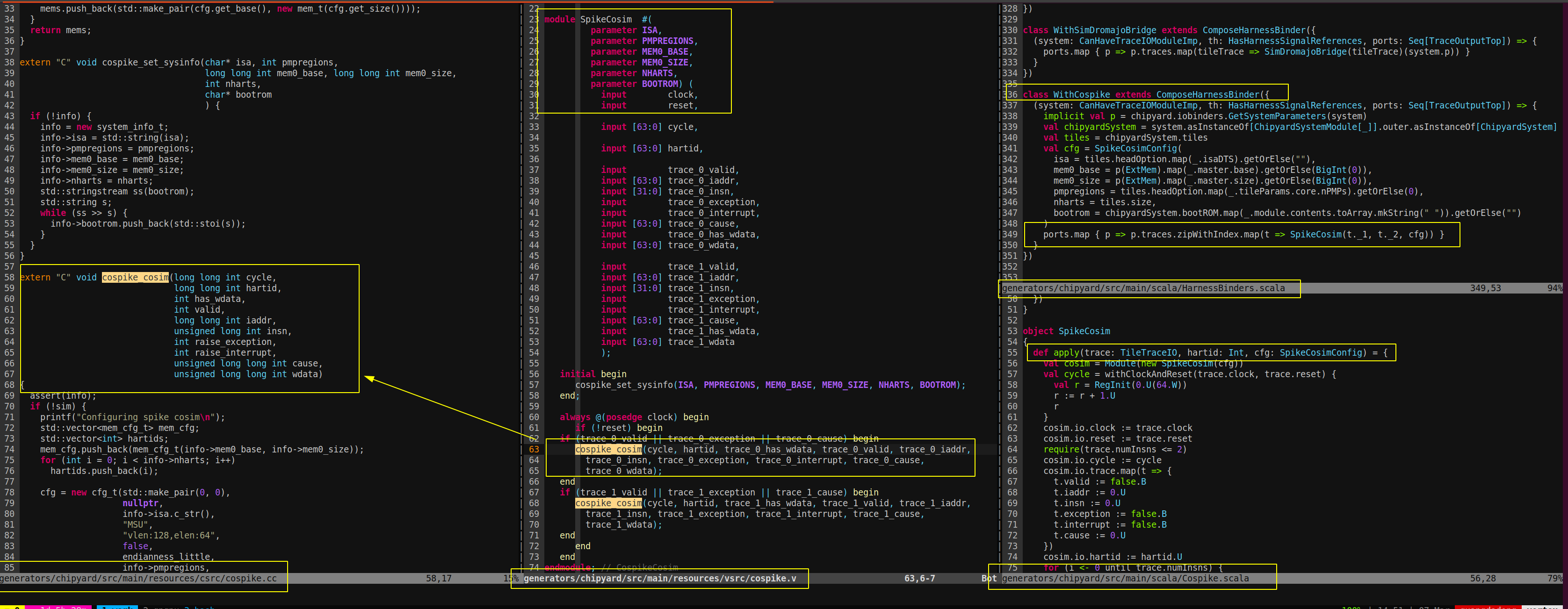

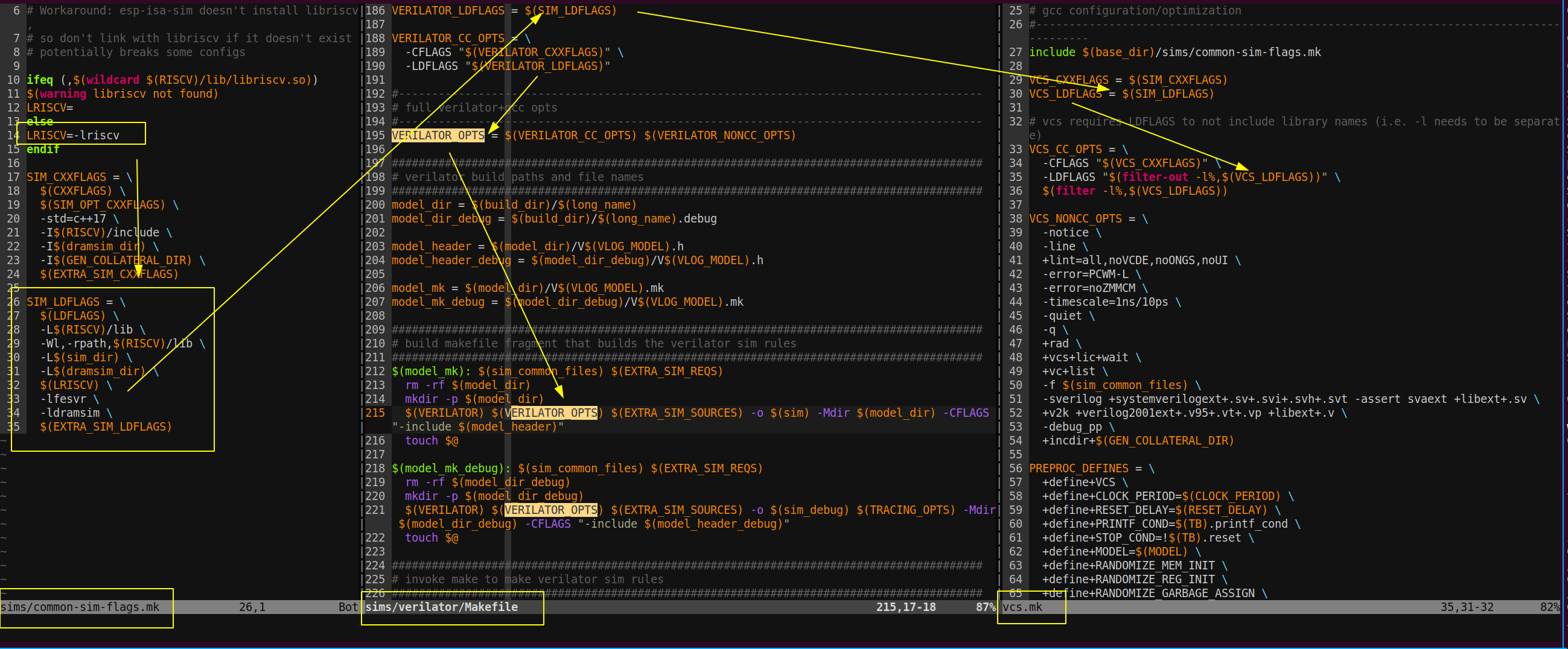

4. 案例:chipyard

-

dpi interface

![image]()

-

emulator编译

![image]()

5. 延伸

借助dpi接口能力与co-sim思路,其他协议或模块也可以组合c/c++的模型(golden model)与RTL设计形成co-sim环境

浙公网安备 33010602011771号

浙公网安备 33010602011771号