TestBench的主要目标是:

- 实例化DUT-Design Under Test

- 为DUT产生激励波形

- 产生参考输出,并将DUT的输出与参考输出进行比较

- 提供测试通过或失败的指示

TestBench产生激励的三种方式:

- 直接在testbench中产生

- 从矢量中读入

- 从单独的激励文件中读入

比较流行的做法是使用matlab产生激励文件,由testbench读入该激励文件并将激励馈送到DUT,DUT产生的相应输出以文件的形式存储,由matlab读取并与理想的响应作比较。

下面以一个简单的同步加法器为例,分析不同形式的testbench的写法。

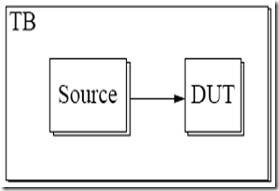

1. 简单的TestBench

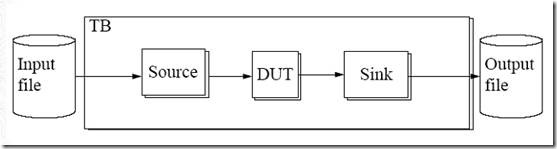

简单的testbench只适合于相对比较简单的设计。如图1-1所示,在testbench中只是简单的实例化了一个DUT,激励在testbench中产生。可见这种方式的testbench可重用性比较差。

图1-1 简单的testbench

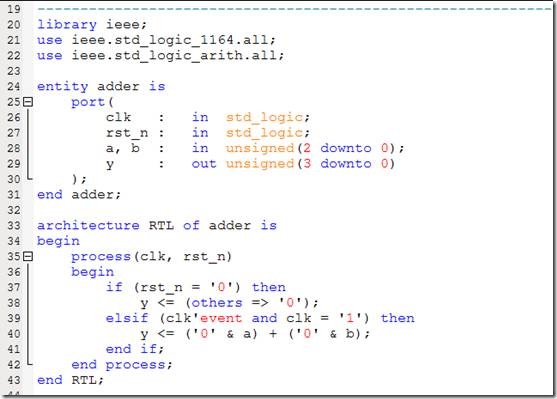

图1-2 DUT VHDL代码

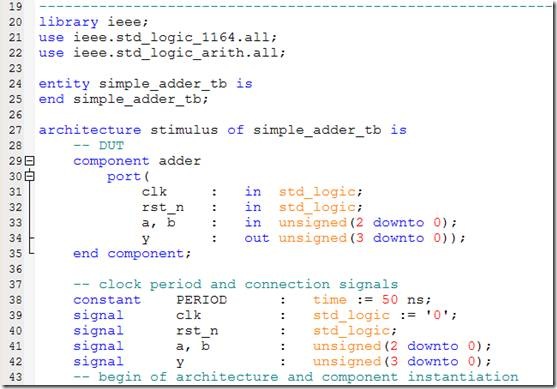

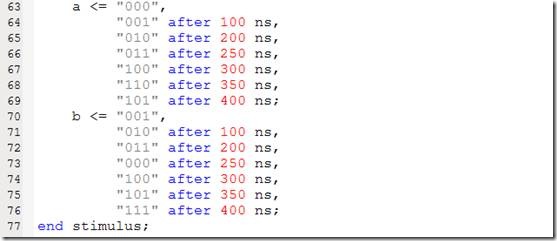

简单的testbench代码如图1-3所示。

图1-3 简单的testbench 代码

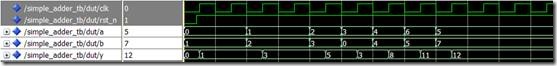

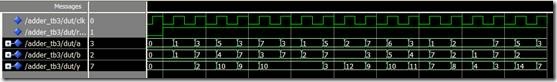

仿真结果如图1-4所示。

图1-4 仿真结果

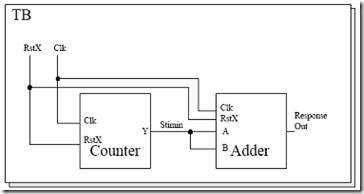

2. 具有独立激励源的testbench

将激励源作为一个文件在testbench中进行实例化,比较适合于具有复杂输入和简单输出的设计。如图2-1所示。

图2-1 具有独立激励源的testbench

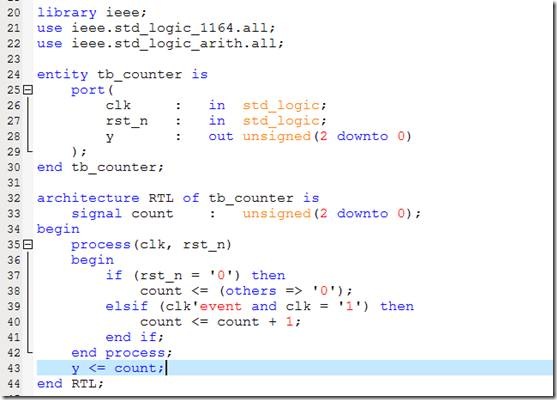

在本例中,DUT的激励源为一个计数器。相应的VHDL代码如下:

图2-2 激励源代码

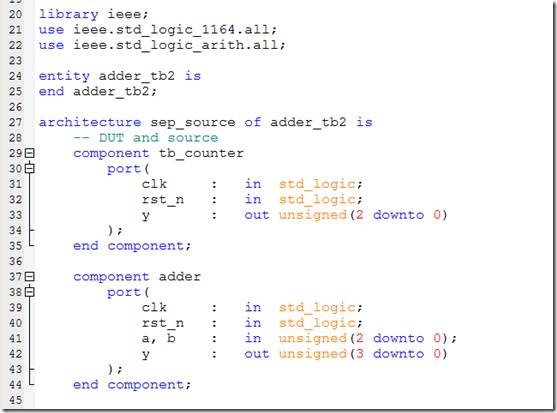

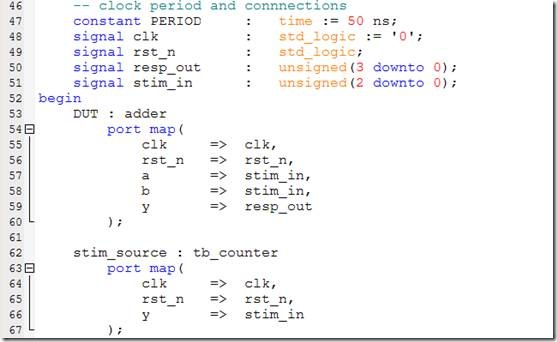

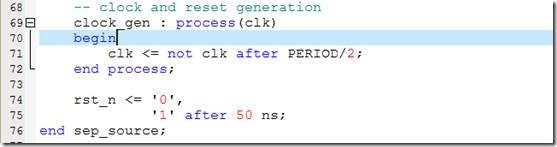

编写完成激励源的VHDL码后,还需要在testbench中进行实例化,方法与实例化DUT的方法一致。相应的testbench代码如下:

图2-3 具有独立激励源的testbench代码

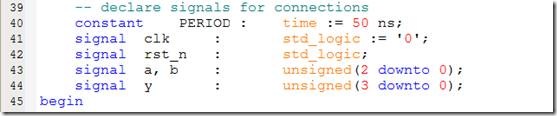

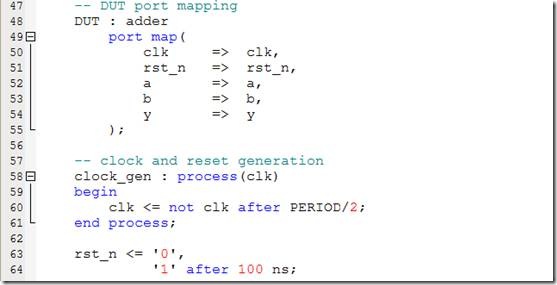

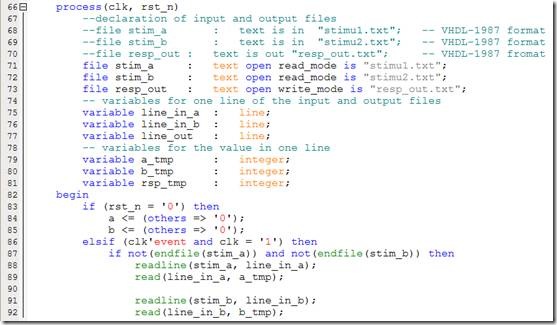

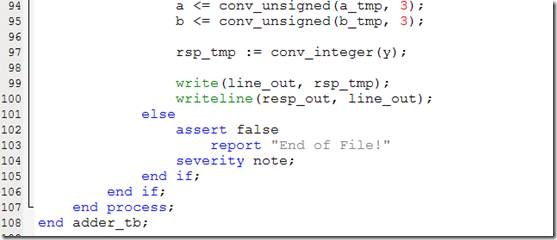

3. 使用TextIO的testbench

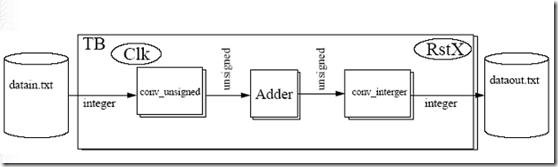

当设计的输入输出都比较复杂时,尤其是在做复杂的算法仿真时,需要产生多种形式的激励输入,还要对仿真结果输出做复杂的分析时,使用TextIO的testbench具有最高的效率。在使用TextIO的testbench中,为DUT从输入文件读取激励输入,激励信号经过DUT处理后写入到输出文件中。其原理如图3-1所示。

图3-1 使用TextIO的testbench原理框图

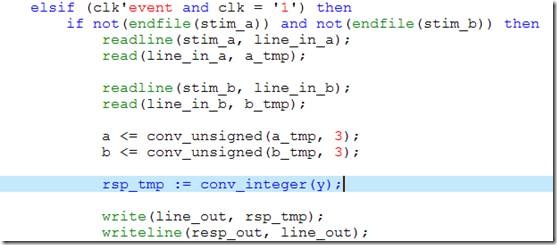

在本例中,我们将Matlab产生的两个激励输入文件加载到testbench中,在输入到DUT之前先进行类型转换,然后按照时钟节拍将数据一个一个的加载到DUT的输入端口,再按照时钟节拍从DUT输出端口将数据写入到输出文件,当然在写入输入文件之前也要先进行类型转换。如图3-2所示。

图3-2 针对本例的testbench原理框图

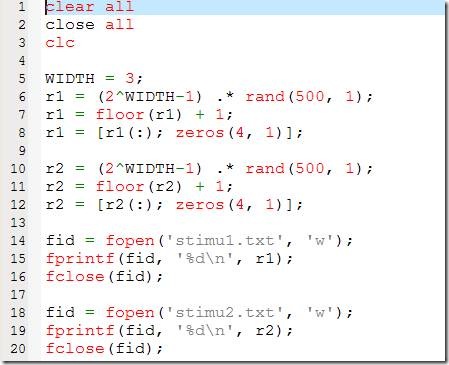

Matlab产生加法器两个输入激励的代码如下,激励输入为范围在0~7之间的随机数,最后保存到txt文件中供testbench读取。

图3-3 激励产生m代码

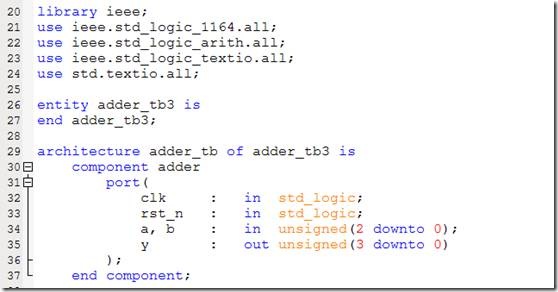

使用TextIO的testbench代码如下:

仿真结果如图3-5所示。

图3-5 仿真结果

下面我们对于如何在TestBench中使用TextIO做一个小结。

(1).首先需要声明TextIO的包集

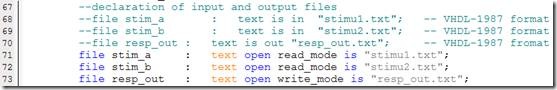

(2).然后在process中声明输入、输出文件

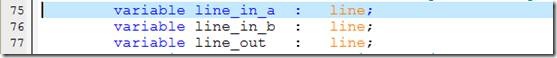

(3).接着声明读写文件的行变量

(4).再声明用于保存行变量中值的数据变量

(5).最后进行文件的读写,在读文件之前需要判断文件是否已经被读到末尾。读文件时,先从文件中按行读出一行数据,再将行中的数据读到数据变量中。写文件时,先将数据变量组合成一行,再将行变量中的数据写入文件。需要注意的是只有variable型才是文件存取类型,不能使用signal型。

TextIO包集中定义了一些常用的文件操作过程:

readline(file_var, line_var);

--用于从文件file_var中读取一行数据保存到line_var中

read(line_var, data_var);

--用于从line_var中读取数据保存到data_var中

writeline(file_var, line_var);

--用于将line_var写入到file_var中

write(line_var, data_var);

--用于将data_var写入到line_var中

endfile(file_var)

--判断file_var是否已经到文件末尾

4. Ref

[1] TKT-1210 Digital design Ⅱ,Lect5 VHDL Test Bench