3. 硬件断点

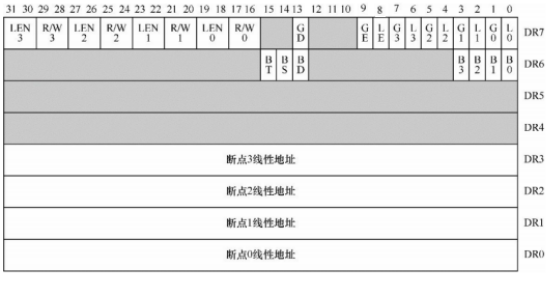

一.DR7的情况:

R/W0 ~ R/W3:

00 执行对应地址的指令时中断

01 向对应地址写入数据时中断

10 I/O读写时中断,忽略,暂时用不到

11 向对应地址读写数据时都中断,但是从该地址读取指令除外

LEN0 ~ LEN3:

00 1字节长

01 2字节长

10 8字节长(奔腾4或至强)或未定义(其他CPU),忽略,暂时用不到

11 4字节长,注意,如果R/Wn为0(即执行指令中断),则这里应该设置为00,

L0 ~ L3:

启用或禁止对应的局部断点。该位设为0时禁止此断点,设为1时满足定义的断点条件便中断,并自动清除此位。

G0 ~ G3:

启用或禁止全局断点,设为1时,CPU在任何任务中检测到满足条件时则中断,不同于L0 ~ L3,不会自动清除此位。忽略,暂时用不到。

LE和GE:

启用局部和全局(精确)断点 Local and Global(exact) breakpoint Enable。从486开始的CPU都忽略这两位的设置,此前是启用以保证产生调试异常的。

GD:

启用访问检测General Detect Enable,设为1时,CPU检测到即将修改调试寄存器(DR0 ~ DR7)的指令时,会在执行这条指令前产生一个调试异常。

二.DR6的情况:

B0 ~ B3:

Breakpoint0 ~ Breakpoint3,断点是否命中,例如B0为1,说明满足DR0、LEN0和R/W0条件的断点发生了。

BD:

检测到要访问调试寄存器

BS:

单步Single Step,如果BS为1,说明异常是由于单步执行(Single Step)模式触发的。如果BS为0,说明是硬件断点触发时产生的单步异常。

BT:

任务切换Task Switch

8个调试寄存器,分别是DR0 ~ DR7

调试地址寄存器:DR0 ~ DR3

调试控制寄存器:DR7

调试状态寄存器:DR6

DR4和DR5保留。

浙公网安备 33010602011771号

浙公网安备 33010602011771号