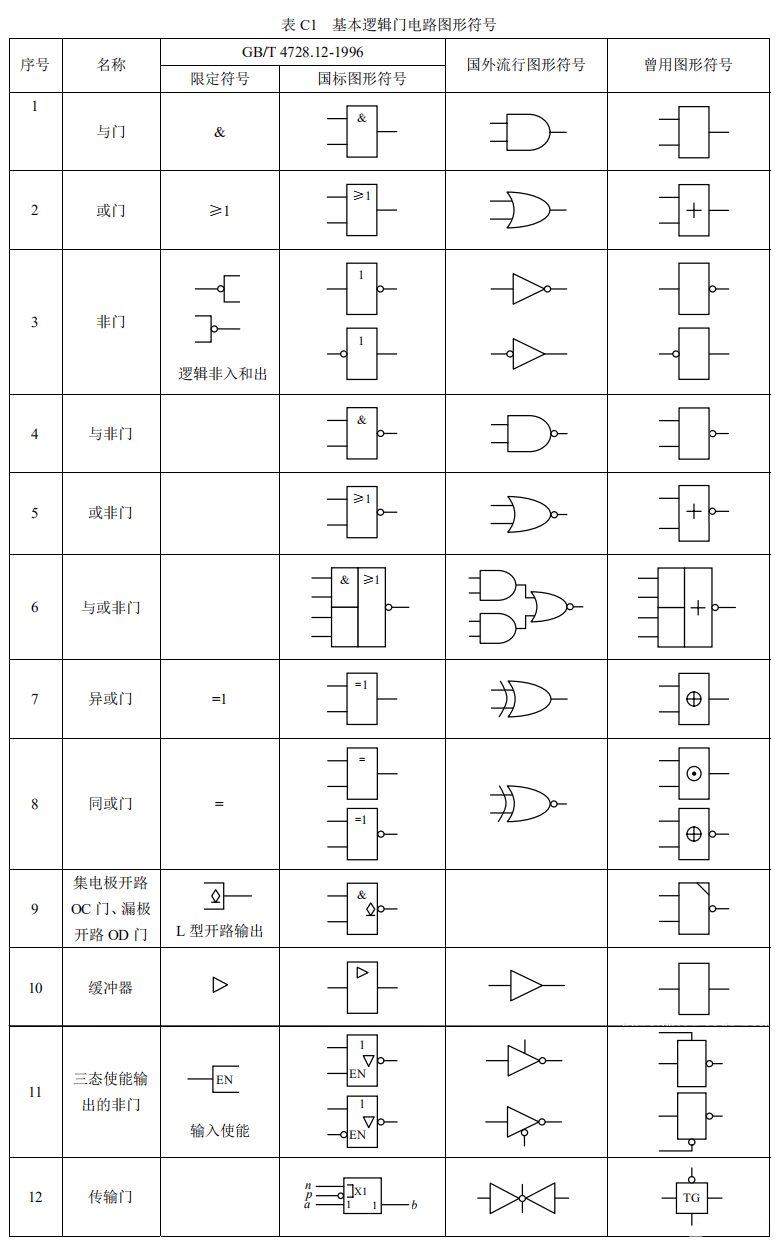

电路逻辑门图形符号

Verilog语言内置了12个基本门级元件模型,如下表所示。门级元件的输出、输入必须为线网类型的变量。

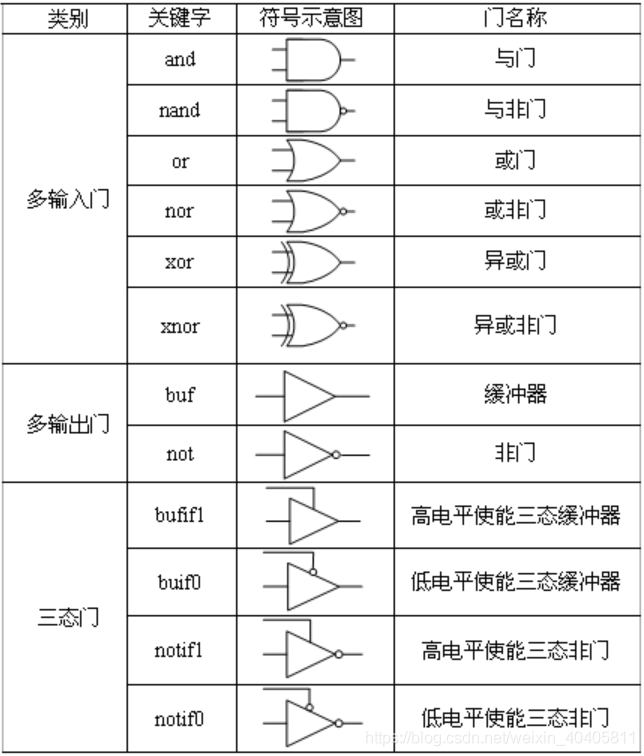

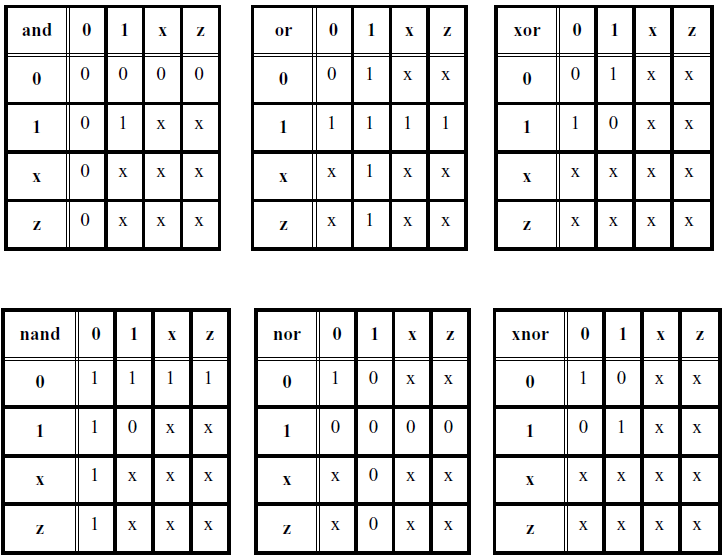

1、多输入门

and、nand、or、nor、xor和xnor是具有多个输入的逻辑门,它们的共同特点是:只允许有一个输出,但可以有多个输入。

and的一般调用格式为:

and A1(out, in1, in2, in3);

其中,调用名A1可以省略。nand、or、nor、xor和xnor的调用格式与and的类似。

| 原语名称 | 图形符号 | 逻辑表达式 |

|---|---|---|

| and(与门) | L = A & B | |

| nand(与非门) | L = ~(A & B) | |

| or(或门) | L = A | B | |

| nor(或非门) | L =~( A | B) | |

| xor(异或门) | L = A ^ B | |

| xnor(同或门) | L = A ~^ B |

2、多输出门

buf、not是具有多个输出的逻辑门,它们的共同特点是:允许有多个输出,但只有一个输入。

一般的调用格式为:

buf B1(out1, out2,…, in);

not N1(out1, out2,…, in);

其中,调用名B1、N1可以省略。

| buf | 0 | 1 | x | z |

|---|---|---|---|---|

| 输出 | 0 | 1 | x | x |

| not | 0 | 1 | x | z |

|---|---|---|---|---|

| 输出 | 1 | 0 | x | x |

3、三态门

bufif1、bufif0、notif1和notif0是三态门元件模型。这些门有一个输出、一个数据输入和一个输入控制。如果输入控制信号无效,则三态门的输出为高阻态z。

一般的调用格式为:

bufif1 B1(out, in, ctrl);

bufif0 B0(out, in, ctrl);

notif1 N1(out, in, ctrl);

notif0 N0(out, in, ctrl);

其中,调用名B1、B0、N1和N0可以省略。

| bufif1 | 控制端(1有效) | bufif0 | 控制端(0有效) | |||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | x | z | 0 | 1 | x | z | |||

| 0 | z | 0 | 0/z | 0/z | 0 | 0 | z | 0/z | 0/z | |

| 1 | z | 1 | 1/z | 1/z | 1 | 1 | z | 1/z | 1/z | |

| x | z | x | x | x | x | x | z | x | x | |

| z | z | x | x | x | z | x | z | x | x | |

| notif1 | 控制端(1有效) | notif0 | 控制端(0有效) | |||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | x | z | 0 | 1 | x | z | |||

| 0 | z | 1 | 1/z | 1/z | 0 | 1 | z | 1/z | 1/z | |

| 1 | z | 0 | 0/z | 0/z | 1 | 0 | z | 0/z | 0/z | |

| x | z | x | x | x | x | x | z | x | x | |

| z | z | x | x | x | z | x | z | x | x | |

浙公网安备 33010602011771号

浙公网安备 33010602011771号