静电与ESD介绍

1.静电

静电即静止不动的电荷,它是正电荷和负电荷在局部范围内失去平衡的结果。静电是通过电子或离子转移而形成的存留在物体表面的一种电能。静电的特点是:聚集时间长、电压高、电量低、作用时间短、受湿度影响大。

图1 静电图示

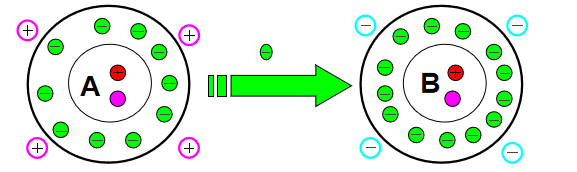

静电的产生原理:电子围绕原子核运动,在外力(包含化学能、动能、热能等)作用下,使得两个物质的电子脱离轨道,离开原来的原子而进入其他的原子。如下图2所示,A原子因失去电子而带有正电,称为阳离子;B原子因获得电子而带负电,称为阴离子。

图2 静电的产生

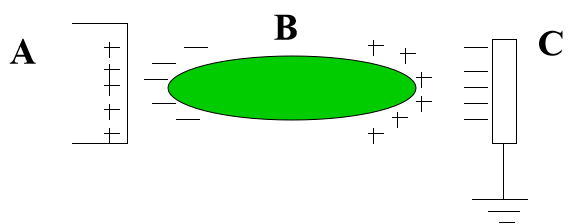

静电产生的方式:(1)摩擦起电,当两个不同材质的物体相互接触是就会使得其中一个物体失去电荷带正电,而另一个物体得到电子带负电。若在分离过程中电荷难以中和,电荷就会累积使得物体带上静电。(2)感应起电,任何放电源的静电场都可能对足够靠近的导电材料产生电荷分离感应,如下图3所示。

图3 感应起电

2.ESD

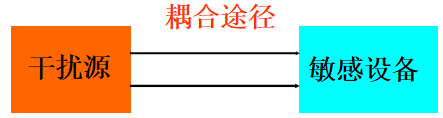

ESD(Electro Static Discharge) 指静电释放,指具有不同静电电位的物体由于直接接触或静电感应所引起的物体之间静电电荷的转移。通常指在静电场的能量达到一定程度之后,击穿其间介质而进行放电的现象。ESD三要素为干扰源、耦合路径和敏感设备,缺少任何一个要素都构不成ESD。

图4 ESD三要素

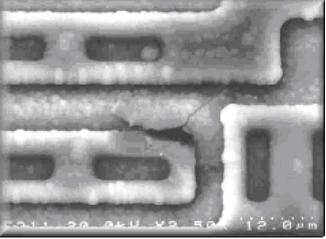

ESD对电子产品的影响很大,ESD可使敏感元件完全失去功能或间歇性失去功能;ESD可使元件直接损坏,从而影响产品质量和增加生产成本。

图5 完全失去功能

图6 间歇性失去功能

ESD敏感符号和ESD防护符号如下图7所示,其中,ESD敏感符号表示该物体对ESD引起的伤害十分敏感,ESD防护符号表示该物体经过专门设计具有静电防护能力。

图7 ESD符号

3.ESD防护

(1)芯片级ESD防护设计:为加强芯片ESD防护能力,一般会在输入垫片(input pad)周边加上ESD防护电路,在输出垫片(output pad)连接的输出缓冲衡(output buffer)上加强输出缓冲衡的ESD防护能力。

(2)PCB级ESD防护设计:为了加强PCB的ESD防护能力,一般会在各接口器件增加防护电路(瞬态抑制二极管、磁珠等),规范防护器件的布局(接口器件和防护器件布局在同一面),规范布线(走线从接口器件→防护器件→内部器件,布线尽量在同一层),设计PCB的ESD放电路径等。

(3)生产过程ESD防护:生产过程的ESD防护主要包括一下几点:

a.工作人员要穿着防静电衣服、鞋子、手套、手环和帽子等;

b.工作台配导电座垫、地面铺导电地毯、配抗静电椅、配粒子风扇等;

c.包装使用抗静电包装袋或导电搬运箱,搬运过程使用导静电车等;

d.工作环境湿度控制在>40%。

4.ESD测试

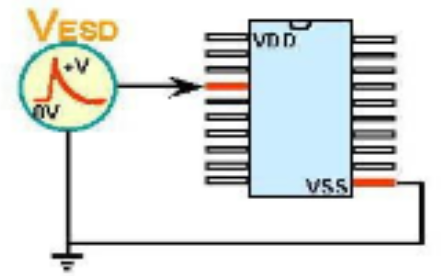

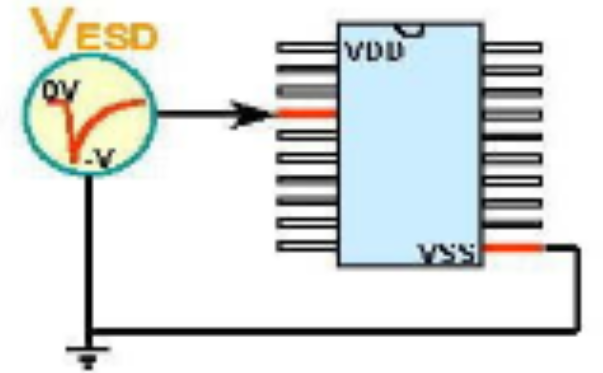

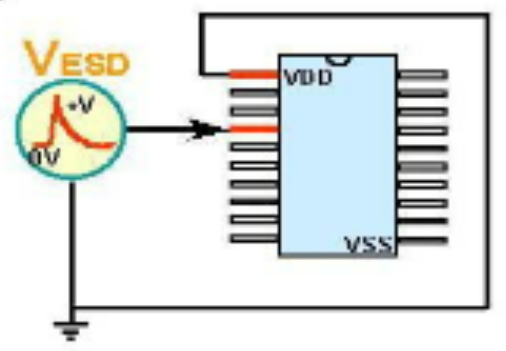

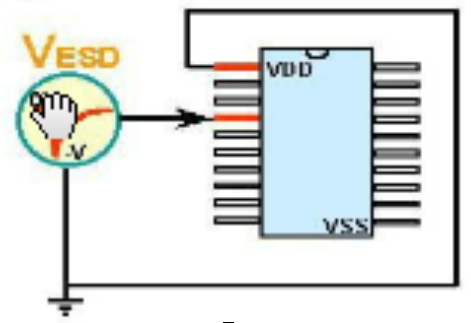

ESD发生在一只输入脚(或输出脚)可能相对于VDD或VSS端具有正的或负的电压极性,因此在工业测试标准上有PS、NS、PD和ND四种放电模式。这些模式的静电放电可能会对输入或输出元件造成损坏,甚至会损及IC内部的电路。

(1)PS模式:VSS脚接地,正的ESD电压出现在该I/O脚对VSS脚放电,此时VDD脚与其他脚皆浮接;

图8 PS模式

(2)NS模式:VSS脚接地,负的ESD电压出现在该I/O脚对VSS脚放电,此时VDD脚与其他脚皆浮接;

图9 NS模式

(3)PD模式:VDD脚接地,正的ESD电压出现在该I/O脚对VDD脚放电,此时VSS脚与其他脚皆浮接;

图10 PD模式

(4)ND模式:VDD脚接地,负的ESD电压出现在该I/O脚对VDD脚放电,此时VSS脚与其他脚皆浮接;

图11 ND模式

浙公网安备 33010602011771号

浙公网安备 33010602011771号