PCB叠层设计及特性阻抗计算

PCB叠层设计是硬件工程师和PCB工程师必备技能之一,Layout工程师会依据叠层设计进行Layout设计,包括线宽、线距、差分走线等设置 。特性阻抗匹配是指在信号能量传输时,要求负载阻抗要和传输线的特征阻抗相等,此时的传输不会产生反射,这表明所有能量都被负载吸收了,反之则在传输中有能量损失,故掌握特性阻抗的计算也很重要。

1.阻抗分类

(1)单端阻抗(Single Ended Impedance):单根信号线测得的阻抗(常用);

(2)差分阻抗(Differential Impedance):差分驱动时在两条等宽等距的传输线测得的阻抗(常用);

(3)共面阻抗(Coplanar Impedance):信号线在其周围GND/VCC之间传输时所测试到得阻抗(不常用)。

2.阻抗影响因素

(1)正比因素:线路层与接地层间介质厚度H1/H2/H3、相邻线路与线路间的距离S;

(2)反比因素:介电常数Er、线底宽度W1、线面宽度W2、铜厚T、基材阻焊厚度C1、线面阻焊厚度C2、线间阻焊厚度C3、阻焊介电常数CEr。

故关系式可以理解为Z=HS/Er*W*T*C*CEr。

3.叠层设计

(1)确定基材:根据产品的使用环境要求和板厂备料情况,选择合适的PCB板材(提取Er),常见的有:Tg=150的生益S1411 150板材,Tg=180的台耀TU-768板材。

(2)确定板厚:根据产品要求或者设备结构要求,确定线路板的成品板厚,常见的有:0.8mm、1.0mm、1.2mm、1.6mm、2.0mm,误差一般为10%。

(3)确定板层数:根据元器件的密集程度以及信号复杂程度,确定线路板的布线层数,常见的有:单层、双层、4层、6层、8层及以上。

(4)确定布线层布局:根据产品的特性进行布线层的布局,比如4层板有:Top(Singel)-L2(GND)-L3(GND/VCC)-Bottom(Singel),此方式适用于大部分的电子设备,SI性能较好;Top(GND)-L2(Singel/VCC)-L3(Singel/VCC)-Bottom(GND),此方式适用于射频类电子设备,EMI性能较好。

(5)确定特性阻抗值:根据产品的所有信号类型及特性,确定所有需要管控特性阻抗的阻抗值,常见的有:单端特性阻抗=45/50/55/60欧姆,差分特性阻抗=85/90/100欧姆。

(6)设计叠层参数:依据所需阻抗值,使用Polar-Si9000软件设计管控信号线的各层线宽、线距、层间介质厚度、铜厚、阻焊厚度等参数设计合理的叠层参数,一般线宽选择≥4mil、线距选择≥5mil,信号层和参考层的介质厚度在2.5mil≤H≤6mil,内层铜厚=1oz,外层铜厚+Plating=0.5oz。

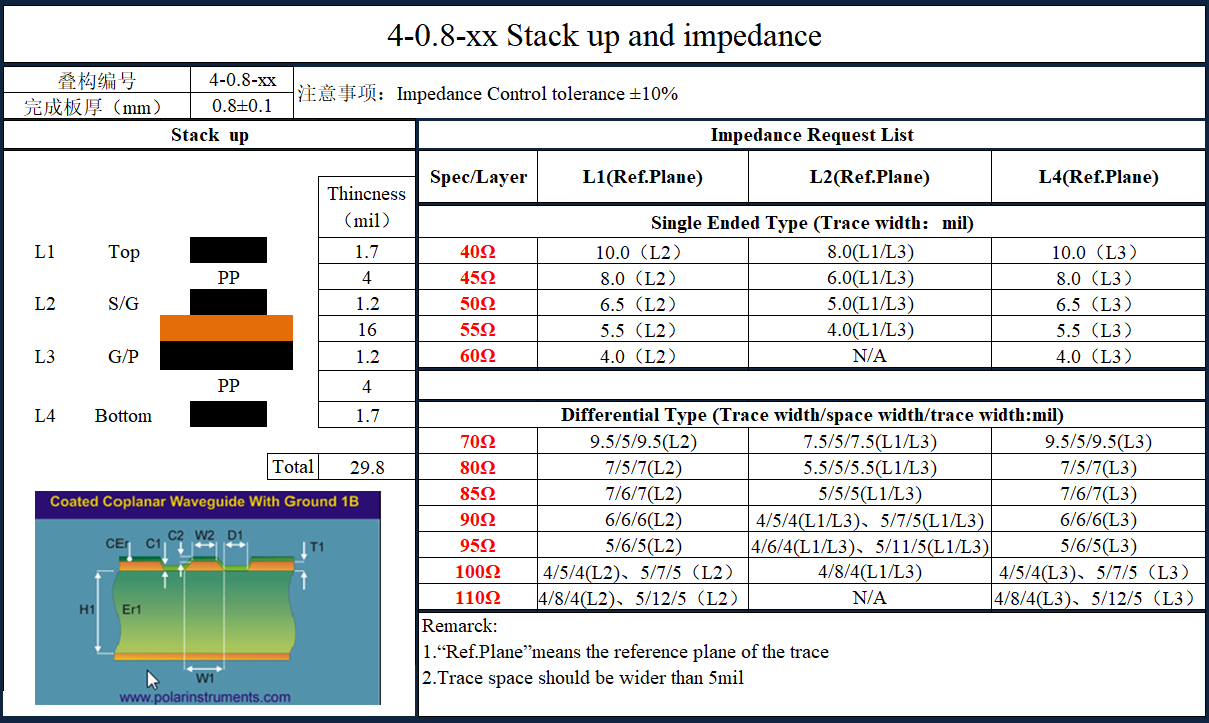

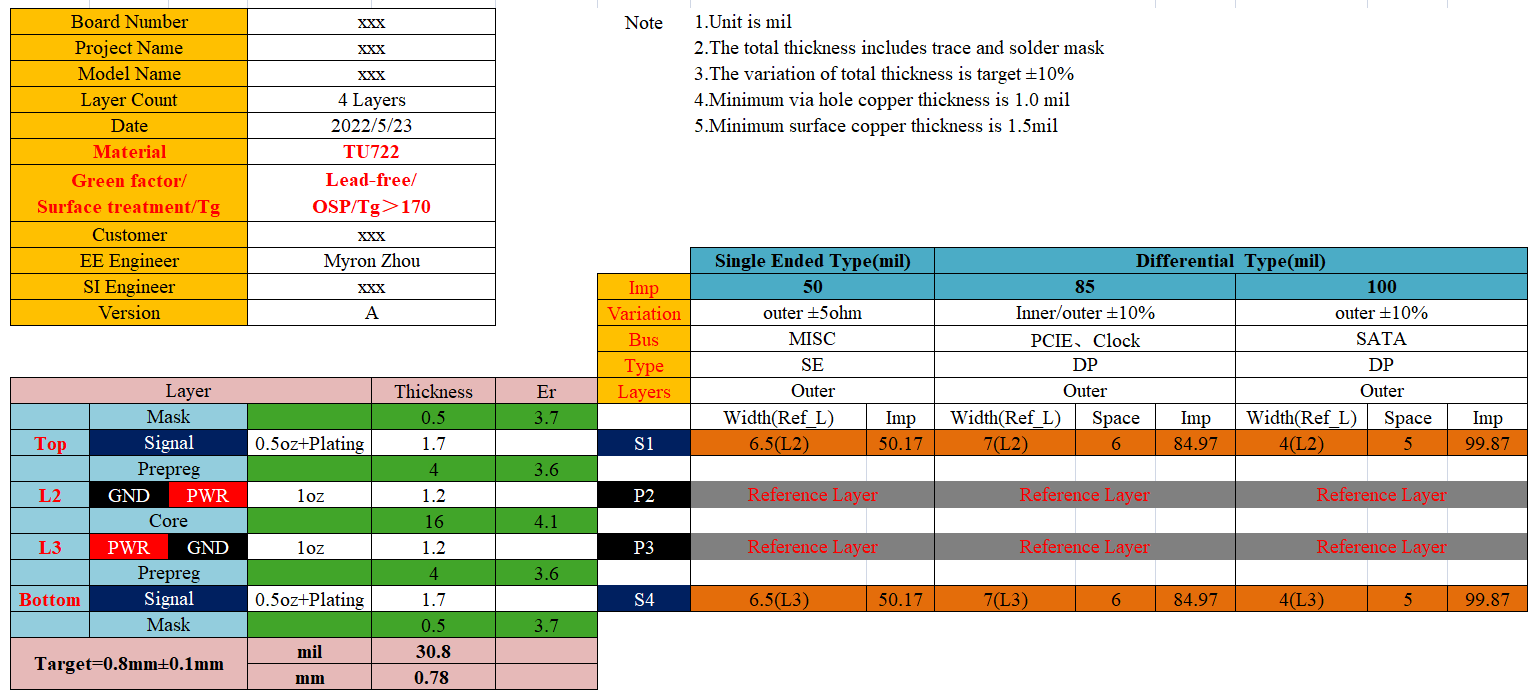

(7)设计叠层表:设计叠层表以供板厂确认,板厂会进行微调及确认,得到最终的叠构表。如下图1所示为通用型叠层表,图2为专用型叠层表。

注:通用型叠层表:需要额外提供板厂信息给板厂,并将表格中不需要管控特性阻抗部分的信息隐藏起来,只留需要管控的部分。

专用型叠层表:叠层信息比较全面,无需额外提供资料,管控的特性阻抗也提取出来。

图1 4层板通用型叠层表

图2 4层板专用型叠层表

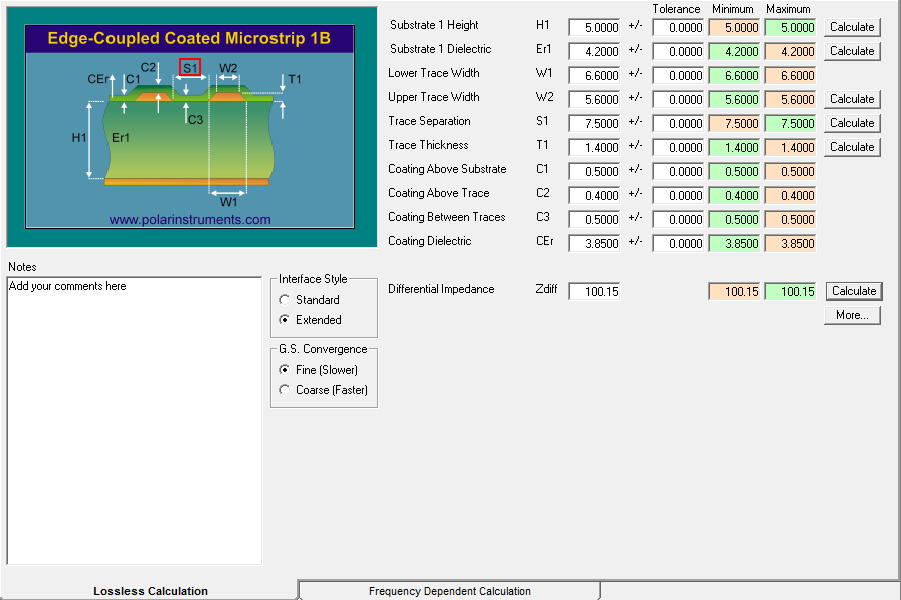

4.特性阻抗计算

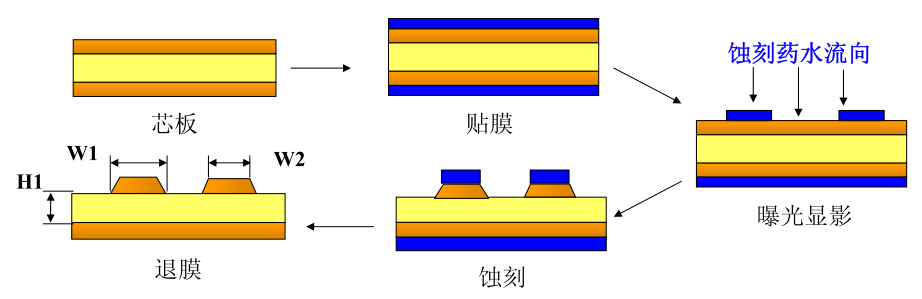

Polar-Si9000软件是大多数工程师首选的阻抗特性计算软件,该软件共提供了93种阻抗计算模式,完全满足大部分PCB板阻抗计算要求,且计算结果的准确度和精度较高。当选择不同的阻抗计算模式时,其计算公式的因子略微不同,其基本因素就是上述提到的H、S、Er、W1、W2、C1、C2、C3、CEr。线宽分为W1和W2的原因见下图3制作流程。生产中蚀刻药水对至上而下铜表面进行腐蚀,因此蚀刻出来的线宽会呈现出梯形,W1与W2的差值与铜厚相关,其差值一般为0.3-1.6mil之间,具体如下:

(1)内层:铜厚T=1oz时,W1=W2+0.5mil;铜厚T=2oz时,W1=W2+1.2mil ;

(2)外层:铜厚T=1oz时,W1=W2+1.0mil;铜厚T=2oz时,W1=W2+1.6mil ;;

(3)与板厂确认W1和W2的关系。

图3 制作流程

如下图4所示是Polar-Si9000的 Edge-Coupled Coated Microstrip 1B模式,现可确定的参数有(板材、油墨、铜厚确定后):Er1=4.2、T1=1.4mil、C1=0.5mil、C2=0.4mil、C3=0.5mil、CEr=3.85;H1设定为5mil。剩下的可调参数为(差分的线宽和线距):W1、W2、S1。此时可以尝试着先定S1,再定W1和W2,或者先定W1和W2,再定S1都可以。比如先定S1=7.5mil,然后慢慢的调整W1和W2数值,直至特性阻抗值达到预计值(Z=100oz),此时W1=6.6,W2=5.6。此时就算完成了该层100欧姆差分特性阻抗的计算,如果该层或者其它层还有特性阻抗要求,还需要按此方式去再计算,直至把整个PCB设计的特性阻抗都计算出来。

图4 差分特性阻抗100欧姆计算

浙公网安备 33010602011771号

浙公网安备 33010602011771号