汇编语言与接口技术第六章 接口基础

汇编语言与接口技术第六章 接口基础

接口是CPU与外界连接的电路,是其和外界数据交换的中转站,不仅能够协调设备间数据传输速度的不同还可以将CPU和外设独立开,让它们都能够独立发展。

接口的功能

- 数据缓冲,协调CPU和慢速外设信息传递速度的不一致,通过缓存器暂存数据和锁存器暂存数据两种方式实现。

- 执行命令,CPU会传递给接口一段控制字,由接口译码后发送给对应的外设执行

- 获取状态,外设会发给接口一段状态字,表明自身所处的工作状态,经由接口译码后会发送给CPU。之后CPU会根据外设状态判断接下来采取的指令。

- 设备选择,当外设很多时,接口可以起到译码的作用,通过翻译出的地址,找到正确的外设。

IO端口

IO端口是接口上可直接由CPU读写的寄存器。这些端口和一些控制电路组成了整个接口电路。

按照CPU对这些端口的读写能力不同,可以将端口分为三类

- 数据端口:CPU可读写,是CPU和外设数据交换的中转站。

- 状态端口:CPU只读,是外设状态字的暂存地。

- 命令端口:CPU只写,是CPU控制字的暂存地。

所以端口都可划分为以上三类。

IO端口的编址方式

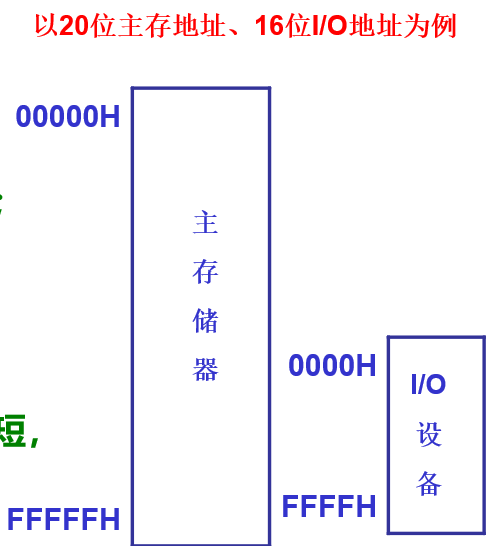

分为独立编址和统一编址两类,一般采用独立编址,即IO端口地址独立于主存储器编址。编址过程由CPU完成,不同CPU的编址方式有所不同。

控制IO端口的IN,OUT指令

IO的作用是读写数据完成外设和CPU直接的信息交换。这个过程由IN,OUT这两个指令完成。

IN,CPU读一个外设数据,格式为IN AL/AX ,PORT/DX

OUT,CPU写一个数据到外设中,格式为OUT PORT/DX ,AL/AX

PORT是IO端口的地址。

注意

当IO端口用8位地址时,可以直接用IO端口地址直接寻址

当IO端口用16位地址时,必须先将IO端口的地址置于DX中,再寄存器间接寻址。

读入或写出的数据都存在AL/AX中。

另外IN,OUT操作允许两边的操作数位数不同,因为一边是寄存器一边是地址,寻址大小由寄存器大小决定。

IO接口地址译码

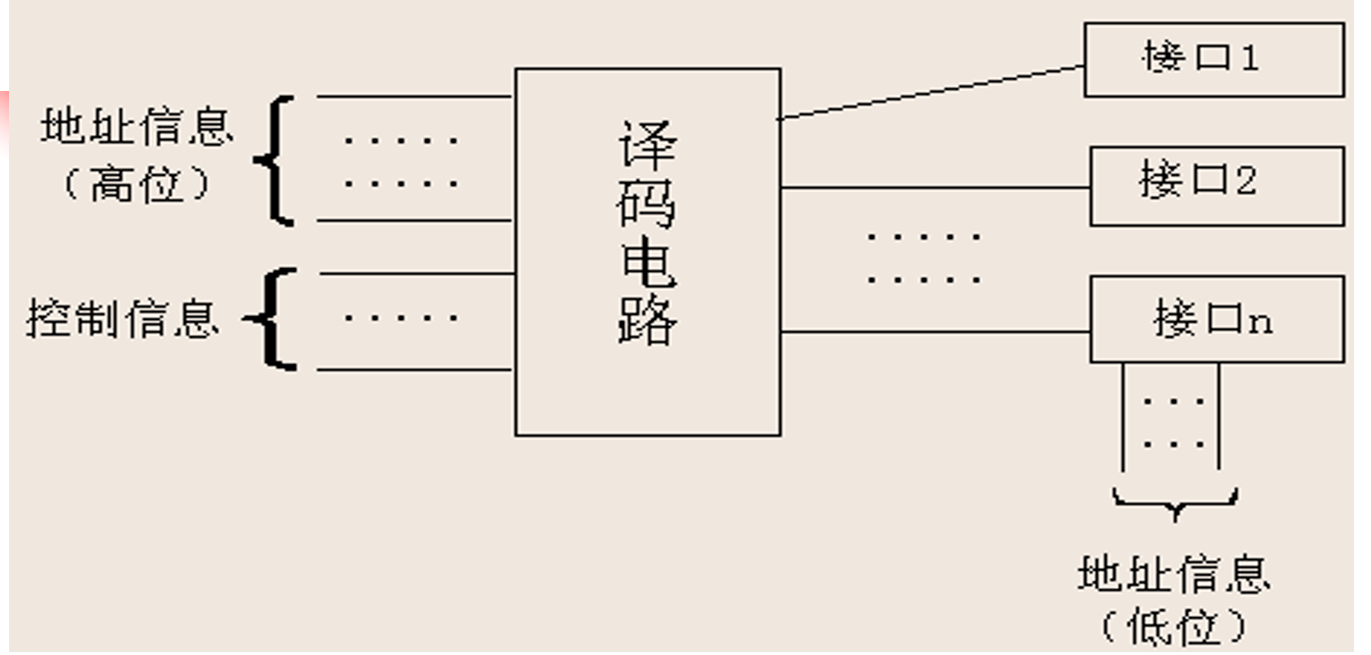

CPU与IO接口电路之间的信息交换需要找到对应的IO端口。这个过程通过一个叫译码器的东西实现。CPU在传或者读数据的过程中,会给译码器一个地址信息,这个地址信息会被划分成两部分分别——接口地址和端口地址,译码器通过接口地址完成片间译码(寻找正确IO接口的过程),之后这个IO接口处于和CPU连通的状态,再给它端口地址完成片内寻址。

译码器

译码器的输入端和CPU相连,输出端和若干IO接口相连接,CPU给它一段地址后,只有和对应接口相连接的那个输出端为信号有效其他输出端都为信号无效,从而完成片间寻址的逻辑功能。

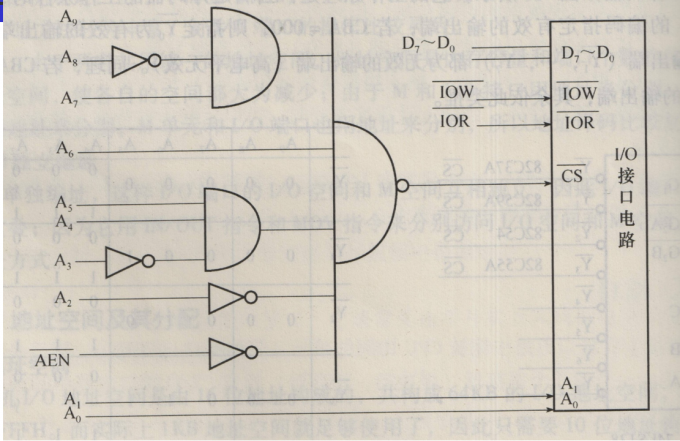

由门电路构成的固定式单端口地址译码器电路

如图高8位完成片间寻址,低2位完成片内寻址,当且仅当A2~A9是所连接的IO接口地址时输出有效电平。若干个这样的电路放在一起即可构成一个译码器。

其中D0~D7就是传输的数据。

IOW是写控制端

IOR是读控制端

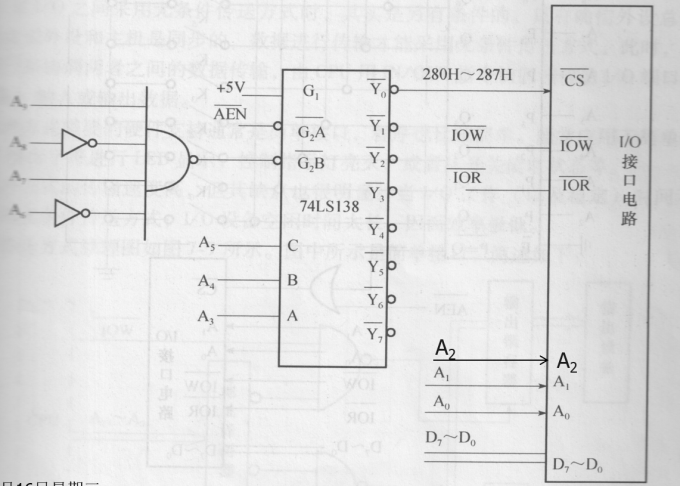

由译码器组成的固定式多端口译码器

如图,一个译码器有8个端口的选择能力。然后我们取这个地址信号高位再分组,分出部分作为译码器的选择标准,找到IO端口的大致区间,再通过剩下的由译码器找到对应的IO端口。

比如一段地址由A0A9构成,先找出管理A9A6是1010的译码器,再通过这个译码器找出地址是A5~A3的IO接口。

这个过程相当于对接口地址分块。

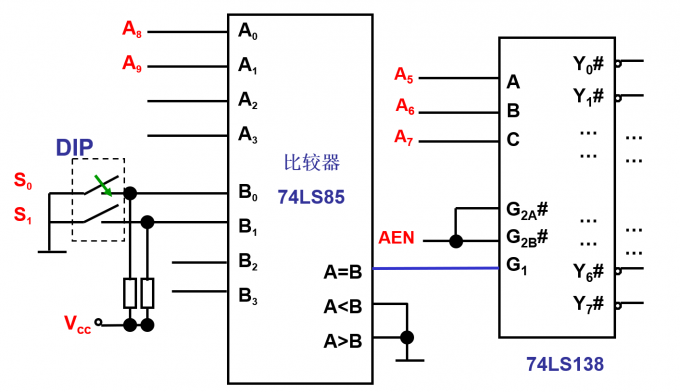

由地址开关和比较器构成的可选式多端口译码电路

S0和S1两个开关控制电平,只有A9A8 和B1B0相同时才输出有效信号,然后再由A5A6A7确定译码器所连的哪一个IO接口电路和CPU连通。

比如此时开关都断开,A9A8 = 00,假设此时的译码器Y0输出端口有效,那么此时Y0连接的接口地址就是A9A8A7A6A5 = 00000,这个接口有最多可以有32个端口。

CPU和外设之间的信息传送方式

无条件传送方式

CPU何时都可以向外设传送数据,不用等待外设,因此也不存在状态字,控制字,接口电路中只要有数据寄存器就行。但必须要求外设状态时刻保持再准备就绪状态。

程序查询传送方式

设计一段程序,控制CPU不断根据外设状态字判断外设是否处于就绪状态,如果是则传送数据如果没有就继续等待。简单来说就是CPU如何和外设有信息交换就会一直等到外设就绪,此时CPU什么也不干,因此时间效率低下。

因为要判断外设状态,所以此时的接口电路就必须有数据寄存器和状态寄存器。

中断传送方式

CPU若传送信息,就会先给外设控制字,让外设初始化并进入就绪状态,在外设准备的过程中CPU还可以处理其他任务,当外设准备就绪,会向CPU发送中断请求,CPU接受后会响应这个请求停下手头工作转而向外设传送信息。

因为CPU还要向外设接口还要有控制寄存器和中断控制电路。

浙公网安备 33010602011771号

浙公网安备 33010602011771号