汇编语言与接口技术第二章 80x86微处理器

汇编语言与接口技术第二章 80x86微处理器

8086的内部结构之寄存器

寄存器

寄存器相较于存储器有更快的存取速度且易于操作。

根据功能可以将寄存器分为通用寄存器,段寄存器,专用寄存器。

-

通用寄存器:传,存数据,可以参与逻辑运算。

MOV AX ,BX ; 传数据 MOV AX,1234H ; 存 ADD AX,BX INC AX; 参与预算并保存结果 ; BP,SP 一般用于维护站内数据 存栈指针 最经典的是在进行函数跳转时保护主程序数据不变 PUSH BP; 压入栈底 MOV BP,SP; 存原来的SP保护SP ..... ..... MOV SP,BP; 复原SP POP BP; 复原BP RET ; 推出子函数 ;可参考 :https://blog.csdn.net/bagboy_taobao_com/article/details/7370504 ; SI DI 一般在寻址时存放偏移地址。通用寄存器有AX,BX,CX,DX,SI,DI,BP,SP共八个

-

段寄存器

存放段地址的寄存器,有CS,DS,SS,ES

-

控制(专用)寄存器

IP,FLAG

其中通用寄存器又可以进一步细分

- 数据寄存器(AX,BX,CX,DX)

- 段寄存器(DS,CS)

- 指针寄存器(SP,BP)

它们更多的作用和分类参考这个,写的非常好。

为了考试,重点掌握数据寄存器和指针寄存器内容,上面博客已经足够。

FLAG标志寄存器

每一位有特定作用,用来辅助进行逻辑有运算。共9个。

| 名称 | 符号 |

|---|---|

| 溢出标志 | OF |

| 进位标志 | CF |

| 零标志 | ZF |

| 符号标志 | SF |

| 奇偶标志 | PF |

| 中断标志 | IF |

| 辅助进位标志 | AF |

| 跟踪标志 | TF |

其中前四个重点掌握之后了解即可。

溢出标志和进位标志

无符号数才有进位(CF),有符号数才有溢出(OF)。学习过半加器全加器之后,很容易明白,如果我们要计算两个16位数的和,就要把两个半加器级联起来,此时对于低八位就是所谓无符号数,如果向上进一就是往高八位进一,也就是所谓进位(CF = 1),如果高八位向上进一,就超出了16位的最大表示范围,也就是所谓的溢出(OF = 1)。这样我们把低八位看出无符号数,高八位看成有符号数也非常自然了。

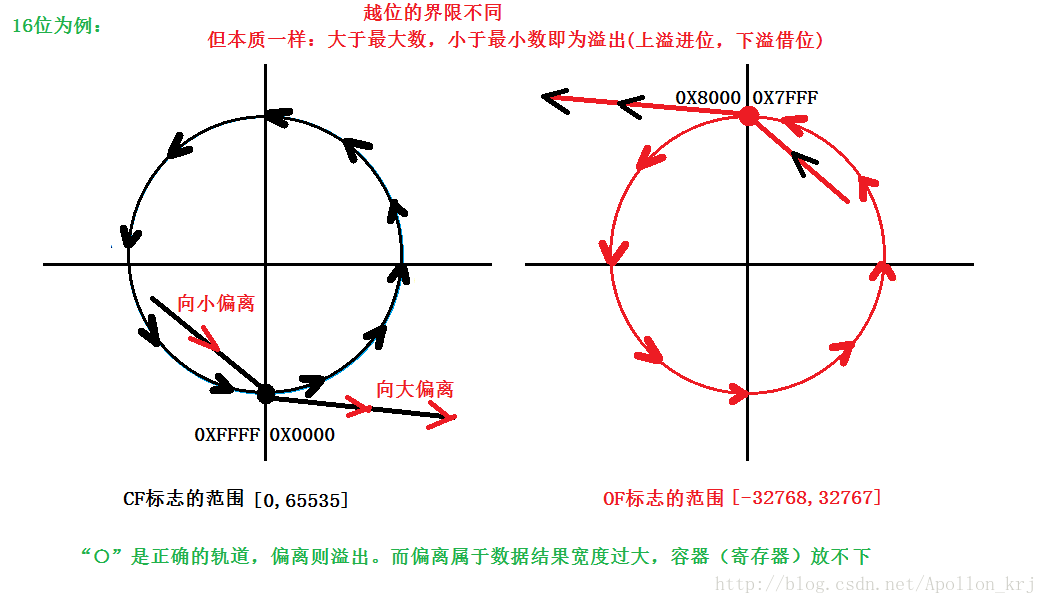

因此,它们都是根据是否超出自己应有的范围决定的。这个范围取决于是什么类型的数字,这个图表示的很明确:

总之,把两个数看成无符号数才可以判断CF,看成有符号数才可以判断OF。考试时用如下判断方法基本就够了。

以下以8位寄存器为例

判断CF:

- 把二进制数化成无符号的十进制数,求得结果,如果超出了[0,255],CF = 1

- 直接二进制计算,如果出现第九位,CF = 1

判断OF:

- 把二进制转换为有符号十进制数,如果结果超过了[-128,127],OF = 1

- 直接二进制计算,如果符号位发生改变,OF = 1

有几个简单的推论,首先CF = 1,计算结果是正确的,OF = 1计算结果是错误的,这个通过上面全加器的例子很容易明白。

其次,OF = 1,仅可能出现在这两个数都是正数或者都是负数的情况,否则根本不会超范围,OF始终为0。

之后的ZF看是否为0,SF看是否为负,PF看是否有偶数个1(用于奇偶校验)了解即可。

存储器

存储器是一段连续的区域,地址从0开始,寻址范围受到地址总线的约束,我们主要讨论的8086cpu的地址总线有20根,故而其寻址能力是$$2^{10}$$。

需要了解两个重要概念。存储单元,存储器的基本单元,大小是1字节或者1字,8086的存储的单元是1字节。物理地址,存储单元的唯一编号。

CPU与存储器的交互过程

首先来看它们之间的连接结构,CPU和存储器需要完成数据的交互,因此一根可双向传递的数据总线。CPU要存放或者取出的数据在哪一个存储单元?这由地址总线传达给存储器,要求存储器准备好对应数据。这个过程的时机,数据总线是写入还是读出,都需要控制,所以还有控制总线,

接下来看具体工作过程。

- 控制总线发出访存请求,作用是打开存储器,允许它们进行信息交互

- 地址总线发出需要的地址,由存储器经过译码,寻址后准备好数据。

- 控制总线发出读写命令,存储器接受后,进行对应的读写操作。

- 数据总线将数据传入或传出CPU。

注意:译码,寻址操作都由存储器完成。

CPU对存储器的分段管理

因为地址总线有20根,但寄存器最大也只有16位,因此对于物理地址超过0FFFFH的存储单元,就很难表示,就有了分段的方式对存储器的划分。

这只是CPU对存储器的一种管理方式,并不是物理意义上的将存储器切开,而是逻辑上的将存储器划分为若干段。

划分方式

先将存储器分若干段,再将每个段中地址赋以对应的偏移量。类似于二维数组的思想,先找到某“行”再找到某“列”。

学会它首先明确几个概念。

- 物理地址:如上所述

- 段地址:物理地址的高16位

- 偏移地址(有效地址EA):相对于段首址的偏移量。

- 逻辑地址:段地址和偏移地址的连携表示,形如DS:EA

我们可以通过,段地址 * 16 + 偏移地址 = 物理地址,的公式得到物理地址。也可以看出段地址的物理地址一定是16的倍数。

另外,如果在十六进制下乘16等价于左移1位,在二进制下等价于左移4位。

划分段特点

这一个个划分出来的逻辑段是可以重叠的。

最大的划分数量是每16个单元划分一个段,最大有\(2^{20} \div 16=2^{16}=64KB\) 个。

最小划分数量是每 \(2^{16}\) 个单元互粉一个,共16个。

同一个物理地址对应的逻辑地址是不唯一的,根据划分方式的不同而不同。

CPU的内部结构和工作时序

了解性内容,包括8086的40个引脚作用,最大最小模式,最小模式下的读写时序等,有时间的话单开一篇总结。

浙公网安备 33010602011771号

浙公网安备 33010602011771号