【操作系统-内存】地址翻译流程图

地址翻译流程图

简略版:

stateDiagram-v2

state if_state <>

CPU产生VA --> 访问TLB

访问TLB --> 转VA并访问Cache: 命中

访问TLB --> 访问页表: 缺失

访问页表 --> 转VA并访问Cache: 命中

访问页表 --> 缺页处理: 缺失

缺页处理 --> 访问TLB: 重新执行

转VA并访问Cache --> 读取Cache数据: 命中

转VA并访问Cache --> 访问内存数据: 缺失

完整版:(注意,TLB和Cache是组相联的)

stateDiagram-v2

state if_state <>

CPU产生VA(VA=页号+页内偏移量) --> 访问PTR(获取页表长度)

访问PTR(获取页表长度) --> 访问TLB(页号=TLB标记+TLB组号): 页号 < 页表长度

访问PTR(获取页表长度) --> 越界中断: 页号 ≥ 页表长度

访问TLB(页号=TLB标记+TLB组号) --> 访问页表(页表项PA=页表起始PA+页号×页表项长度): 缺失,访问PTR(获取页表起始PA)

访问TLB(页号=TLB标记+TLB组号) --> 读取页框号: 命中

访问页表(页表项PA=页表起始PA+页号×页表项长度) --> 缺页中断处理:缺失

访问页表(页表项PA=页表起始PA+页号×页表项长度) --> 读取页框号,修改TLB:命中

state 缺页中断处理{

[*] --> 外存找到缺页

外存找到缺页 --> 内存是否已满

内存是否已满 --> 页面置换: 是

内存是否已满 --> 该页换入内存: 否

页面置换 --> 该页换入内存

该页换入内存 --> 修改页表

state 页面置换{

[*] --> 选择一页换出

选择一页换出 --> 该页是否被修改过

该页是否被修改过 --> 该页写入外存:是

该页是否被修改过 --> [*]:否

该页写入外存 --> [*]

}

修改页表 --> [*]

}

缺页中断处理 --> 修改TLB

读取页框号 --> CPU获得PA(PA=页框号+页内偏移量)

读取页框号,修改TLB --> CPU获得PA(PA=页框号+页内偏移量)

修改TLB --> 访问TLB(页号=TLB标记+TLB组号): 重新执行被中断指令

CPU获得PA(PA=页框号+页内偏移量) --> 访问Cache(PA=Cache标记+Cache组号+块内偏移量)

访问Cache(PA=Cache标记+Cache组号+块内偏移量)--> 读取数据: 命中

访问Cache(PA=Cache标记+Cache组号+块内偏移量)--> 访问内存: 缺失

访问内存 --> Cache已满?

Cache已满? --> 替换算法: 是

Cache已满? --> 写入新行: 否

替换算法 --> 读取数据

写入新行 --> 读取数据

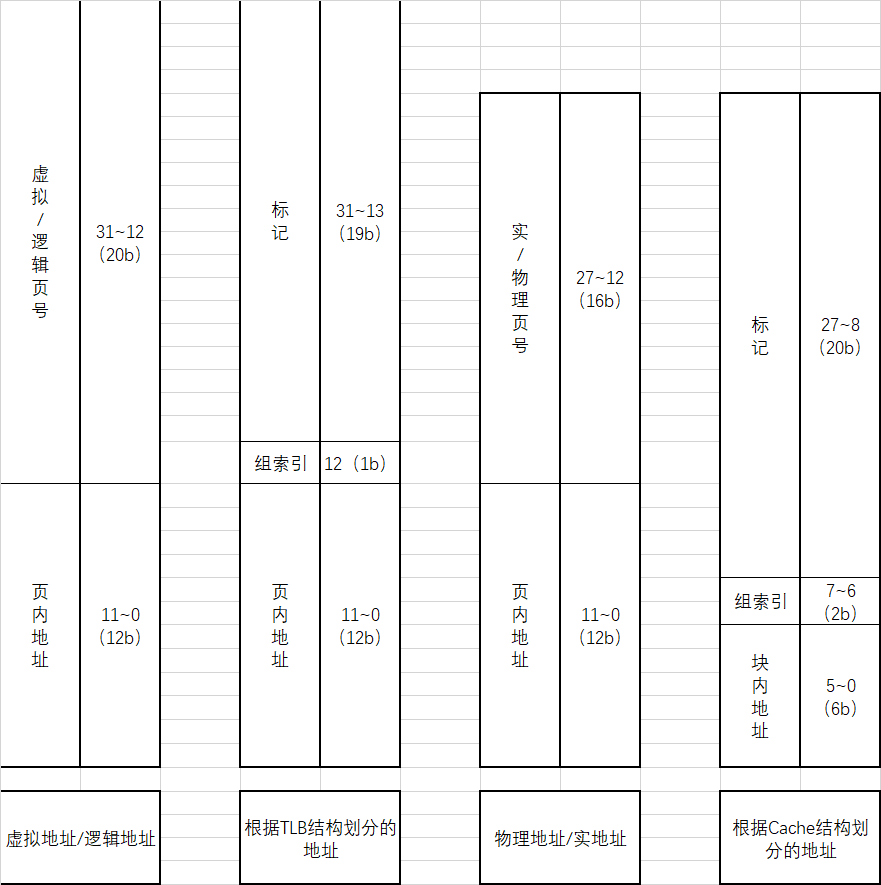

一级分页存储系统

- 字节编址

- 一页为 4KB

- 逻辑地址空间为 32 位(4GB)

- 物理地址空间为 28 位(256MB)

- 页表项长度为 4B

- TLB为八路组相联,一共16行(组数=16/8=2)

- Cache为四路组相联,一共16行(组数=16/4=4),Cache行大小为64B

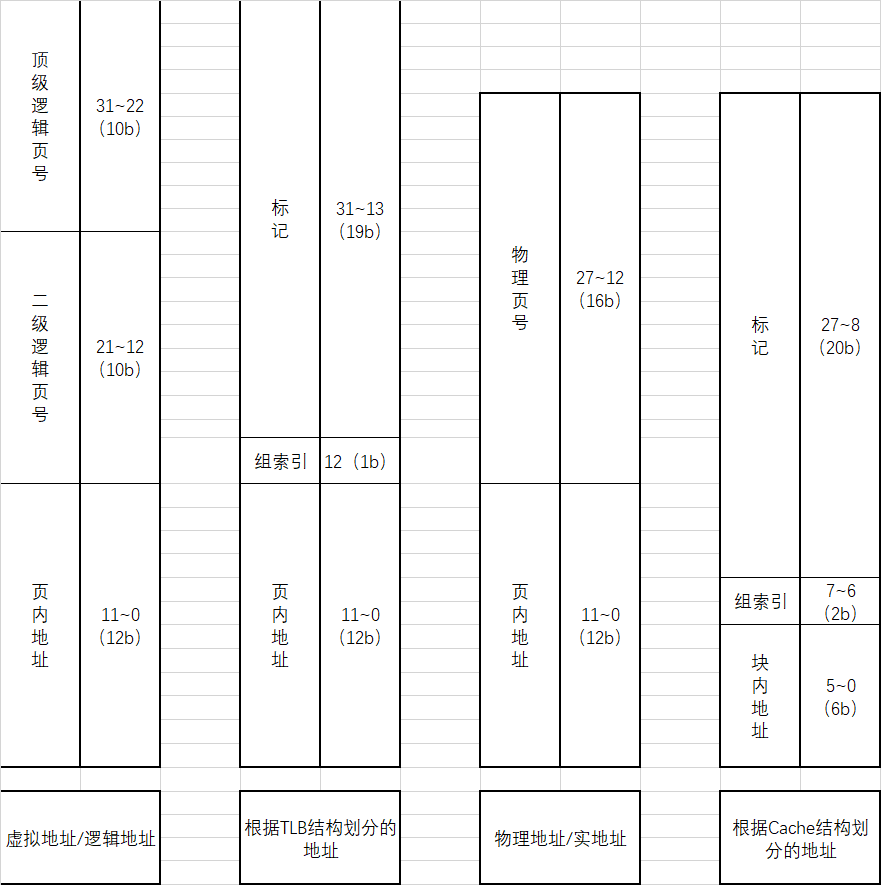

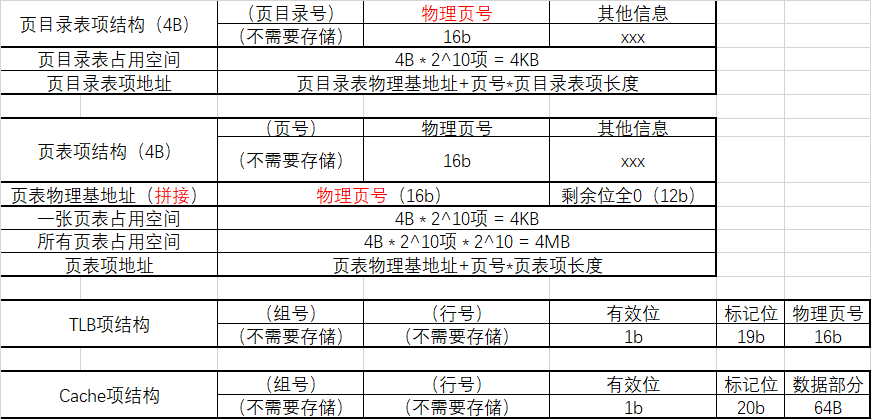

二级分页存储系统

- 字节编址

- 一页为 4KB

- 逻辑地址空间为 32 位(4GB)

- 物理地址空间为 28 位(256MB)

- 页表项长度为 4B

- 规定页目录表只占一页

- TLB为八路组相联,一共16行(组数=16/8=2)

- Cache为四路组相联,一共16行(组数=16/4=4),Cache行大小为64B

浙公网安备 33010602011771号

浙公网安备 33010602011771号