【组成原理-处理器】微程序控制器

1 易混淆的几个概念

- 微操作:一条机器指令可分解为多条微操作。

- 微命令:控制部件向执行部件发出的控制命令。这些命令导致执行部件执行微操作。

微命令和微操作是一一对应的:微命令是微操作的控制信号,微操作是微命令的执行过程。

- 微指令:若干微命令的集合。

- 微程序:若干微指令的集合。

粒度大小:微命令&微操作 < 微指令 < 微程序

- 微周期:从控制存储器(CM)读取一条微指令并执行相应微操作所需的时间。

2 微指令的设计

2.1 水平型微指令

水平型微指令:一条微指令能定义多个可并行的微命令。

(1)优缺点:

- 优点:微程序短,执行速度快。

- 缺点:微指令长,编写微程序较麻烦。

(2)格式:

| 操作控制(微操作码) | 顺序控制(微地址码/下地址) | 顺序控制(微地址码/下地址) |

|---|---|---|

| A1, A2, A3,...,An | 判断测试字段 | 后继地址字段 |

下面来讨论水平型微指令的编码方式。

2.1.1 直接编码(直接控制)方式

在微指令的操作控制字段中,每一位代表一个微操作命令,某位为“1”表示该控制信号有效。

(1)格式:

| 操作控制(控制信号) | 下地址 |

|---|---|

| 1 0 1 0 0 ... 0 1 | ~ |

(2)优缺点:

- 优点:简单、直观,执行速度快,操作并行性好。

- 缺点:微指令字长过长,n 个微命令就要求微指令的操作字段有 n 位,造成控存容量极大。

2.1.2 字段直接编码方式

将微指令的控制字段分成若干“段”,每段经译码后发出控制信号。

(0)两个概念:

- 相容性微命令:可以并行完成的微命令。

- 互斥性微命令:不允许并行完成的微命令。

(1)原则:

- 互斥性微命令位于同一段内,相容性微命令位于不同段内。

- 每个小段中包含的信息位不能太多。

- 每个小段需留出一个状态,表示本字段不发出任何微命令。通常用 000 表示不操作。

例:当某字段的长度为 3 位时,最多只能表示 7 个互斥的微命令,用 000 表示不操作。

(2)格式:

| 操作控制 1 | 操作控制 2 | 操作控制 3 | 操作控制 4 | 下地址 |

|---|---|---|---|---|

| 1 0 1 | 0 0 1 | 1 0 0 | 0 1 0 | ~ |

(3)优缺点:

- 优点:可以缩短微指令字长。

- 缺点:要通过译码电路后再发出微命令,因此比直接编码方式慢。

相关例题

【例】某计算机的控制器采用微程序控制方式,微程序中操作控制字段采用字段直接编码法,共有 33 个微命令,构成 5 个互斥类,分别包含 7、3、12、5 和 6 个微命令。问一共需要几位操作控制位?

【解】这 5 个互斥类实际包含的状态数为 8、4、13、6 和 7 个,因为 8 = 23, 4 = 22, 13 < 24, 6 < 23, 7 < 23,所以需要的位数分别为 3,2,4,3,3,操作控制位一共需要 3+2+4+3+3=15 位。

2.1.3 字段间接编码方式

一个字段的某些微命令需由另一个字段中的某些微命令来解释,由于不是靠字段直接译码发出的微命令,故称为字段间接编码,又称隐式编码。

优缺点:

- 优点:可进一步缩短微指令字长。

- 缺点:削弱了微指令的并行控制能力,故通常作为字段直接编码方式的一种辅助手段。

2.2 垂直型微指令

垂直型微指令:一条微指令只能定义一个微命令,由微操作码字段规定具体功能。

(1)优缺点:

- 优点:微指令短、简单、规整,便于编写微程序。

- 缺点:微程序长,执行速度慢,工作效率低。

(2)格式:

| 微操作码 | 目的地址 | 源地址 |

|---|---|---|

| uOP | Rd | Rs |

2.3 混合型微指令

混合型微指令:在垂直型的基础上增加一些不太复杂的并行操作。微指令较短,仍便于编写;微程序也不长,执行速度加快。

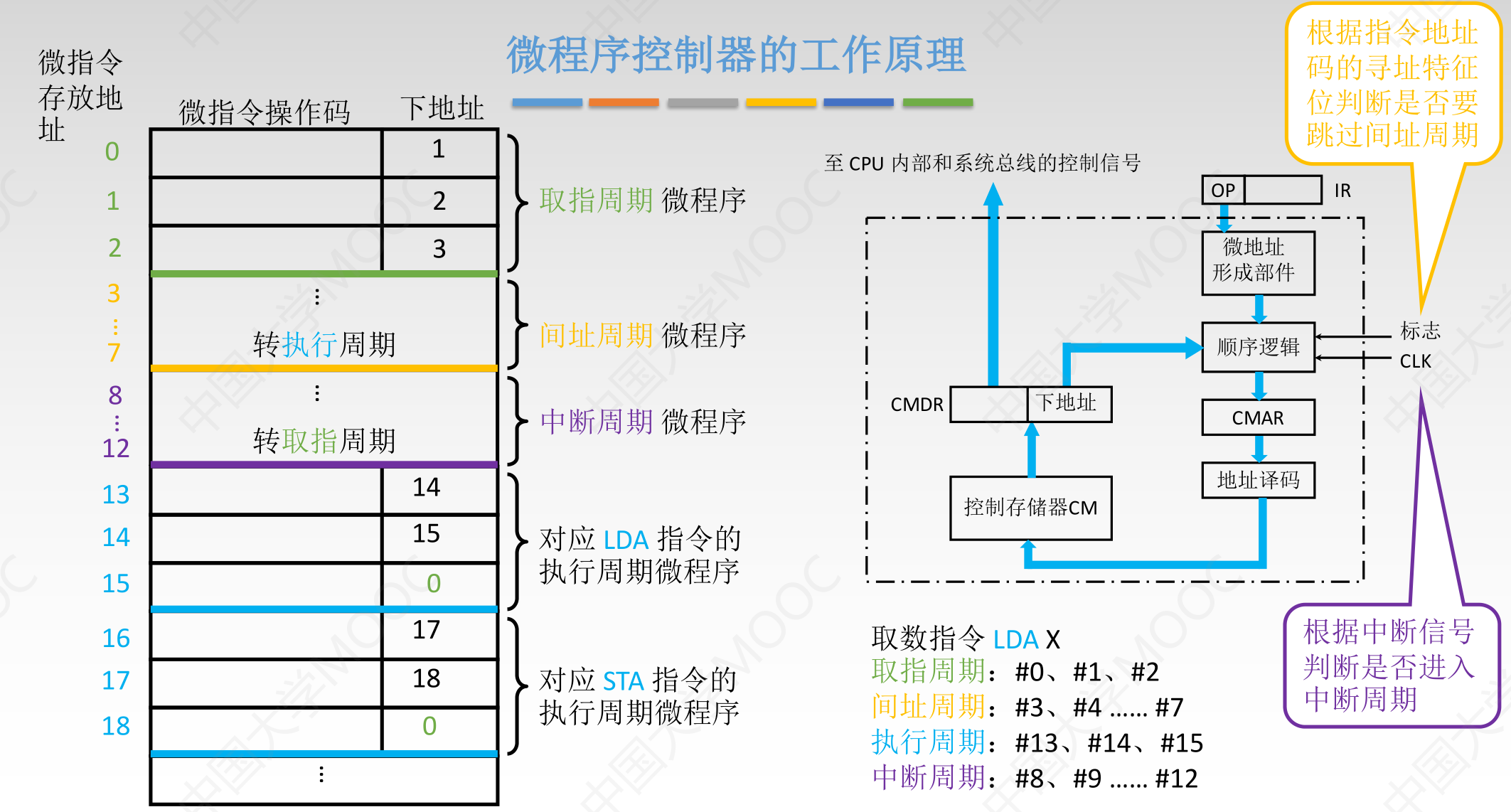

3 微程序控制器的工作原理

3.1 微程序控制器的组成

- 微地址形成部件:产生初始微地址和后继微地址,以保证微指令的连续执行。

- 控制存储器(CM):用于存放各指令对应的微程序,控制存储器可用只读存储器 ROM 构成。

- 微地址寄存器(CMAR,uPC):又称为微指令计数器,用于存放控制存储器(CM)的下一条微指令的地址。

- 微指令寄存器(CMDR,uIR):用于存放从控制存储器(CM)中读出的微指令。

控制存储器(CM)怎样存储微指令?

- 取指周期微程序:通常是公用的,故如果某指令系统中有 n 条机器指令,则 CM 中微程序的个数至少是 n+1 个。

- 间址周期微程序、中断周期微程序:一些早期的 CPU、物联网设备的 CPU 可以不提供间接寻址和中断功能,因此这类 CPU 可以不包含间址周期、中断周期的微程序段。

- 执行周期:不同指令的执行周期微程序。

【注意】物理上,取指周期、执行周期看起来像是两个微程序,但逻辑上应该把它们看作一个整体。因此,一般我们认为“一条指令对应一个微程序”!

相关例题

【例 1】某带中断的计算机指令系统共有 101 种操作,采用微程序控制方式时,控制存储器中相应最少有几个微程序?

【解】取指周期微程序 1 个,中断周期微程序 1 个,执行周期微程序 101 个,一共 103 个微程序。

【例 2】通常情况下,一个微程序的周期对应一个( )

A. 指令周期

B. 主频周期

C. 机器周期

D. 工作周期

【解】如果将“一个微程序”理解为“一个周期的微程序”,则对应的周期应为机器周期,选 C;而如果将“一个微程序”理解为“一条指令的微程序”,即上文所述的,通常情况下,“一条指令对应一个微程序”,则对应的周期应为指令周期,选 A,可见此题有歧义。不过幸运的是,统考一般不会出现这种带有歧义性的题目,但是一旦出现了,最好还是选 A。

3.2 微指令的地址形成

- 微指令的下地址字段指出:微指令格式中设置一个下地址字段,由微指令的下地址字段直接指出后继微指令的地址,这种方式又称为断定方式。

- 根据机器指令的操作码形成:当机器指令取至指令寄存器后,微指令的地址由操作码经微地址形成部件形成。

- 增量计数器:(CMAR) + 1 --> CMAR

- 分支转移

- 测试网络

- 由硬件产生微程序入口地址

相关例题

【例】某计算机采用微程序控制器,共有 32 条指令,公共的取指令微程序包含 2 条微指令,各指令对应的微程序平均由 4 条微指令组成,采用断定法(下地址字段法) 确定下条微指令地址,则微指令中下地址字段的位数至少是?

【解】一共有 32 条指令,每条指令的执行周期微程序有 4 条微指令,则一共有 32*4 = 128 条微指令,再加上公共的取指令微程序包含 2 条微指令,则总共为 128+2 = 130 条微指令。因为 130 < 28=256,所以下地址字段的位数至少有 8 位。

4 微程序的设计

4.1 取指周期的微程序

取指周期的微操作分析:

| 微操作 | 描述 |

|---|---|

| (PC)-->MAR | 指令对应的地址放入 MAR 中 |

| 1-->R | 允许读主存 |

| M(MAR)-->MDR | 从主存的相应地址读出指令并存入 MDR 中 |

| (PC)+1-->PC | 程序计数器加 1 个指令字长 |

| (MDR)-->IR | MDR 存储的指令放入 IR 中 |

| OP(IR)-->微地址形成部件 | 指令的操作码送入微地址形成部件进行译码 |

| 微地址形成部件-->CMAR | 根据指令操作码确定该指令的执行(或间址)周期微程序的首地址 |

因此,取指周期的微程序可以由以下几个微指令组成:

| 微指令条数 | 微操作 | 描述 |

|---|---|---|

| 1 | (PC)-->MAR | 指令对应的地址放入 MAR 中 |

| 1 | 1-->R | 允许读主存 |

| ~ | Ad(CMDR)-->CMAR | 读取当前指令的下地址字段,并存放在 CMAR 中,这样就能确定下一条微指令的地址 |

| 2 | M(MAR)-->MDR | 从主存的相应地址读出指令并存入 MDR 中 |

| 2 | (PC)+1-->PC | 程序计数器加 1 个指令字长 |

| ~ | Ad(CMDR)-->CMAR | 读取当前指令的下地址字段,并存放在 CMAR 中,这样就能确定下一条微指令的地址 |

| 3 | (MDR)-->IR | MDR 存储的指令放入 IR 中 |

| 3 | OP(IR)-->微地址形成部件 | 指令的操作码送入微地址形成部件进行译码 |

| ~ | 微地址形成部件-->CMAR | 根据指令操作码确定该指令的执行(或间址)周期微程序的首地址 |

4.2 间址周期的微程序

4.2.1 间接寻址

间址周期的微操作分析:

| 微操作 | 描述 |

|---|---|

| Ad(IR)-->MAR | 读出指令的地址码部分,送入 MAR 中 |

| 1-->R | 允许读主存 |

| M(MAR)-->MDR | 从主存的相应地址读出数据并存入 MDR 中 |

| (MDR)-->Y | MDR 存储的数据放入暂存输入寄存器 Y 中 |

因此,该指令的间址周期的微程序可以由以下几个微指令组成:

| 微指令条数 | 微操作 | 描述 |

|---|---|---|

| 1 | Ad(IR)-->MAR | 读出指令的地址码部分,送入 MAR 中 |

| 1 | 1-->R | 允许读主存 |

| ~ | Ad(CMDR)-->CMAR | 读取当前指令的下地址字段,并存放在 CMAR 中,这样就能确定下一条微指令的地址 |

| 2 | M(MAR)-->MDR | 从主存的相应地址读出数据并存入 MDR 中 |

| ~ | Ad(CMDR)-->CMAR | 读取当前指令的下地址字段,并存放在 CMAR 中,这样就能确定下一条微指令的地址 |

| 3 | (MDR)-->Y | MDR 存储的数据放入暂存输入寄存器 Y 中 |

| ~ | Ad(CMDR)-->CMAR | 读取当前指令的下地址字段(此时该字段应为执行周期微程序的首地址),并存放在 CMAR |

4.2.2 寄存器间接寻址

间址周期的微操作分析:

| 功能 | 描述 |

|---|---|

| (R0)-->MAR | 读出 R0 的数据,送入 MAR 中 |

| 1-->R | 允许读主存 |

| M(MAR)-->MDR | 从主存的相应地址读出数据并存入 MDR 中 |

| (MDR)-->Y | MDR 存储的数据放入暂存输入寄存器 Y 中 |

因此,该指令的间址周期的微程序可以由以下几个微指令组成:

| 微指令条数 | 微操作 | 描述 |

|---|---|---|

| 1 | (R0)-->MAR | 读出 R0 的数据,送入 MAR 中 |

| 1 | 1-->R | 允许读主存 |

| ~ | Ad(CMDR)-->CMAR | 读取当前指令的下地址字段,并存放在 CMAR |

| 2 | M(MAR)-->MDR | 从主存的相应地址读出数据并存入 MDR 中 |

| ~ | Ad(CMDR)-->CMAR | 读取当前指令的下地址字段,并存放在 CMAR |

| 3 | (MDR)-->Y | MDR 存储的数据放入暂存输入寄存器 Y 中 |

| ~ | Ad(CMDR)-->CMAR | 读取当前指令的下地址字段(此时该字段应为执行周期微程序的首地址),并存放在 CMAR |

4.3 执行周期的微程序

以ADD (R0), R1为例,功能为((R0))+(R1)-->(R0),说明执行周期的微程序。

执行周期的微操作分析:

| 微操作 | 描述 |

|---|---|

| (Y)+(R1)-->Z | Y 中数据和 R1 中数据相加,经过 ALU 计算的结果存入 Z 中 |

| (Z)-->MDR | 将计算结果放入 MDR 中 |

| 1-->W | 允许写主存 |

| (MDR)-->M(MAR) | 将 MDR 数据放入到主存相应地址中,注意此时 MAR 仍存储着 R0 的数据 |

因此,该指令的执行周期的微程序可以由以下几个微指令组成:

| 微指令条数 | 微操作 | 描述 |

|---|---|---|

| 1 | (Y)+(R1)-->Z | Y 中数据和 R1 中数据相加,经过 ALU 计算的结果存入 Z 中 |

| ~ | Ad(CMDR)-->CMAR | 读取当前指令的下地址字段,并存放在 CMAR 中,这样就能确定下一条微指令的地址 |

| 2 | (Z)-->MDR | 将计算结果放入 MDR 中 |

| 2 | 1-->W | 允许写主存 |

| ~ | Ad(CMDR)-->CMAR | 读取当前指令的下地址字段,并存放在 CMAR 中,这样就能确定下一条微指令的地址 |

| 3 | (MDR)-->M(MAR) | 将 MDR 数据放入到主存相应地址中,注意此时 MAR 仍存储着 R0 的数据 |

| ~ | Ad(CMDR)-->CMAR | 读取当前指令的下地址字段(此时该字段应为取指周期微程序的首地址),并存放在 CMAR |

5 综合例题

例 1

【例 1】假设某机器有 80 条指令,平均每条指令由 4 条微指令组成,其中有一条取指微指令是所有指令公用的。微指令长度为 32 位,请估算控制存储器 CM 的容量。

【解】平均每条指令由 4 条微指令组成,其中有一条取指微指令是所有指令公用的,那么剩余的 3 条指令则是执行周期的指令,所以执行周期微指令一共有 80*3 = 240 条,再加上取指周期的微指令,CM 一共存储 240+1 = 241 条微指令。

考虑微指令的格式,因为 241 < 28=256,所以下地址位数至少有 8 位。因此,CM 的存储单元个数有 256 个,每个存储单元存放一个 32 位的微指令,则 CM 容量为 32b*256。

例 2

【例 2】某微程序控制器中,微指令采用水平型格式、长度为 26 位,操作控制字段采用字段直接编码法,共 5 组,每组共有 5 个、8 个、15 个、27 个、3 个微命令;顺序控制字段采用下址法 + 测试网络法(断定法),测试网络有 2 种外部测试条件。

(1)请设计该微程序控制器的微指令格式。

(2)控制存储器 CM 的容量最大应为多少?

【解】(1)操作控制字段采用字段直接编码法,共 5 组,每组共有 5 个、8 个、15 个、27 个、3 个微命令,则状态数分别为 6,9,16,28,4,因为 6 < 23, 9 < 24, 16 = 24, 28 = 25, 4 = 2^2,所以需要的位数为3,4,4,5,2,操作控制位一共 3+4+4+5+2=18 位。

测试条件有 2 种,因此测试字段占 2 位。剩余的下地址位数 26-18-2=6 位。

(2)下地址位数为 6,则 CM 存储单元个数为 26=64,容量为 26b*64。

| 操作控制(微操作码) | 顺序控制(判断测试字段) | 顺序控制(后继地址字段) |

|---|---|---|

| 18b | 2b | 6b |

例 3

【例 3】某微程序控制器中,采用水平型直接控制(编码)方式微指令格式,后继微指令地址由微指令的下地址字段给出。已知机器共有 28 个微命令、6 个互斥的可判定的外部条件,控制存储器的容量为 512 × 40 位。设计其微指令格式。

【解】CM 容量为 512 × 40 位,说明微指令字长为 40 位,下地址需要 9 位(512 = 29)。6 个可判定的外部条件,且互斥,说明微指令的判断字段需要 3 位(6 < 23),这样控制字段需要 40-9-3=28 位。

| 操作控制(微操作码) | 顺序控制(判断测试字段) | 顺序控制(后继地址字段) |

|---|---|---|

| 28b | 3b | 9b |

例 4

【例 4】某机共有 52 个微操作控制信号,构成 5 个相斥类的微命令组,各组分别包含 5、8、2、15、22 个微命令。已知可判定的外部条件有两个,微指令字长 28 位。

(1)请设计该微程序控制器的微指令格式。

(2)控制存储器 CM 的容量最大应为多少?

【解】(1)有 5 个相斥类的微命令组,各组分别包含 5、8、2、15、22 个微命令,则各组的状态数为 6,9,3,16,22,因为 6 < 23, 9 < 24, 3 < 2^2, 16 = 24, 22 < 25,所以控制位需要 3+4+2+4+5=18 位。

可判定的外部条件有两个,则判断位数需要 2 位。剩余的下地址位需要 28-2-18=8 位。

(2)CM 所需的容量为 28*28 = 256*28b。

| 操作控制(微操作码) | 顺序控制(判断测试字段) | 顺序控制(后继地址字段) |

|---|---|---|

| 18b | 2b | 8b |

例 5

【例 5】有指令STA X(X 为主存地址)。

(1)若采用硬布线控制器,写出全部的微操作命令。

(2)若采用微程序控制器,写出全部的微指令。

【解】

(1)若采用硬布线控制器,写出全部的微操作命令。

- 取指周期:

| 微操作 | 控制信号 |

|---|---|

| (PC)-->MAR | PCout, MARin |

| 1-->R | 无 |

| M(MAR)-->MDR | MDRinE |

| (PC)+1-->PC | PC+1 |

| (MDR)-->IR | MDRout, IRin |

| OP(IR)-->ID | 无 |

- 间址周期:

| 微操作 | 控制信号 |

|---|---|

| Ad(IR)-->MAR | MARin |

| 1-->W | 无 |

| ACC-->MDR | ACCout, MDRin |

| MDR-->M(MAR) | MDRout |

- 无执行周期。

(2)若采用微程序控制器,写出全部的微指令。

- 取指周期:

| 微指令条数 | 微操作 |

|---|---|

| 1 | (PC)-->MAR |

| 1 | 1-->R |

| ~ | Ad(CMDR)-->CMAR |

| 2 | M(MAR)-->MDR |

| 2 | (PC)+1-->PC |

| ~ | Ad(CMDR)-->CMAR |

| 3 | (MDR)-->IR |

| ~ | OP(IR)-->CMAR |

- 间址周期:

| 微指令条数 | 微操作 |

|---|---|

| 1 | Ad(IR)-->MAR |

| 1 | 1-->W |

| ~ | Ad(CMDR)-->CMAR |

| 2 | ACC-->MDR |

| ~ | Ad(CMDR)-->CMAR |

| 3 | MDR-->M(MAR) |

| ~ | Ad(CMDR)-->CMAR |

- 无执行周期。

浙公网安备 33010602011771号

浙公网安备 33010602011771号