HDLBits Verilog(1)——Basic Gates

- ----- 44. Wire -----

- ----- 45. GND -----

- ----- 46. NOR -----

- ----- 47. Another gate -----

- ----- 48. Two gates -----

- ----- 49. More logic gates -----

- ----- 50. Chip 7420 -----

- ----- 51. Truth tables -----

- ----- 52. Two-bit equality -----

- ----- 53. Simple circuit A -----

- ----- 54. Simple circuit B -----

- ----- 55. Combine circuits A and B -----

- ----- 56. Ring or vibrate? -----

- ----- 57. Thermostat -----

- ----- 58. 3-bit population count -----

- ----- 59. Gates and vectors -----

- ----- 60. Even longer vectors -----

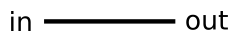

----- 44. Wire -----

Problem Statement

Implement the following circuit:

Answer

module top_module (

input in,

output out);

assign out = in;

endmodule

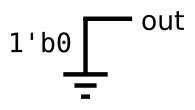

----- 45. GND -----

Problem Statement

Implement the following circuit:

Answer

module top_module (

output out);

assign out = 1'b0;

endmodule

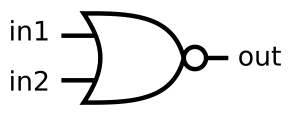

----- 46. NOR -----

Problem Statement

Implement the following circuit:

Answer

module top_module (

input in1,

input in2,

output out);

assign out = ~(in1 | in2);

endmodule

----- 47. Another gate -----

Problem Statement

Implement the following circuit:

Answer

module top_module (

input in1,

input in2,

output out);

assign out = in1 & (~in2);

endmodule

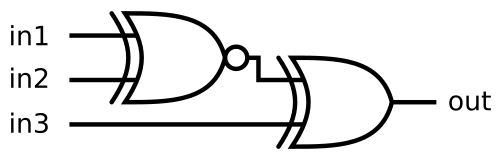

----- 48. Two gates -----

Problem Statement

Implement the following circuit:

Answer

module top_module (

input in1,

input in2,

input in3,

output out);

wire io;

assign io = in1 ^~ in2;

assign out = io ^ in3;

endmodule

----- 49. More logic gates -----

Problem Statement

Ok, let's try building several logic gates at the same time. Build a combinational circuit with two inputs, a and b.

There are 7 outputs, each with a logic gate driving it:

- out_and: a and b (与门)

- out_or: a or b (或门)

- out_xor: a xor b (异或门)

- out_nand: a nand b (与非门)

- out_nor: a nor b (或非门)

- out_xnor: a xnor b (异或非门/同或门)

- out_anotb: a and-not b (与门,其中输入b经过反转)

Expected solution length: Around 7 lines.

Answer

module top_module(

input a, b,

output out_and,

output out_or,

output out_xor,

output out_nand,

output out_nor,

output out_xnor,

output out_anotb

);

assign out_and = a & b;

assign out_or = a | b;

assign out_xor = a ^ b;

assign out_nand = ~(a & b);

assign out_nor = ~(a | b);

assign out_xnor = a ^~ b;

assign out_anotb = a & (~b);

endmodule

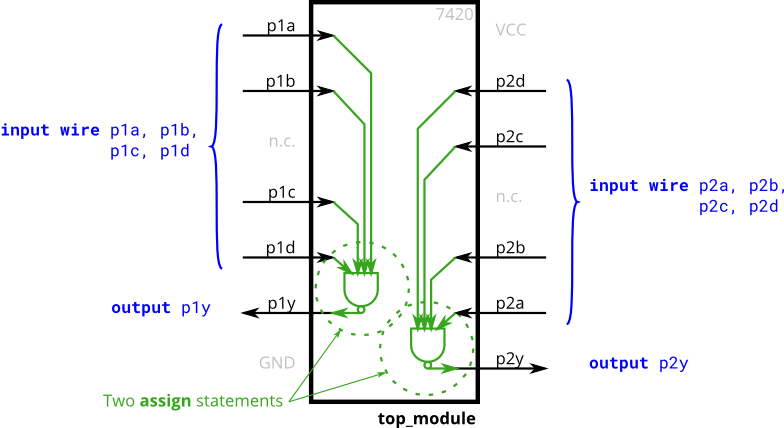

----- 50. Chip 7420 -----

Problem Statement

The 7400-series integrated circuits are a series of digital chips with a few gates each. The 7420 is a chip with two 4-input NAND gates.

Create a module with the same functionality as the 7420 chip. It has 8 inputs and 2 outputs.

Expected solution length: Around 2 lines.

Answer

module top_module (

input p1a, p1b, p1c, p1d,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

assign p1y = ~(p1a & p1b & p1c & p1d);

assign p2y = ~(p2a & p2b & p2c & p2d);

endmodule

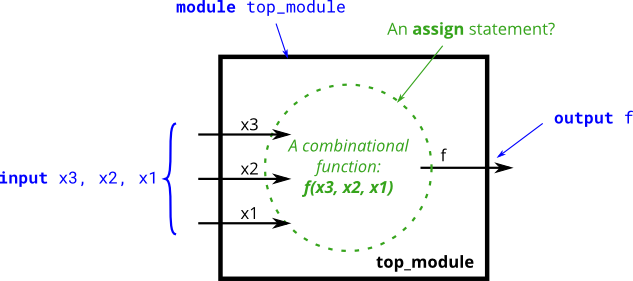

----- 51. Truth tables -----

Problem Statement

| Row number | Input: x3 x2 x1 | Output: f |

|---|---|---|

| 0 | 0 0 0 | 0 |

| 1 | 0 0 1 | 0 |

| 2 | 0 1 0 | 1 |

| 3 | 0 1 1 | 1 |

| 4 | 1 0 0 | 0 |

| 5 | 1 0 1 | 1 |

| 6 | 1 1 0 | 0 |

| 7 | 1 1 1 | 1 |

Create a combinational circuit that implements the above truth table.

Expected solution length: Around 1 line.

Answer

module top_module(

input x3,

input x2,

input x1, // three inputs

output f // one output

);

assign f = ( ~x3 & x2 & ~x1) | ( ~x3 & x2 & x1) | ( x3 & ~x2 & x1) | ( x3 & x2 & x1);

endmodule

----- 52. Two-bit equality -----

Problem Statement

Create a circuit that has two 2-bit inputs A[1:0] and B[1:0], and produces an output z. The value of z should be 1 if A = B, otherwise z should be 0.

Answer

module top_module ( input [1:0] A, input [1:0] B, output z );

assign z = (A[1] ^~ B[1]) & (A[0] ^~ B[0]);

endmodule

----- 53. Simple circuit A -----

Problem Statement

Module A is supposed to implement the function z = (x^y) & x. Implement this module.

Answer

module top_module (input x, input y, output z);

assign z = (x ^ y) & x;

endmodule

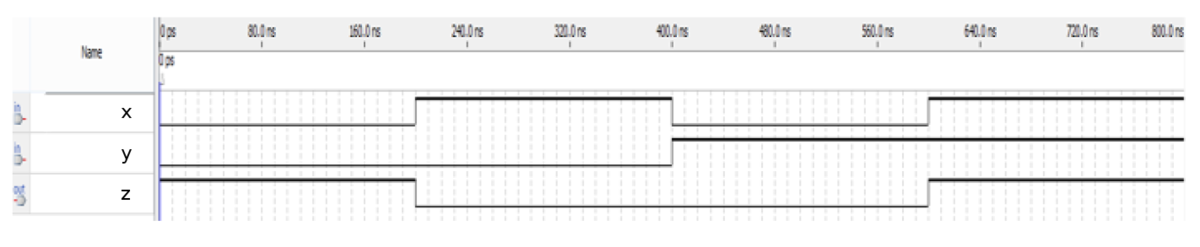

----- 54. Simple circuit B -----

Problem Statement

Circuit B can be described by the following simulation waveform:

Implement this circuit.

Answer

module top_module ( input x, input y, output z );

assign z = x ^~ y;

endmodule

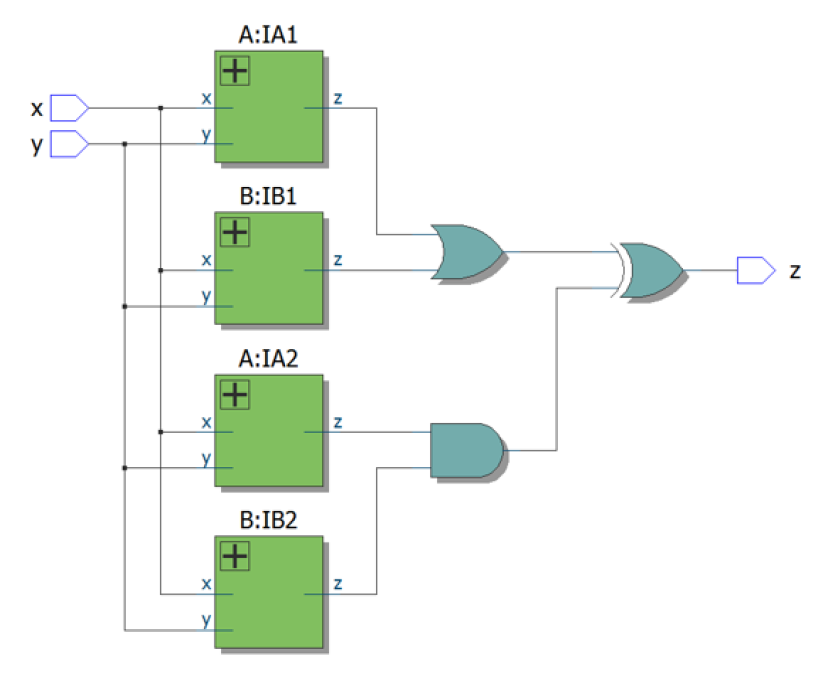

----- 55. Combine circuits A and B -----

Problem Statement

The top-level design consists of two instantiations each of subcircuits A and B, as shown below.

Answer

module top_module (input x, input y, output z);

wire io1, io2, io3, io4, io5, io6;

A instanceA1(.x(x), .y(y), .z(io1));

B instanceB1(.x(x), .y(y), .z(io2));

A instanceA2(.x(x), .y(y), .z(io3));

B instanceB2(.x(x), .y(y), .z(io4));

assign io5 = io1 | io2;

assign io6 = io3 & io4;

assign z = io5 ^ io6;

endmodule

module A (input x, input y, output z);

assign z = (x ^ y) & x;

endmodule

module B (input x, input y, output z);

assign z = x ^~ y;

endmodule

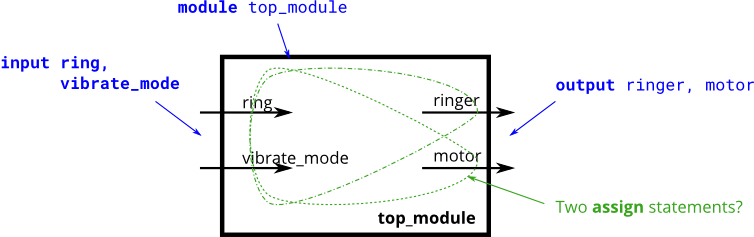

----- 56. Ring or vibrate? -----

Problem Statement

Suppose you are designing a circuit to control a cellphone's ringer and vibration motor. Whenever the phone needs to ring from an incoming call (input ring), your circuit must either turn on the ringer (批注:响铃模式) (output ringer = 1) or the motor (output motor = 1), but not both. If the phone is in vibrate mode (批注:震动模式,震动模式是手机待机模式的一种,此模式手机没有铃声提示,只能发出震动的提示,主要用于需要静音的公共场合) (input vibrate_mode = 1), turn on the motor. Otherwise, turn on the ringer.

Try to use only assign statements, to see whether you can translate a problem description into a collection of logic gates.

Expected solution length: Around 2 lines.

Answer

(批注:由题意可知:1. 当震动模式关闭时,来电时手机只响铃,不震动;2. 当震动模式开启时,来电时手机不响铃,只震动。据此可以列出下面的真值表)

| in: ring | in: vibrate_mode | out: ringer | out: motor |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

module top_module (

input ring,

input vibrate_mode,

output ringer, // Make sound

output motor // Vibrate

);

assign ringer = ring & (~vibrate_mode);

assign motor = ring & vibrate_mode;

endmodule

----- 57. Thermostat -----

Problem Statement

A heating/cooling thermostat(恒温器) controls both a heater (during winter) and an air conditioner (during summer). Implement a circuit that will turn on and off the heater, air conditioning, and blower fan as appropriate.

The thermostat can be in one of two modes: heating (mode = 1) and cooling (mode = 0). In heating mode, turn the heater on when it is too cold (too_cold = 1) but do not use the air conditioner. In cooling mode, turn the air conditioner on when it is too hot (too_hot = 1), but do not turn on the heater. When the heater or air conditioner are on, also turn on the fan to circulate the air. In addition, the user can also request the fan to turn on (fan_on = 1), even if the heater and air conditioner are off.

Try to use only assign statements, to see whether you can translate a problem description into a collection of logic gates.

Expected solution length: Around 3 lines.

Answer1

(批注:由题意可知有以下情况:1. 加热模式下,如果太冷,打开加热器和风扇,但不使用空调;2. 凉爽模式下,如果太热,打开空调和风扇,但不使用加热器;3. 在加热器和空调都未开启的情况下,可以单独打开风扇。艾玛,怎么那么像汽车里的空调系统,于是我们写下了下面的真值表)

凉爽模式:

| in: too_cold | in: too_hot | in: mode | in: fan_on | out: heater | out: aircon | out: fan | 备注 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 正常温度,凉爽模式,风扇关闭 -> 加热器、空调、风扇关闭 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 正常温度,凉爽模式,风扇开启 -> 加热器、空调关闭,风扇开启 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 温度较低,凉爽模式,风扇关闭 -> 加热器、空调、风扇关闭 |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 温度较低,凉爽模式,风扇开启 -> 加热器、空调关闭,风扇开启 |

| 0 | 1 | 0 | 0/1 | 0 | 1 | 1 | 温度较高,凉爽模式,风扇无所谓 -> 加热器关闭,空调、风扇开启 |

加热模式:

| in: too_cold | in: too_hot | in: mode | in: fan_on | out: heater | out: aircon | out: fan | 备注 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 正常温度,加热模式,风扇关闭 -> 加热器、空调、风扇关闭 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 正常温度,加热模式,风扇开启 -> 加热器、空调关闭,风扇开启 |

| 1 | 0 | 1 | 0/1 | 1 | 0 | 1 | 温度较低,加热模式,风扇无所谓 -> 加热器、风扇开启,空调关闭 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 温度较高,加热模式,风扇关闭 -> 加热器、空调、风扇关闭 |

| 0 | 1 | 1 | 1 | 0 | 0 | 1 | 温度较高,加热模式,风扇开启 -> 加热器、空调关闭,风扇开启 |

module top_module (

input too_cold,

input too_hot,

input mode,

input fan_on,

output heater,

output aircon,

output fan

);

assign aircon = too_hot & (~mode);

assign heater = too_cold & mode;

assign fan = (too_hot & (~mode)) | (too_cold & mode) | (fan_on);

endmodule

Answer2

module top_module(

input too_cold,

input too_hot,

input mode,

input fan_on,

output heater,

output aircon,

output fan

);

// Reminder: The order in which you write assign statements doesn't matter.

// assign statements describe circuits, so you get the same circuit in the end

// regardless of which portion you describe first.

// Fan should be on when either heater or aircon is on, and also when requested to do so (fan_on = 1).

assign fan = heater | aircon | fan_on;

// Heater is on when it's too cold and mode is "heating".

assign heater = (mode & too_cold);

// Aircon is on when it's too hot and mode is not "heating".

assign aircon = (~mode & too_hot);

// * Unlike real thermostats, there is no "off" mode here.

endmodule

----- 58. 3-bit population count -----

Problem Statement

A "population count" circuit counts the number of '1's in an input vector. Build a population count circuit for a 3-bit input vector.

Answer1

module top_module(

input [2:0] in,

output reg [1:0] out );

integer i;

always @(*) begin

out = 2'd0;

for(i = 0; i <= 2; i = i + 1) begin

if(in[i] == 1'b1)

out = out + 1;

end

end

endmodule

Answer2

module top_module (

input [2:0] in,

output [1:0] out

);

// This is a function of 3 inputs. One method is to use a 8-entry truth table:

// in[2:0] out[1:0]

// 000 00

// 001 01

// 010 01

// 011 10

// 100 01

// 101 10

// 110 10

// 111 11

assign out[0] = (~in[2] & ~in[1] & in[0]) | (~in[2] & in[1] & ~in[0]) | (in[2] & ~in[1] & ~in[0]) | (in[2] & in[1] & in[0]);

assign out[1] = (in[1] & in[0]) | (in[2] & in[0]) | (in[2] & in[1]);

endmodule

Answer3

module top_module (

input [2:0] in,

output [1:0] out

);

// Using the addition operator works too:

assign out = in[0]+in[1]+in[2];

endmodule

Answer4

module top_module (

input [2:0] in,

output [1:0] out

);

// Yet another method uses behavioural code inside a procedure (combinational always block)

// to directly implement the truth table:

always @(*) begin

case (in)

3'd0: out = 2'd0;

3'd1: out = 2'd1;

3'd2: out = 2'd1;

3'd3: out = 2'd2;

3'd4: out = 2'd1;

3'd5: out = 2'd2;

3'd6: out = 2'd2;

3'd7: out = 2'd3;

endcase

end

endmodule

----- 59. Gates and vectors -----

Problem Statement

You are given a four-bit input vector in[3:0]. We want to know some relationships between each bit and its neighbour:

-

out_both: Each bit of this output vector should indicate whether both the corresponding input bit and its neighbour to the left (higher index) are '1'.For example,

out_both[2]should indicate ifin[3]andin[2]are both 1. Sincein[3]has no neighbour to the left, the answer is obvious so we don't need to knowout_both[3]. -

out_any: Each bit of this output vector should indicate whether any of the corresponding input bit and its neighbour to the right are '1'. For example,

out_any[2]should indicate if eitherin[2]orin[1]are 1. Sincein[0]has no neighbour to the right, the answer is obvious so we don't need to knowout_any[0]. -

out_different: Each bit of this output vector should indicate whether the corresponding input bit is different from its neighbour to the left. For example,

out_different[2]should indicate ifin[2]is different fromin[3]. For this part, treat the vector as wrapping around, soin[3]'s neighbour to the left isin[0].

Answer1

module top_module(

input [3:0] in,

output reg [2:0] out_both,

output reg [3:1] out_any,

output reg [3:0] out_different );

integer i;

always @(*) begin

out_both = 3'd0; out_any = 3'd0; out_different = 4'd0;

for (i = 3; i >= 0; i = i - 1) begin

// out_both

if (i != 3) begin

if (in[i+1] & in[i])

out_both[i] = 1'b1;

end

// out_any

if (i != 0) begin

if (in[i] | in[i-1])

out_any[i] = 1'b1;

end

// out_different

if (i == 3) begin

if (in[0] ^ in[i])

out_different[i] = 1'b1;

end

else begin

if (in[i+1] ^ in[i])

out_different[i] = 1'b1;

end

end

end

endmodule

Answer2

(批注:这是网站给出的参考解法,挺巧妙的,第一次看的时候把我看傻了。。。我还写的很复杂,脑子不太好使啊= =)

module top_module (

input [3:0] in,

output [2:0] out_both,

output [3:1] out_any,

output [3:0] out_different

);

// Use bitwise operators and part-select to do the entire calculation in one line of code

// in[3:1] is this vector: in[3] in[2] in[1]

// in[2:0] is this vector: in[2] in[1] in[0]

// Bitwise-OR produces a 3 bit vector. | | |

// Assign this 3-bit result to out_any[3:1]: o_a[3] o_a[2] o_a[1]

// Thus, each output bit is the OR of the input bit and its neighbour to the right:

// e.g., out_any[1] = in[1] | in[0];

// Notice how this works even for long vectors.

assign out_any = in[3:1] | in[2:0];

assign out_both = in[2:0] & in[3:1];

// XOR 'in' with a vector that is 'in' rotated to the right by 1 position: {in[0], in[3:1]}

// The rotation is accomplished by using part selects[] and the concatenation operator{}.

assign out_different = in ^ {in[0], in[3:1]};

endmodule

----- 60. Even longer vectors -----

Problem Statement

You are given a 100-bit input vector in[99:0]. We want to know some relationships between each bit and its neighbour:

-

out_both: Each bit of this output vector should indicate whether both the corresponding input bit and its neighbour to the left are '1'. For example,

out_both[98]should indicate ifin[98]andin[99]are both 1. Sincein[99]has no neighbour to the left, the answer is obvious so we don't need to knowout_both[99]. -

out_any: Each bit of this output vector should indicate whether any of the corresponding input bit and its neighbour to the right are '1'. For example,

out_any[2]should indicate if eitherin[2]orin[1]are 1. Sincein[0]has no neighbour to the right, the answer is obvious so we don't need to knowout_any[0]. -

out_different: Each bit of this output vector should indicate whether the corresponding input bit is different from its neighbour to the left. For example,

out_differentshould indicate ifin[98]is different fromin[99]. For this part, treat the vector as wrapping around, soin[99]'s neighbour to the left isin[0].

Answer1

module top_module(

input [99:0] in,

output reg [98:0] out_both,

output reg [99:1] out_any,

output [99:0] out_different );

integer i;

always @(*) begin

out_both = 99'd0; out_any = 99'd0; out_different = 100'd0;

for (i = 99; i >= 0; i = i - 1) begin

// out_both

if (i != 99) begin

if (in[i+1] & in[i])

out_both[i] = 1'b1;

end

// out_any

if (i != 0) begin

if (in[i] | in[i-1])

out_any[i] = 1'b1;

end

// out_different

if (i == 99) begin

if (in[0] ^ in[i])

out_different[i] = 1'b1;

end

else begin

if (in[i+1] ^ in[i])

out_different[i] = 1'b1;

end

end

end

endmodule

Answer2

module top_module(

input [99:0] in,

output [98:0] out_both,

output [99:1] out_any,

output [99:0] out_different );

assign out_any = in[99:1] | in[98:0];

assign out_both = in[98:0] & in[99:1];

assign out_different = in ^ {in[0], in[99:1]};

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号