计算机系统结构复习笔记(三)

第三章 流水线技术

3.1流水线的基本概念

3.1.1 什么是流水线

流水线技术

把一个重复的过程分解为若干个子过程,每个子过程由专门的功能部件来实现。把多个处理过程在时间上错开,依次通过各功能段,这样,每个子过程就可以与其他的子过程并行进行。

流水线中的每个子过程及其功能部件称为流水线的级或段,段与段相互连接形成流水线。流水线的段数称为流水线的深度。

把流水线技术应用于运算的执行过程,就形成了运算操作流水线,也称为部件级流水线。

时空图

时空图从时间和空间两个方面描述了流水线的工作过程。时空图中,横坐标代表时间,纵坐标代表流水线的各个段。

流水技术的特点

1.合作:流水线把一个处理过程分解为若干个子过程(段),每个子过程由一个专门的功能部件来实现。

2.瓶颈:流水线中各段的时间应尽可能相等,否则将引起流水线堵塞、断流。时间长的段将成为流水线的瓶颈。

3.流水寄存器:流水线各功能部件间都要有一个缓冲寄存器(锁存器)。

4.流水技术适合于大量重复的时序过程,只有在输入端不断地提供任务,才能充分发挥流水线的效率。

5.流水线需要有通过时间和排空时间。两个时间段流水线均不满载

通过时间:第一个任务从进入流水线到流出结果所需的时间。

排空时间:最后一个任务从进入流水线到流出结果所需的时间。

3.1.2 流水线的分类

单功能流水线与多功能流水线(按照流水线所完成的功能来分类)

单功能流水线:只能完成一种固定功能的流水线。

多功能流水线:流水线的各段可以进行不同的连接,以实现不同的功能

静态流水线与动态流水线(按照同一时间内各段之间的连接方式对多功能流水线做进一步的分类)

静态流水线:在同一时间内,多功能流水线中的各段只能按同一种功能的连接方式工作。

动态流水线:在同一时间内,多功能流水线中的各段可以按照不同的方式连接,同时执行多种功能。

部件级、处理机级及处理机间流水线(按照流水的级别来进行分类)

部件级流水线(运算操作流水线):把处理机的算术逻辑运算部件分段,使得各种类型的运算操作能够按流水方式进行。

处理机级流水线(指令流水线):把指令的解释执行过程按照流水方式处理。把一条指令的执行过程分解为若干个子过程,每个子过程在独立的功能部件中执行。

处理机间流水线(宏流水线&系统级流水线):它是由两个或两个以上的处理机串行连接起来,对同一数据流进行处理,每个处理机完成整个任务中的一部分。

线性流水线与非线性流水线(按照流水线中是否有反馈回路来进行分类)

线性流水线:流水线的各段串行连接,没有反馈回路。

非线性流水线:流水线中除了有串行的连接外,还有反馈回路。

顺序流水线与乱序流水线(根据任务流入和流出的顺序是否相同来进行分类)

顺序流水线:流水线输出端任务流出的顺序与输入端任务流入的顺序完全相同。每一个任务在流水线的各段中是一个跟着一个顺序流动的。

乱序流水线:流水线输出端任务流出的顺序与输入端任务流入的顺序可以不同,允许后进入流水线的任务先完成(从输出端流出)。

标量处理机与向量流水处理机

把指令执行部件中采用了流水线的处理机称为流水线处理机。有下面两种流水线处理机:

标量处理机:处理机不具有向量数据表示和向量指令,仅对标量数据进行流水处理。

向量流水处理机:具有向量数据表示和向量指令的处理机。

3.2 流水线的性能指标

3.2.1吞吐率

吞吐率:在单位时间内流水线所完成的任务数量或输出结果的数量。用TP表示,计算公式如下:

对于各段时间均相等的流水线来说:

流水线完成n个连续任务所需要的总时间为(假设一条k段线性流水线)

流水线的实际吞吐率:

最大吞吐率:

最大吞吐率与实际吞吐率的关系:

对于各段时间不完全相等的流水线来说:

例如:一条4段的流水线:

S1,S3,S4各段的时间:Δt

S2的时间:3Δt (瓶颈段)

流水线中这种时间最长的段称为流水线的瓶颈段。

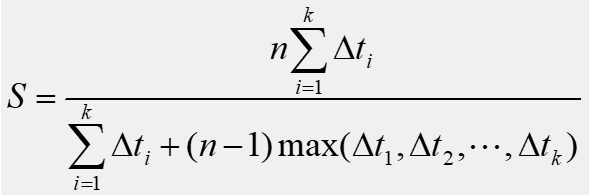

各段时间不等的流水线的实际吞吐率:

( Δti为第i段的时间,共有k个段 )

流水线的最大吞吐率为

解决流水线瓶颈问题的常用方法

1.细分瓶颈段

例如:对前面的4段流水线把瓶颈段S3细分为3个子流水线段:S3a,S3b,S3c

2.重复设置瓶颈段

缺点:控制逻辑比较复杂,所需的硬件增加了。

例如:对前面的4段流水线重复设置瓶颈段S3:S3a,S3b,S3c

3.2.2 加速比(Speedup)

流水线加速比:完成同样一批任务,不使用流水线所用的时间与使用流水线所用的时间之比。

当流水线各段时间相等(都是△t):

流水线的实际加速比为

最大加速比:

当流水线的各段时间不完全相等时:

一条k段流水线完成n个连续任务的实际加速比为

3.2.3 效率(Efficiency)

效率:流水线中的设备实际使用时间与整个运行时间的比值,即流水线设备的利用率。

当各段时间相等时,各段的效率ei相同:

整条流水线的效率为

可以写成

最高效率为:

当流水线各段时间相等时,流水线的效率E与吞吐率TP成正比:

流水线的效率是流水线的实际加速比S与它的最大加速比k的比值。

当E=1时,S=k,实际加速比达到最大。

从时空图上看,效率就是n个任务占用的时空面积和k个段总的时空面积之比:

当各段时间不相等时:

3.2.4 流水线的性能分析举例

例3.1 设在下图所示的静态流水线上计算

流水线的输出可以直接返回输入端或暂存于相应的流水寄存器中,试计算其吞吐率、加速比和效率。

解:(1)选择适合于流水线工作的算法

先计算\(A_1+B_1、A_2+B_2、A_3+B_3\)和\(A_4+B_4\);——4次加法

再计算\((A_1+B_1)×(A_2+B_2)\)和\((A_3+B_3)×(A_4+B_4)\);——2次乘法

然后求总的乘积结果。——1次乘法

(2)画出时空图

求得:

(3)计算性能

1.在18个\(\Delta t\)时间中,给出了7个结果。吞吐率为$TP= \frac{7}{18 \Delta t} $

2.不用流水线,由于一次求和需\(6\Delta t\),一次求积需\(4\Delta t\),则产生上述7个结果共需\((4\times6+3\times4)\Delta t = 36\Delta t\)加速比为\(S=\frac{36 \Delta t}{18 \Delta t}=2\)

3.流水线的效率:$ E=\frac{4 \times6+3\times4}{8\times 18}=0.25 $

可以看出,在求解此问题时,该流水线的效率不高

主要原因:

1.多功能流水线在做某一种运算时,总有一些段是空闲的。

2.静态流水线在进行功能切换时,要等前一种运算全部流出流水线后才能进行后面的运算。

3.运算之间存在关联,后面有些运算要用到前面运算的结果。

4.流水线的工作过程有建立与排空部分。

3.2.5 流水线设计中的若干问题

1.瓶颈问题

2.流水线的额外开销

建立时间:在触发写操作的时钟信号到达之前,寄存器输入必须保持稳定的时间。

传输延迟:时钟信号到达后到寄存器输出可用的时间。

时钟偏移开销:流水线中,时钟到达各流水寄存器的最大差值时间。(时钟到达各流水寄存器的时间不是完全相同)

3.冲突问题

3.3 流水线的相关与冲突

3.3.1 一个经典的5段流水线

介绍一个经典的5段RISC流水线

首先讨论在 非流水情况 下是如何实现的

一条指令的执行过程分为以下5个周期:

1.取指令周期(IF)(Instruction fetch)

IR ← Mem[PC] 。

PC值加4。(假设每条指令占4个字节)

2.指令译码/读寄存器周期(ID)(Instruction decode)

译码。

用IR中的寄存器编号去访问通用寄存器组,读出所需的操作数。

3.执行/有效地址计算周期(EX)(Execution)

不同指令所进行的操作不同:

存储器访问指令:ALU把所指定的寄存器的内容与偏移量相加,形成用于访存的有效地址。

寄存器-寄存器ALU指令:ALU按照操作码指定的操作对从通用寄存器组中读取的数据进行运算。

寄存器-立即数ALU指令:ALU按照操作码指定的操作对从通用寄存器组中读取的第一操作数和立即数进行运算。

分支指令:ALU把偏移量与PC值相加,形成转移目标的地址。同时,对在前一个周期读出的操作数进行判断,确定分支是否成功。

4.存储器访问/分支完成周期(MEM)

该周期处理的指令只有load、store和分支指令。

其他类型的指令在此周期不做任何操作。

load指令:用上一个周期计算出的有效地址从存储器中读出相应的数据。

store指令:把指定的数据写入这个有效地址所指出的存储器单元。

分支指令:分支“成功”,就把转移目标地址送入PC。分支指令执行完成。

5.写回周期(WB)(Writeback)

ALU运算指令和load指令在这个周期把结果数据写入通用寄存器组。

ALU运算指令:结果数据来自ALU。

load指令:结果数据来自存储器系统。

在这个实现方案中:

分支指令需要4个时钟周期(如果把分支指令的执行提前到ID周期,则只需要2个周期)。store指令需要4个周期。其他指令需要5个周期才能完成。

将上述实现方案修改为 流水线实现 :

每一个周期作为一个流水段。

在各段之间加上锁存器(流水寄存器)。

5段流水线的两种描述方式:

第一种描述(类似于时空图)

第二种描述(按时间错开的数据通路序列)

采用流水线方式实现时,应解决以下几个问题:

1.要保证不会在同一时钟周期要求同一个功能段做两件不同的工作。

2.避免IF段的访存(取指令)与MEM段的访存(读/写数据)发生冲突。

3.同样的时钟周期,改为流水执行后,存储器带宽要提升到原来的5倍才能满足流水取值的要求。

3.3.2 相关与流水线冲突

相关:两条指令之间存在某种依赖关系。

相关有3种类型:

1.数据相关(也称真数据相关):

对于两条指令i(在前,下同)和j(在后,下同),如果下述条件之一成立,则称指令j与指令i数据相关。

(1)指令j使用指令i产生的结果;

(2)指令j与指令k数据相关,而指令k又与指令i数据相关。

数据相关具有传递性。

数据相关反映了数据的流动关系,即如何从其产生者流动到其消费者。

2.名相关(名:指令所访问的寄存器或存储器单元的名称。):

如果两条指令使用相同的名,但是它们之间并没有数据流动,则称这两条指令存在名相关。

指令j与指令i之间的名相关有两种:

反相关:如果指令j写的名与指令i读的名相同,则称指令i和j发生了反相关。——读后写

名相关的两条指令之间并没有数据的传送。

如果一条指令中的名改变了,并不影响另外一条指令的执行。

换名技术:通过改变指令中操作数的名来消除名相关。

对于寄存器操作数进行换名称为寄存器换名。

既可以用编译器静态实现,也可以用硬件动态完成。

输出相关:如果指令j和指令i写相同的名,则称指令i和j发生了输出相关。要保证最后的数据是j写的,执行顺序非常重要。 ——写后写

3.控制相关:

控制相关是指由分支指令引起的相关。

流水线冲突

是指对于具体的流水线来说,由于相关的存在,使得指令流中的下一条指令不能在指定的时钟周期执行。

流水线冲突有3种类型:

一.结构冲突:因硬件资源满足不了指令重叠执行的要求而发生的冲突。

常见的导致结构冲突的原因:

1.功能部件不是完全流水

2.资源份数不够

结构冲突举例:访存冲突

有些流水线处理机只有一个存储器,将数据和指令放在一起,访存指令会导致访存冲突

解决办法Ⅰ:插入暂停周期

解决方法Ⅱ:设置相互独立的指令存储器和数据存储器或设置相互独立的指令Cache和数据Cache。

由于访问同一个存储器而引起的结构冲突 :

为消除结构冲突而插入的流水线气泡 :

引入暂停后的时空图:

二.数据冲突(重点):当指令在流水线中重叠执行时,因需要用到前面指令的执行结果而发生的冲突。

数据冲突举例:

DADD R1,R2,R3

DSUB R4,R1,R5

XOR R6,R1,R7

AND R8,R1,R9

OR R10,R1,R11

根据指令读访问和写访问的顺序,可以将数据冲突分为3种类型:

1.写后读冲突(RAW):在 i 写入之前,j 先去读。j 读出的内容是错误的。这是最常见的一种数据冲突,它对应于真数据相关。

2.读后写冲突(WAR):在 i 读之前,j 先写。 i 读出的内容是错误的。由名相关里的反相关引起。

3.写后写冲突(WAW):在 i 写入之前,j 先写。最后写入的结果是 i 的错误的。 这种冲突对应于名相关里的输出相关。

通过定向技术减少数据冲突引起的停顿(定向技术也称为旁路或短路):

关键思想:在某条指令产生计算结果之前,其他指令并不真正立即需要该计算结果,如果能够将该计算结果从其产生的地方直接送到其他指令需要它的地方,那么就可以避免停顿。

采用定向技术后的流水线数据通路 :

需要停顿的数据冲突

并不是所有的数据冲突都可以用定向技术来解决。

举例:

LD R1,0(R2)

DADD R4,R1,R5

AND R6,R1,R7

XOR R8,R1,R9

增加流水线互锁(pipeline interlock)硬件,插入“暂停”。

作用:检测发现数据冲突,并使流水线停顿,直至冲突消失。

无法将LD指令的结果定向到DADD指令 :

流水线互锁机制插入气泡后的执行过程 :

依靠编译器解决数据冲突

让编译器重新组织指令顺序来消除冲突,这种技术称为指令调度或流水线调度。

举例:

请为下列表达式生成没有暂停的指令序列(假设载入延迟为1个时钟周期):

\(A=B+C ;\)

\(D=E-F ;\)

三.控制冲突:流水线遇到分支指令和其他会改变PC值的指令所引起的冲突。

执行分支指令的结果有两种

分支成功:PC值改变为分支转移的目标地址。在条件判定和转移地址计算都完成后,才改变PC值(MEM段)。

不成功或者失败:PC的值保持正常递增,指向顺序的下一条指令。

处理分支指令最简单的方法:“冻结”或者“排空”流水线 。

前述5段流水线中,改变PC值是在MEM段进行的。给流水线带来了三个时钟周期的延迟:

把由分支指令引起的延迟称为分支延迟。

可采取两种措施来减少分支延迟:(硬件方法)

1.在流水线中尽早判断出分支转移是否成功;

2.尽早计算出分支目标地址。

两个尽早必须同时采用,缺一不可。

下面的讨论中,我们假设:

这两步工作被提前到ID段完成,即分支指令是在ID段的末尾执行完成,所带来的分支延迟为一个时钟周期。

3种通过软件(编译器)来减少分支延迟的方法:

共同点:

(1)对分支的处理方法在程序的执行过程中始终是不变的,是静态的。

(2)要么总是预测分支成功,要么总是预测分支失败

1.预测分支失败

(做的事)允许分支指令后的指令继续在流水线中流动,就好象什么都没发生似的。

(实际上)若确定分支失败,将分支指令看作是一条普通指令,流水线正常流动。

(实际上)若确定分支成功,流水线就把在分支指令之后取出的所有指令转化为空操作,并按分支目地重新取指令执行。

2.预测分支成功

假设分支转移成功,并从分支目标地址处取指令执行。

起作用的场合:先知道分支目标地址,后知道分支是否成功的系统中。

3.延迟分支

在分支指令后面加上m条指令(延迟槽),把它们看成一个整体。不管分支是否成功,都顺序执行这些指令。

分支延迟指令的调度:在延迟槽中放入有用的指令。

三种调度方法:

进一步改进:分支取消机制:

当分支的实际执行方向和事先所预测的一样时,执行分支延迟槽中的指令,否则就将分支延迟槽中的指令转化成一个空操作。(动态调度)

3.4 流水线的实现

3.4.1 MIPS的一种简单实现

NPC、IR、A、B、Imm、Cond、ALUo、LMD等临时寄存器是在单指令执行过程中保存中间结果的。

3.4.2 基本的MIPS流水线

每一个时钟周期完成的工作看作是流水线的一段,每个时钟周期启动一条新的指令。

流水实现的数据通路(改动):

段与段之间设置流水寄存器:

流水寄存器的命名:用其相邻的两个段的名称拼合而成。例如:ID段与EX段之间的流水寄存器用ID/EX表示。

寄存器的命名形式为:x.y

所包含的字段的命名形式为:x.y[s]

x:流水寄存器名称

y:具体寄存器名称

s:字段名称

例如:

ID/EX.IR:流水寄存器ID/EX中的子寄存器IR

IRID/EX.IR[op]:该寄存器的op字段(即操作码字段)

流水寄存器的作用:将各段的工作隔开,使得它们不会互相干扰。保存相应段的处理结果。向后传递后面将要用到的数据或者控制信息。

流水实现的数据通路:

3.5 向量处理机(非重点)

3.5.1 向量处理方式

3.5.2 向量处理机的结构

3.5.3 提高向量处理机性能的方法

链接技术:具有先写后读相关的两条指令,在不出现功能部件冲突和源向量冲突的情况下,可以把功能部件链接起来进行流水处理,以达到加快执行的目的。

分段开采技术:当向量的长度大于向量寄存器的长度时,必须把长向量分成长度固定的段,然后循环分段处理,每一次循环只处理一个向量段。

浙公网安备 33010602011771号

浙公网安备 33010602011771号