FPGA高速

划重点

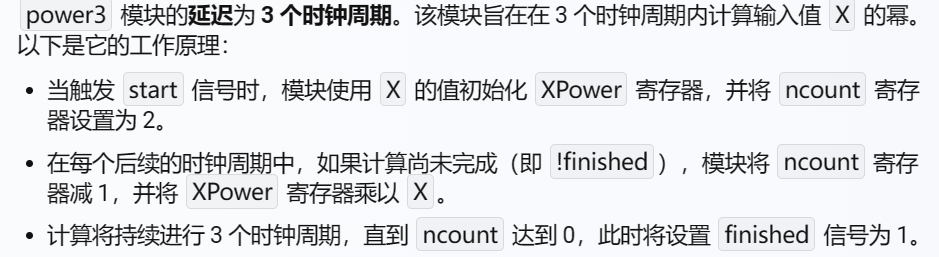

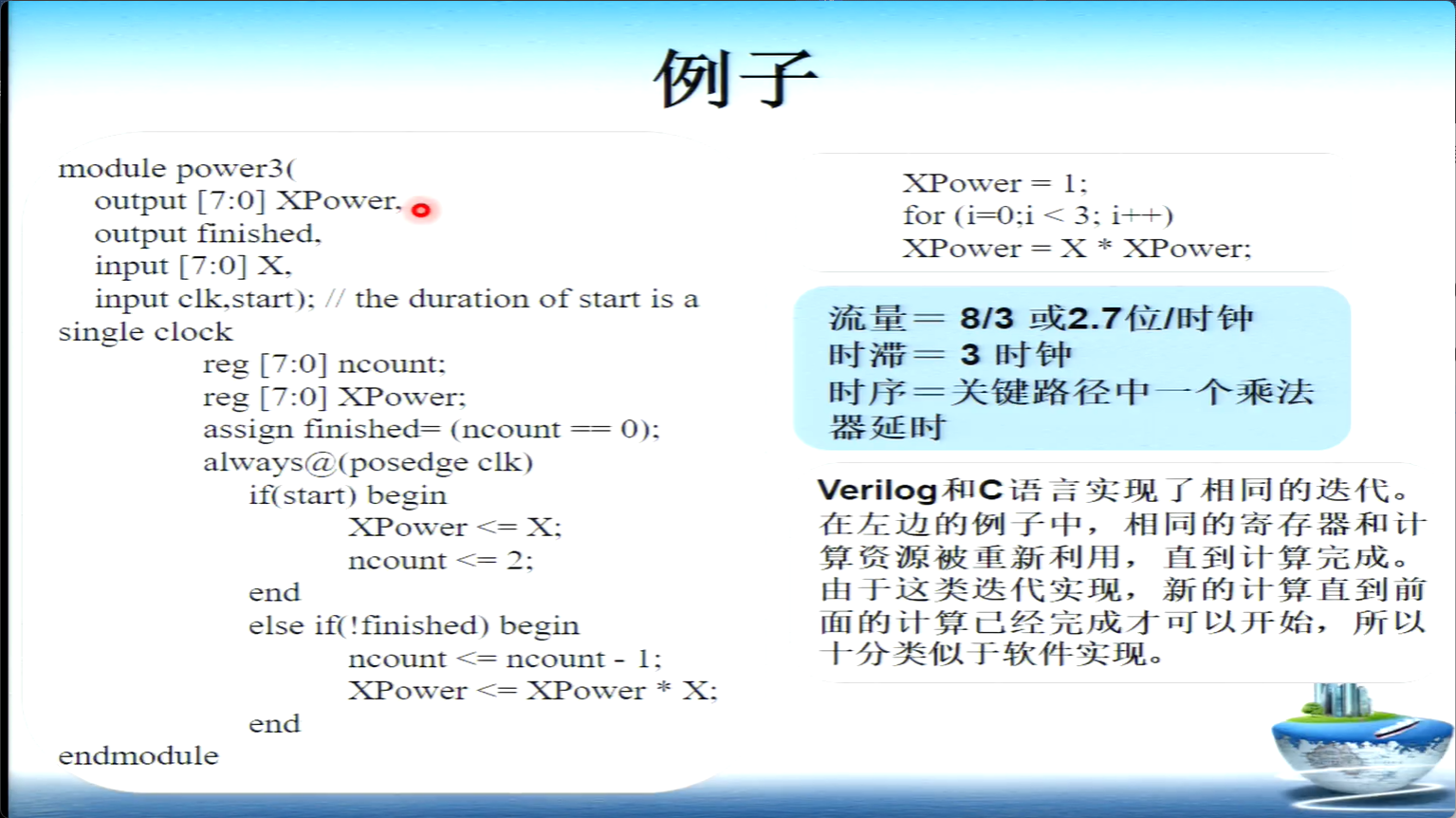

module power3(

output [7:0] XPower,

output finished,

input [7:0] X,

input clk,

input start

);

reg [7:0] ncount;

reg [7:0] XPower;

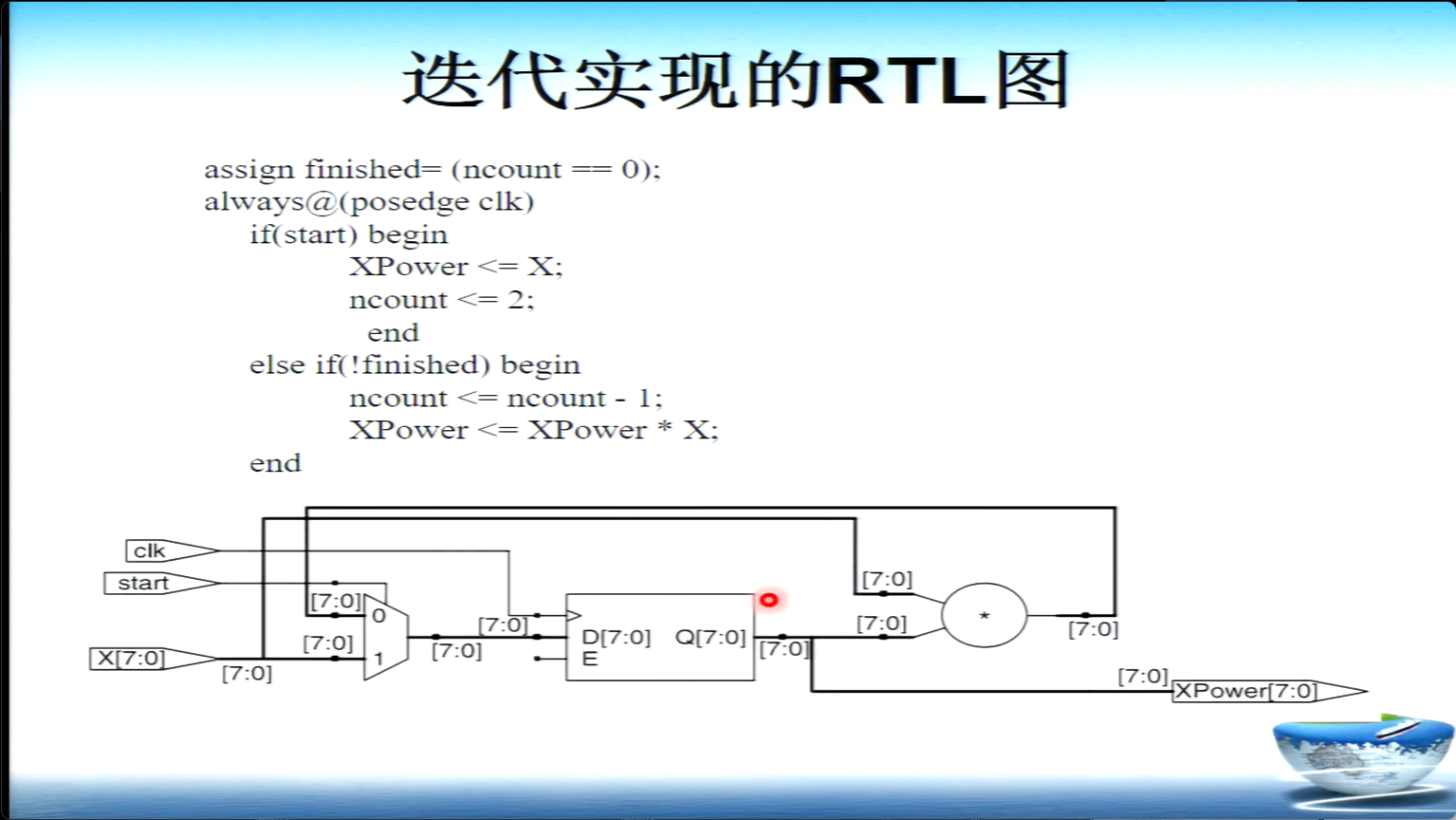

assign finished = (ncount == 0);

always @(posedge clk)

if (start) begin

XPower <= X;

ncount <= 2;

end

else if (!finished) begin

ncount <= ncount - 1;

XPower <= XPower * X;

end

endmodule

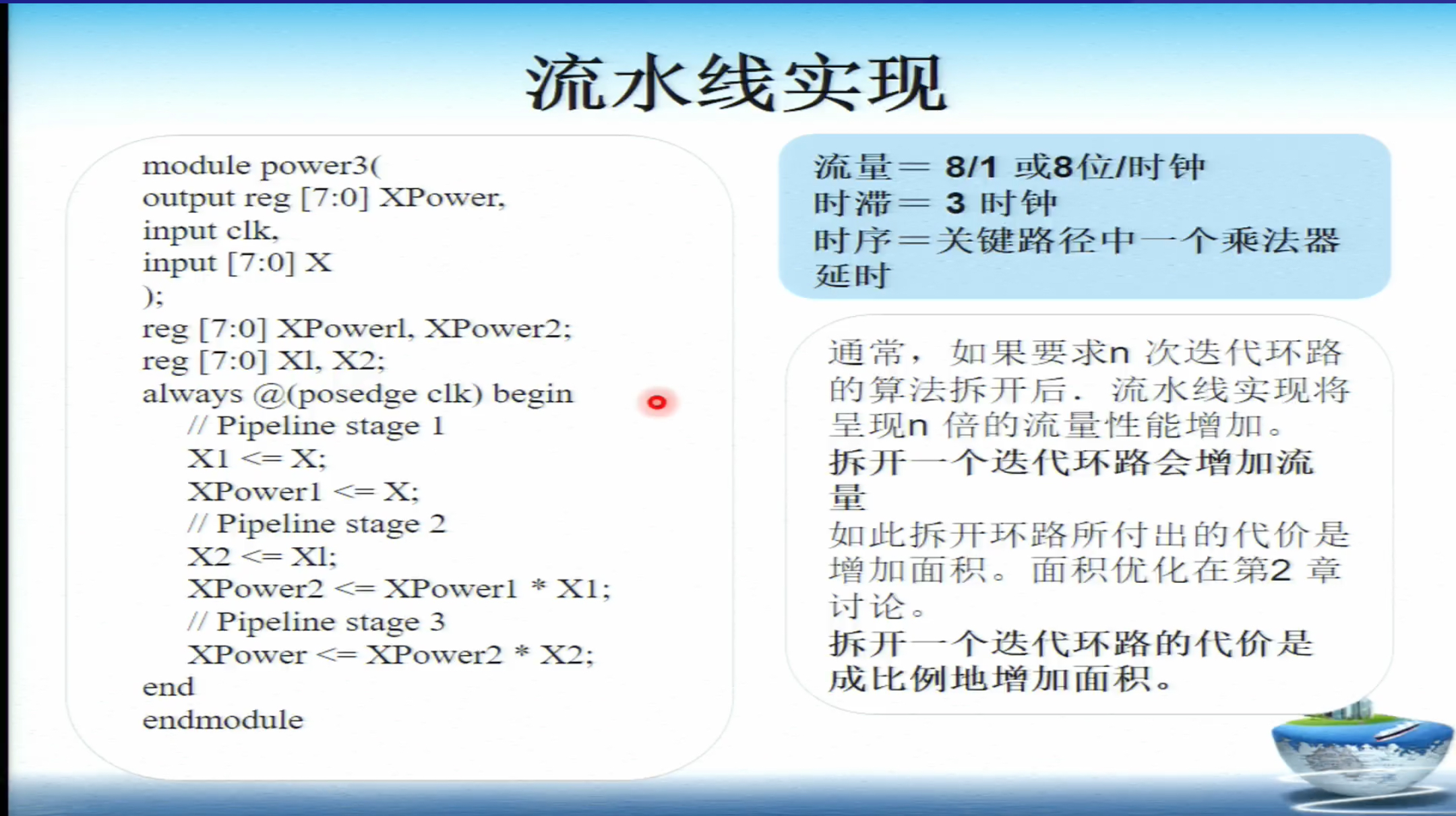

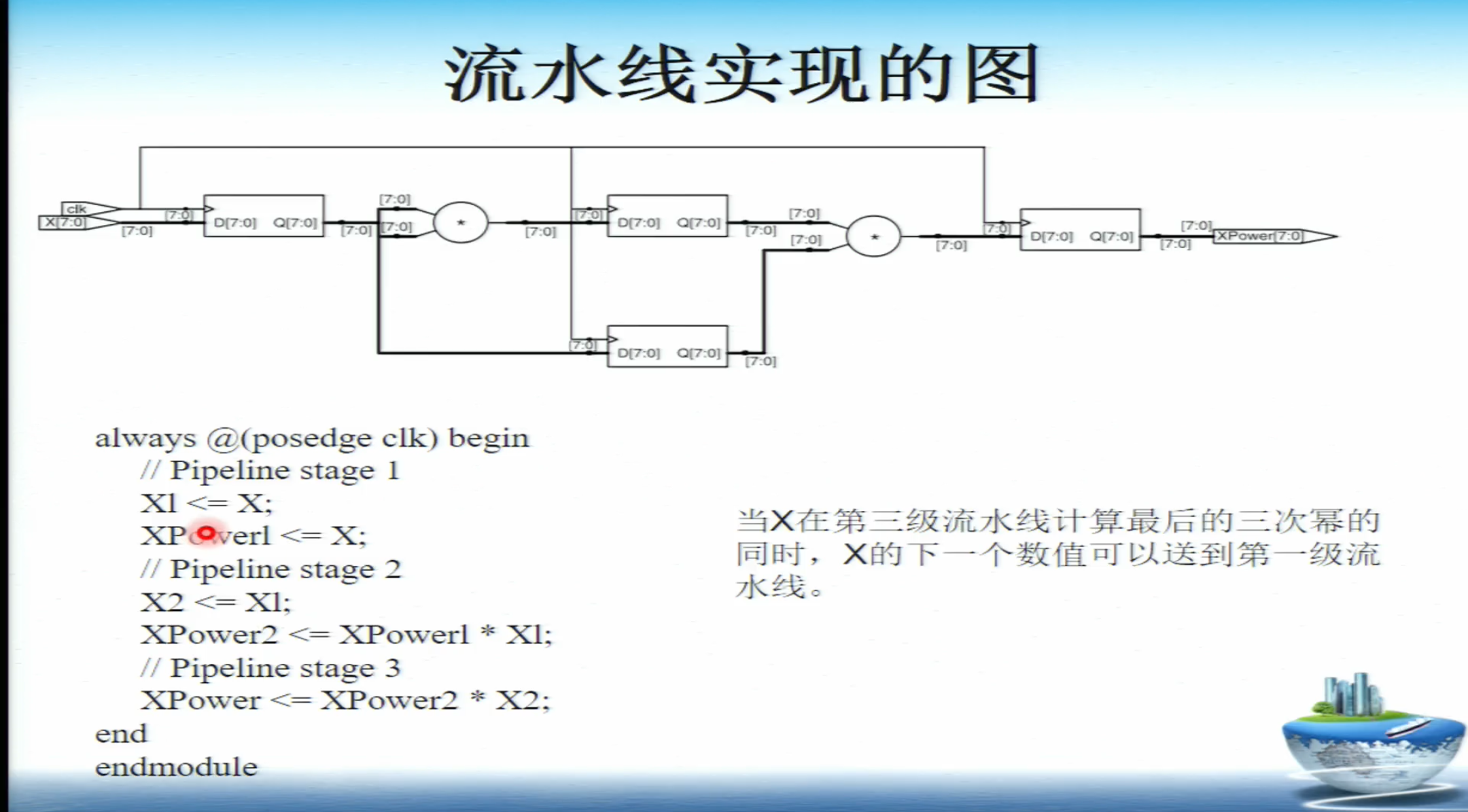

流水线设计

实际上流水线设计是牺牲资源换取通量throughout的方法,即在同一个时钟周期中尽可能多地对数据进行计算,以便得单位时间内可以得到更多的结果

打一拍 时序同步

划重点

划重点

RTL和代码转换