运放指标与供电

失调电压Vos

offset voltage

使用实际运放时,我们发现运放的两个输入端同时接地时,输出将呈饱和电压(电源轨V+ 或V- )而非0,原因是运放内部存在VOS

- 该值可正可负

- 可以看作在同相输入端有一个内部的小电压源

- 想象实际运放内部有一个理想运放

失调电压看起来很小,数量级在μV~mV,但放大后即使不会让运放输出饱和,也会影响高倍放大的精密电路检测微弱信号的精度

偏置电流IB

bias current

定义

实际运放的两个输入端电流不为0,且不受输入端电压影响,好比同相和反相输入端分别接了两个电流源。

这两个电流值很近似,但不绝对相同,因此分别用common mode(Input Bias Current)和diffrential mode(Input Offset Current,即IOS ,为两电流之差的绝对值)的形式来表示

手册

偏置电流看起来很小,比如OPA656(双极型输入)的最大偏置电流为35uA,但是对输出阻抗高的信号源放大时非常重要,例如在100K电阻上可产生3.5V的电压,放大倍数稍大就可以使运放饱和

应用

为了减小偏置电流的影响,考虑反向放大电路在同相输入端接入电阻的情况

输入阻抗

impedance,resistance

- Noninverting Input Impedance

- 非反相输入阻抗

- Inverting Input Resistance

- 反相输入电阻

这两个参数意味着运放的输入阻抗作为信号源的负载时,会影响信号源输出的电压和电流

两个基本定义

共模输入阻抗

差模输入阻抗

- 定义:同相输入端和反相输入端之间的总电阻

- 测量方法

- 差分输入电压的变化与偏置电流的变化之比

补充

- 共模输入

- 输入两个同频同相同幅的信号

- 输出零电压

- 称为共模抑制

- 不希望该杂讯出现在输出端干扰想要的信号

- 称为共模抑制

- 差分输入(双端输入)

输入电压范围

input voltage range

- Common-Mode Voltage Range

- 超过该范围会引起削波或其他失真

dc supply voltage

- 电源轨

- 轨到轨输入和输出运放(OPA365)

- 轨到轨输出运放(OPA335):输入在高电平处需要1.5V净空

- 非轨到轨运放(LM324,OP27):输入和输出在高低电平处都需要一定的净空(裕量从数mV到数V不等)

输入电压范围

轨到轨:ouput swing from rail

非轨到轨:VOH (High-level output voltage) 和 VOL

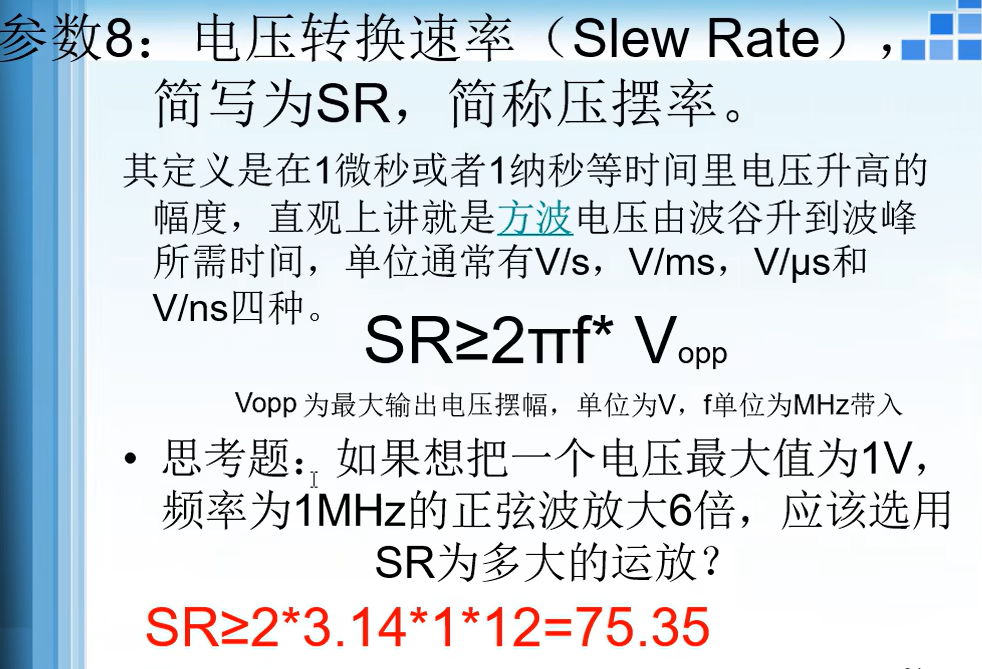

压摆率

Slew Rate

定义

应用

- 根据信号的最大斜率选择相应压摆率的运放,避免波形失真

- 结合增益带宽积计算。例如,输出50MHz正弦信号可以达到多少峰峰值

- 压摆率限制了输出大信号的带宽

供电

运放只要两个电源端有足够的压差就可以工作

数据手册

网站:立创商城,中国IC,得捷电子,贸泽电子

单电源供电

- 节约成本‘

- 输出小信号时误差较大,输出电压越小,误差越大

- 能处理的频率较低≤100kHz

- 微弱信号检测时最好用双电源供电

OPA354 250MHz (单位增益带宽) 轨到轨IO(输入轨到轨,输出轨到轨)

- Supply voltage (V+ to V-) MAX 7.5

PCB布局

- 大的去耦电容(库电容)远离芯片

- 小的去耦电容(旁路电容)靠近芯片

- 让去耦电容尽量靠近电源引脚

- 如果使用多个去耦电容,将最小的去耦电容放在离电源引脚最近的位置

- 尽量缩短反相输入端的引脚连接

- 不要将过孔置于去耦电容和电源引脚之间

V+ 和 V- 间接电容滤波的作用:减少偶数次高次谐波

空气中有手机信号、微波信号等杂讯,会在电源线上产生感应电动势,干扰芯片的正常工作,最好使用RC低通滤波器,电容靠近Vcc 引脚

- 屏蔽罩

举例

STC8A

- 对不同频率的系统时钟选择不同容值的去耦电容

- 频率越高,越靠近芯片Vcc 引脚的电容容值越小,0.1μF在高频下变成了感性,不但没法滤波,还有害。可以并联多个电容搭配,滤掉不同频率的高频干扰信号

OPA320驱动ADS8326

- 单电源供电时由于输出摆幅限制而在接近GND时丢失少量ADC代码。可提供负电源-5V,用BAS40(肖特基二极管)的导通管压降(0.3V),刚好给运放提供-0.3V的负电压

Single Ended Input: Extending the OP Amp Range

LM7705(低噪声负偏置产生 5V→-0.232V)

容值选择

根据电路处理信号的频率选择:

- DC~十数MHz:0.1μF

- 十数MHz~百数十MHz:0.01μF

- 百数十MHz~数百MHz:1000pF

- 数百MHz~数GHz:100pF

宽带放大器应取上述多个电容器并联

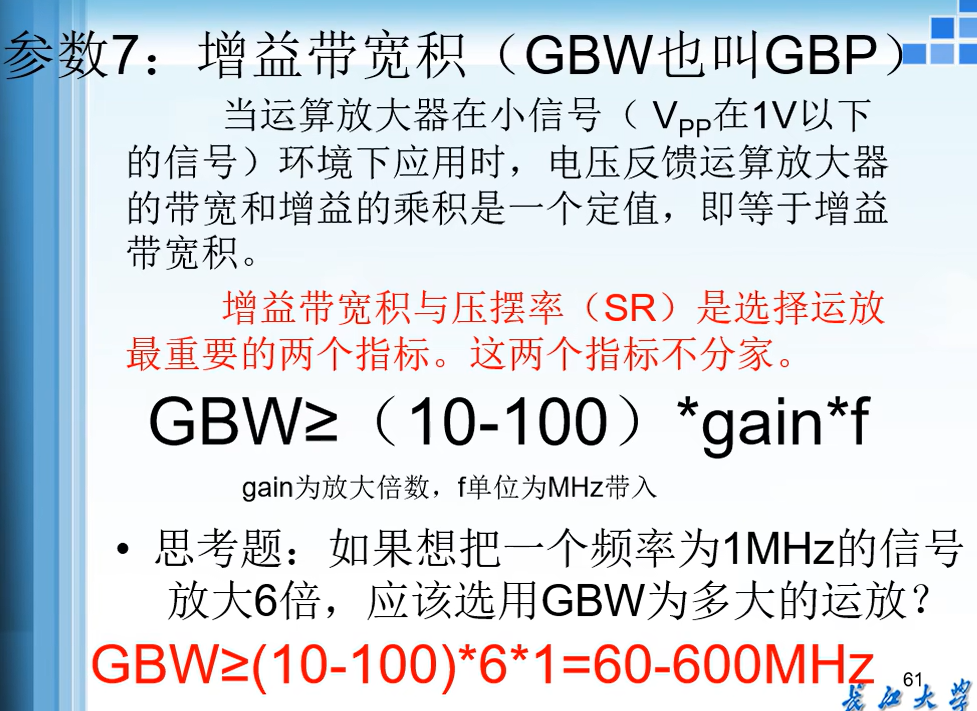

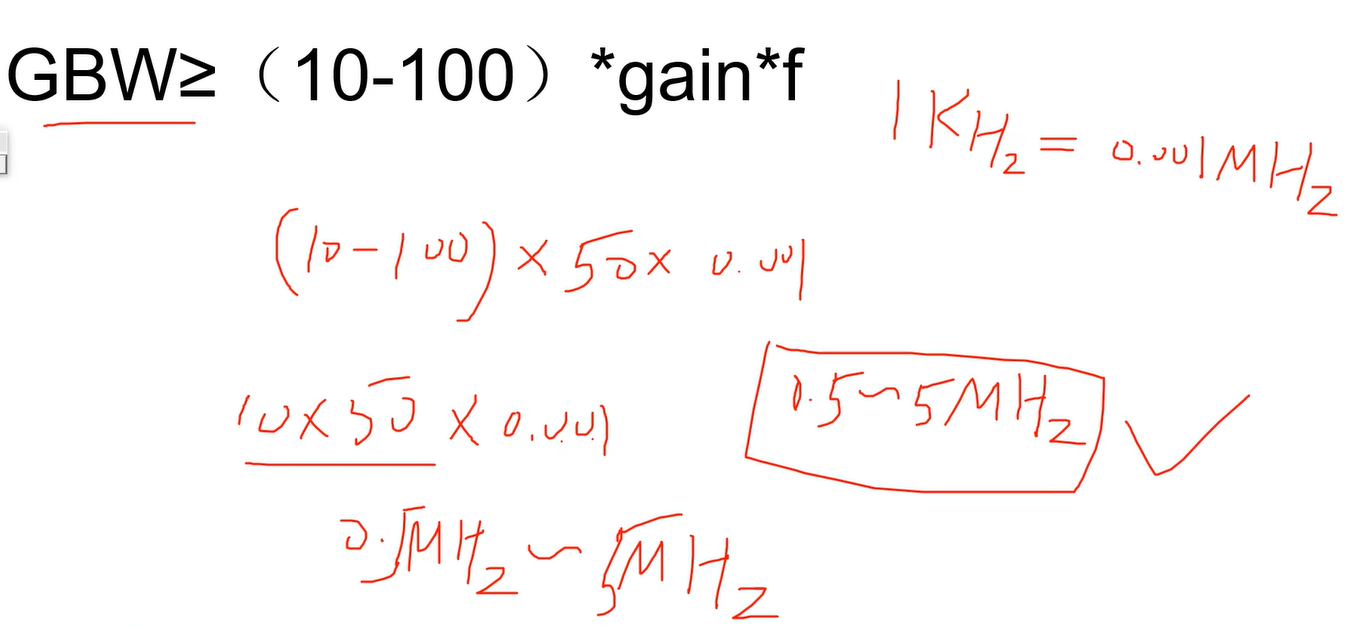

增益带宽积

真题

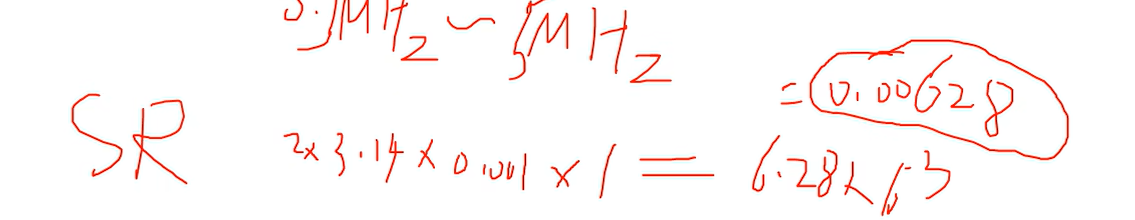

压摆率

真题

真题分析

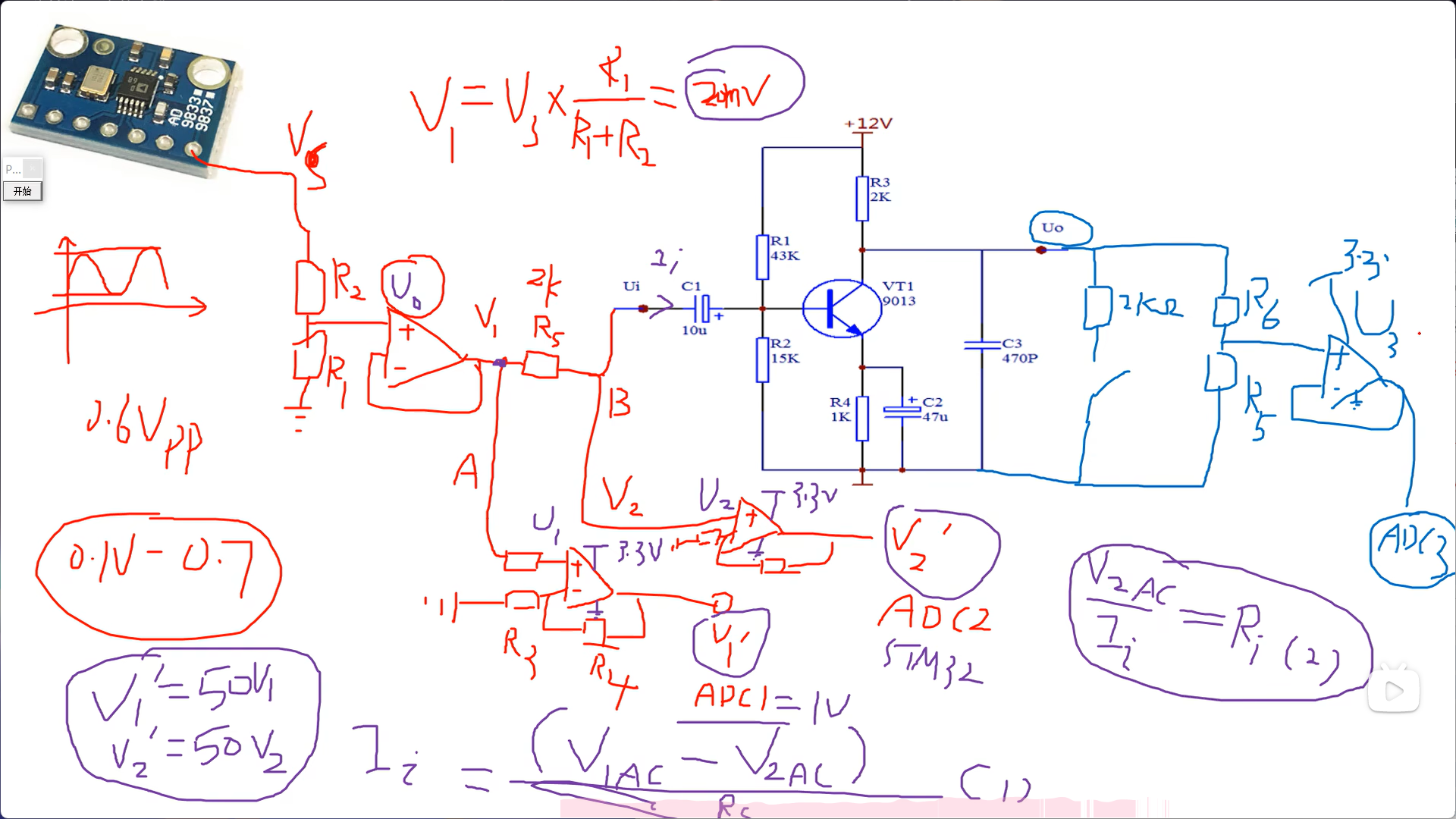

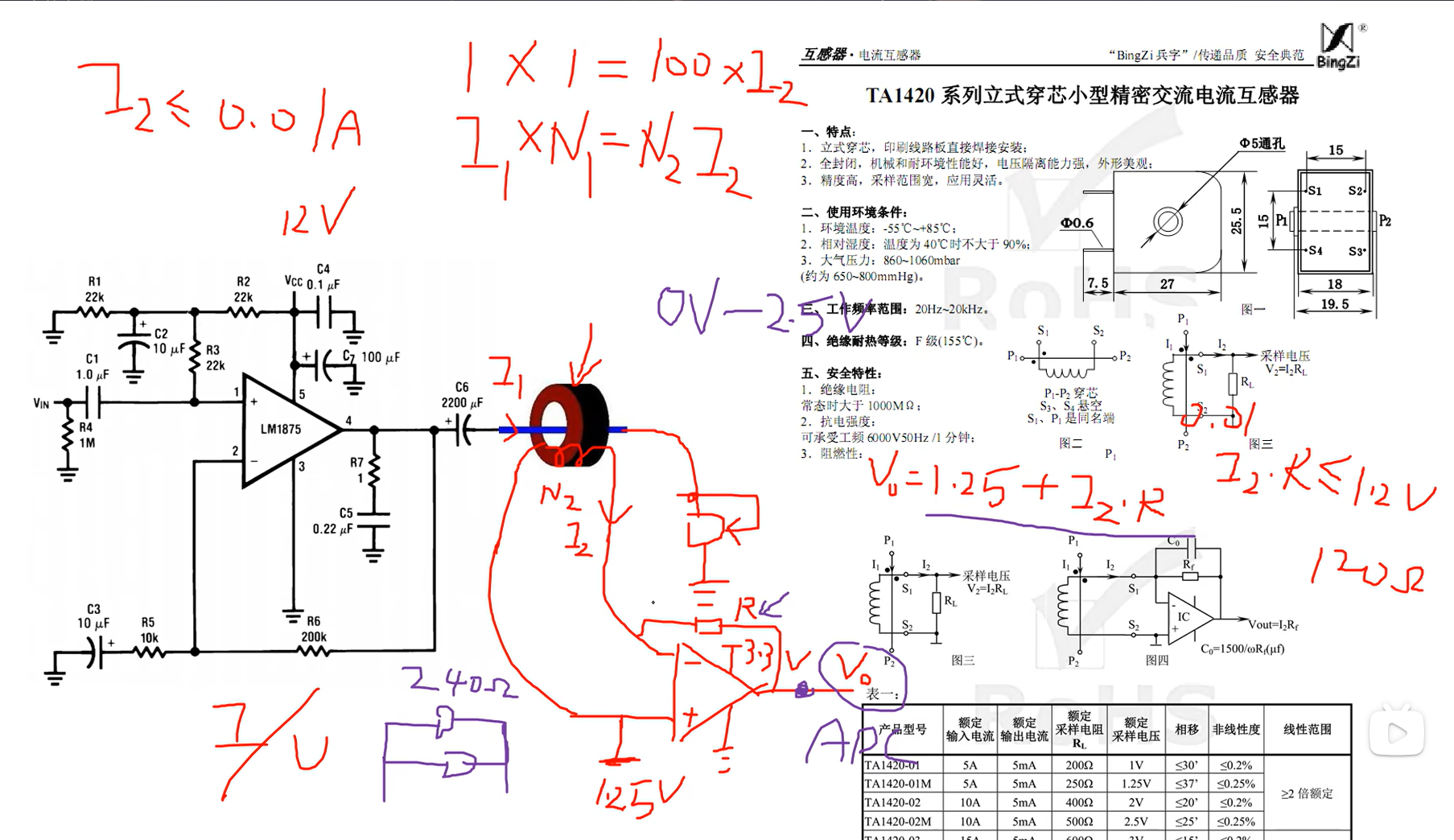

IV转换

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 使用C#创建一个MCP客户端

· 分享一个免费、快速、无限量使用的满血 DeepSeek R1 模型,支持深度思考和联网搜索!

· ollama系列1:轻松3步本地部署deepseek,普通电脑可用

· 基于 Docker 搭建 FRP 内网穿透开源项目(很简单哒)

· 按钮权限的设计及实现