亚稳态记录

亚稳态

(由边沿提取温故)

定义

触发器输出信号无法在规定时间内输出确定的状态

同步电路

定义

钟控单元全由一个统一的全局时钟控制

- 避免竞争冒险

- 触发器只在时钟边沿变取值,减少毛刺和噪声

缺点

- 到达各个触发器有延迟

- 时钟可能抖动

- 延时单元消耗面积,功耗大

异步电路

定义

电路数据传输无统一时钟控制,可在任意时刻进行

例如两个触发器用两个clk控制

同一个时钟域、不同的时钟域主要是针对时钟源点来说的

- 比如从同一个PLL引出几个时钟,这些时钟之间的相位和倍数是可控的,因此它们是同步时钟

- 又如从两个PLL引出两个时钟,即使它们频率相同也是异步时钟,因为它们的相位关系不可控

全局异步、局部同步的设计要注意异步信号与同步电路的交互问题

可以用故障间隔平均时间MTBF衡量亚稳态影响

该值越大,影响越小

时钟频率和数据变化率固定时,只能在两个寄存器间不添加任何逻辑来减少逻辑延时

a_clk下采样到的数据在b_clk下如果仅用一个触发器锁存,那么结果可能是亚稳态(输出中间电平)

输出阻抗

信号源

我们设置的是希望示波器显示的值

50Ω :以负载为50Ω输出

示波器

50Ω : 内阻为50Ω

使用这个关系式对Vsig、Rs、Ro串联回路进行分析

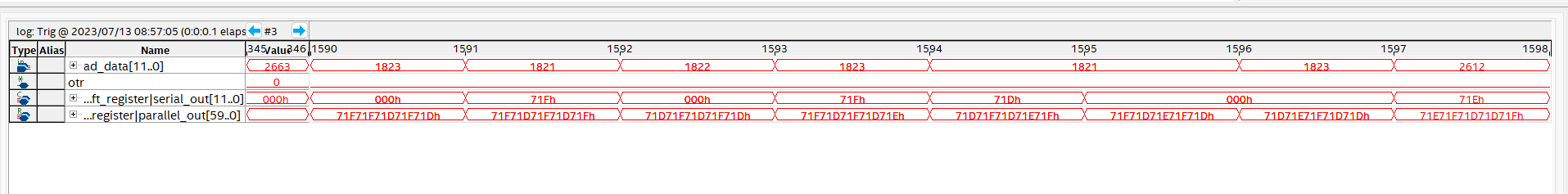

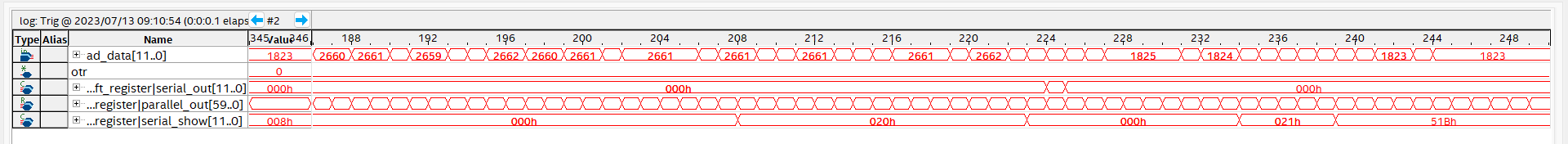

移位寄存器

对后两位进行减法操作时,如果所得为负数,也会和(>20)得到一样的判断结果

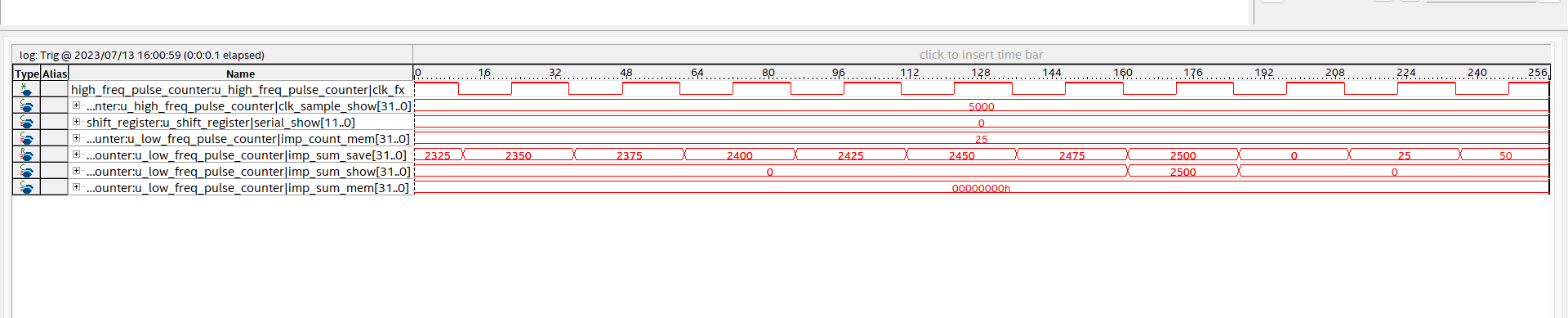

数据保存

打拍前

系统误差

ADC 系统误差为2%

低幅值时(0.1V取4075还是4076)即使变动1也会造成2%的误差

数据保存

mem没能保存show

可能原因:

- 建立时间,英文名字Setup Time,缩写是 Tsu,即在时钟上升沿之前数据必须稳定的最短时间。

若不满足setup time,数据无法进入寄存器,也就是说寄存器的数据采样会失败。- 保持时间,英文名字Hold Time,缩写是 Th,即在时钟上升沿之后数据必须稳定的最短时间。若不满足hold time,数据也无法进入寄存器,也就是说寄存器的数据采样采样也会失败。

解决方案

- 移位寄存器!

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· winform 绘制太阳,地球,月球 运作规律

· AI与.NET技术实操系列(五):向量存储与相似性搜索在 .NET 中的实现

· 超详细:普通电脑也行Windows部署deepseek R1训练数据并当服务器共享给他人

· 【硬核科普】Trae如何「偷看」你的代码?零基础破解AI编程运行原理

· 上周热点回顾(3.3-3.9)