计算机基础知识

导航

目录

一、数的转换

进位计数制系统基本概念

- 数制:人为定义的计数方法

- 基数(底数):数字符号

- 数码:每个数字符号算一个数码

- 数位:数值当中某一个数的位置

- 位权:数的整数次幂

| 特点/数制 | 十进制D | 二进制B | 八进制Q | 十六进制H |

|---|---|---|---|---|

| 基本数码 | 0-9 | 0,1 | 0-7 | 0-9.A-F |

| 基数 | 10 | 2 | 8 | 16 |

| 位权 | \(10^n\) | \(2^n\) | \(8^n\) | \(16^n\) |

R进制-->十进制

使用按权展开法

将R进制数的每一位数值用\(R^k\)形式表

R为底数/基数

K为指数

例如:八进制-->十进制

604.01 = 6*\(8^2\)+4*\(8^0\)+1*\(8^{-2}\)

十进制-->R进制

使用短除法(取余数,从下往上取)

数据的储存单位

在计算机中,数据的最小存储单位为BIT,1比特为1个二进制位。字节(Byte.B),1个字节为8个二进制位。

二进制的算术运算

加法运算

- 0+0=0

- 0+1=1

- 1+0=1

- 1+1=0(向上进一位)

减法运算

- 0-0=0

- 1-0=1

- 1-1=0

- 0-1=1(向上借款)

乘法运算

- 0*0=0

- 0*1=0

- 1*0=0

- 1*1=1

除法运算

- 0/0 1/0 无意义

- 0/1=0

- 1/1=1

二进制的逻辑运算

与或非

二、数据的表示

机器数

- 码制(原码、反码、补码、移码)

| 数值+1(正1) | 数值-1(负1) | 1+(-1)也就是代表1-1 | |

|---|---|---|---|

| 原码(头一个数字代表正负) | 0000 0001 | 1000 0001 | 1000 0010 |

| 反码(正数不变,负数取反头位是1) | 0000 0001 | 1111 1110 | 1111 1111 |

| 补码(正数不变,负数在反码基础上+1) | 0000 0001 | 1111 1111 | 0000 0000 |

| 移码(补码基础上数值不变,符号位取反) | 1000 0001 | 0111 1111 | 1000 0000 |

-

补码:常用于加减法运算

-

移码:常用语浮点数的阶码

整数数值范围 原码 -(\(2^{n-1}\)-1)~\(2^{n-1}\)-1 反码 -(\(2^{n-1}\)-1)~\(2^{n-1}\)-1 补码 -\(2^{n-1}\)~\(2^{n-1}\)-1 移码 -\(2^{n-1}\)~\(2^{n-1}\)-1 -

定点数:小数点的位置固定不变的数,小数点不需要占用一位二进制

定点整数

定点小数 -

浮点数:N=\(R^e\)*M其中M称为尾数,e是指数(阶码),R为基数(阶码的底)

- 计算方法:对阶(小阶数对齐大阶数)->尾数计算->结果格式化(转换成0.1***的格式)

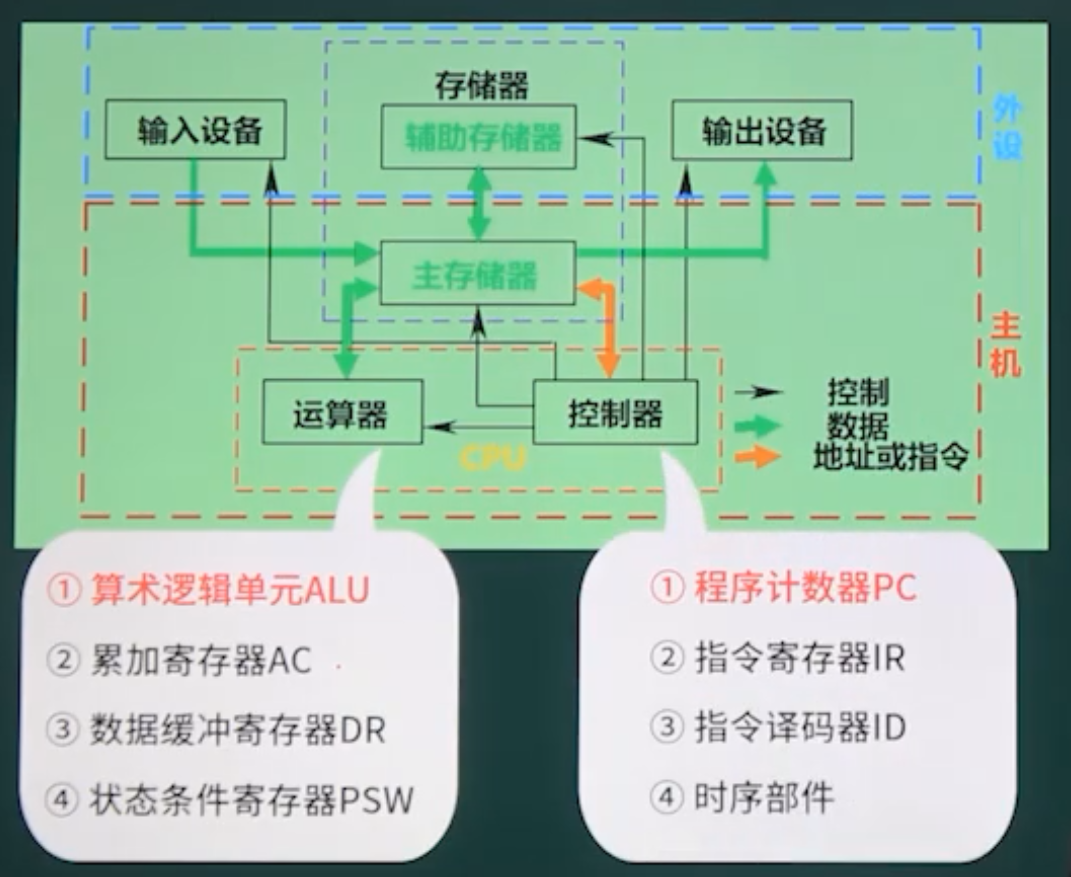

三、计算机的基本组成

运算器

- 算术逻辑单元ALU:数据的算术运算和逻辑运算

- 累加寄存器AC:通用寄存器,为ALU提供一个工作区,用在暂存数据

- 数据缓冲寄存器DR:写内存时,暂存指令或数据状态条件

- 寄存器PSW:存状态标志与控制标志

控制器

- 程序计数器PC:存储下一条要执行指令的地址

- 指令寄存器IR:存储即将执行的指令

- 指令译码器ID:对进行分析解释

- 时序部件:提供时序控制信号指令中的操作码字段

基本概念

- CPU的性能指标:主频、字长、CPU缓存、核心数量

- 总线的分类:数据总线、控制总线、地址总线

- 总线的性能指标:带宽、位宽、工作频率

- BIOS/CMOS系统性能评测方法:时钟频率、指令执行、等效指令速度法数据处理速率(PDR)、核心程序法、基准测试程序

指令、寻址方式

指令

一条指令就是机器语言的一个语句,是一组有意义的二进制代码

- 操作码字段OP:指出了计算机要执行什么性质的操作

- 地址码字段A:包含各操作数的地址及操作结果的存放地址等

寻址方式

- 立即寻址方式特点:操作数直接在指令中,速度快,灵活性差

- 直接寻址方式:-特点:指令中存放的是操作数的地址

- 间接寻址方式---特点:指令中存放了一个地址,这个地址对应的内容是操作数的地址。

- 寄存器寻址方式特点:寄存器存放操作数

- 寄存器间接寻址方式特点:寄存器内存放的是操作数的地址

move R1(跟寄存器有关), #数字H(跟立即寻址有关)

四、流水线

流水线

多条指令重叠进行操作的一种准并行处理实现技术

流水线周期:执行时间最长的一段

流水线计算公式:

- 1条指令执行时间(取指+分析+执行)+(指令条数-1)*流水线周期

- 流水线的吞吐率(TP)计算的最基本的公式为:TP=\(\frac {n} {T_k}\)

- 流水线的最大吞吐率:流水线周期的倒数

五、多级存储结构

cache

- 功能:提高CPU数据输入输出的速率,突破所谓的“冯·诺依曼瓶颈”

- 速度:在计算机的存储系统体系中,Cache是访问速度较快的层次

- 原理:使用Cache改善系统性能的依据是程序的局部性原理组成:Cache由两部分

- 组成:控制部分和Cache存储器部分

- 平均系统周期时间(以读操作为例:使用“Cache+主存储器”

- \(t_3\)=h*\(t_1\)+(1-h)*\(t_2\)

- h代表对Cache的访问命中率

- \(t_1\)表示Cache的周期时间

- \(t_2\)表示主存储器周期时间

- 系统的平均周期为\(t_3\)

- (1-h)又称为失效率(未命中率)

直接映像和变换

- 地址变换电路简单,访问速度快

- 空间利用率低,冲突率高

- 对页面置换算法依赖度较高,且Cache空间利用率较低,命中率较低

全相联地址映像和变换

- 空间利用率高,命中率较高

- 冲突概率低

- 实现复杂,速度慢,适合小容量cache

组相联地址映像和变换

- 是以上两种方式的折衷

- 实现难度和造价要比直接映像方式高

输入输出设备管理

- 直接程序控制:无条件传送方式、程序查询方式

- 中断方式

- 中断方式直接存储器存取方式(DMA):在传送数据块的过程中不需要CPU干涉

- 输入输出处理机(IOP)

六、可靠性、校验码

可靠性

- 串联系统:R=\(R_1\)*\(R_2\)*……*\(R_n\)

- 并联系统:R=1-(1-\(R_1\))*(1-\(R_2\))*……*(1-\(R_n\))

- 混合系统:R*(1-(\({1-R}^3\))*(1-(\({1-R}^2\))

校验码

- 奇偶校验码-仅可检错,可检测1(奇数)位错

- 增加一位校验码使得1的个数为奇数或偶数,从而使码距为2

- CRC(循环冗余码)-仅可检错,可检测多位

- 编码程度为k+r(k个数据后面产生r个校验码)

- 海明码-可检错,且可纠1位错

- 在数据位之间插入K个检验码,数据位设为n,则有\(2^k\)-1\(\geq\)n+k