FPGA VGA时序的理解

最近在做FPGA毕业设计,毕业设计规划的是摄像头采集图像,经过均值滤波,中值滤波,高斯滤波,然后通过VGA接口控制显示器显示出来,所以最近学习了一下FPGA的VGA驱动的相关内容。

VGA接口

如上图所示,VGA接口一共15针,分为3*5。

主要使用的信号线是上面的5根线,行同步信号,场同步信号和R,G,B基色的模拟信号。

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。隔行扫描是指电子束扫描时每隔一行扫一线,完成一屏后在返回来扫描剩下的线,隔行扫描的显示器闪烁的厉害,会让使用者的眼睛疲劳。

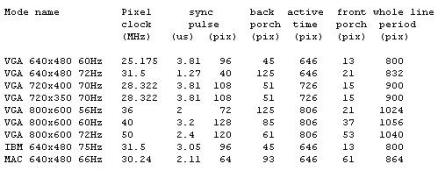

VGA水平扫描时序

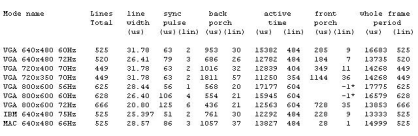

VGA垂直扫描时序

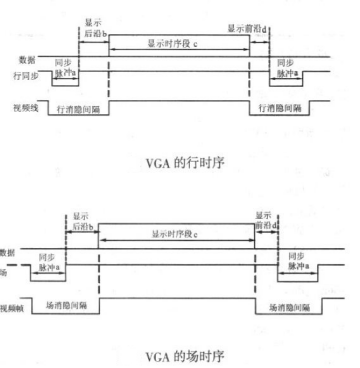

VGA时序图

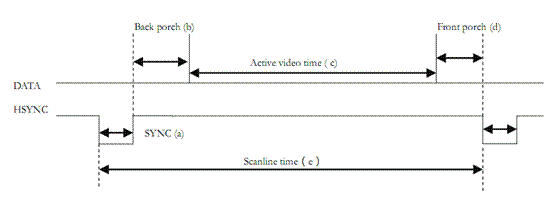

如上图VGA显示时序所示,VGA每次显示都需要同步信号,经过同步脉冲a,显示后沿b,显示时序段c,显示前沿d,然后是同步脉冲a,这样一个循环。

根据VGA协议标准,以640*480 60HZ为例,每秒钟要显示60次,一次显示800*525个点,其中640*480为显示时序段的有效点,其他的是为了同步时序的无效点。

如下图所示黄色区域为800个点的行周期,红色区域为525个点的场周期,只有行周期和场周期同时有效的橘色区域640*480才是有效显示区域。

VGA时序分析

一秒钟需要显示800*525*60个点,而时序的时钟频率是25MHZ,所以显示一个点的时间是25M/(800*525*60)=40ns.

行时序如上图所示:

a段的持续时间是96*40ns

b段的持续时间是45*40ns

c段的持续时间是646*40ns

d段的持续时间是13*40ns

e段的持续时间是800*40ns(e段是整个行周期)

场时序如上图所示:

o段的持续时间是2*e

p段的持续时间是30*e

q段的持续时间是484*e

r段的持续时间是9*e

S段的持续时间是528*e

只有行时序处于c段和场时序处于q段的时候发送的才是有效数据,一个行周期要显示640个点,一个场周期要显示480个行。

代码如下,代码只实现了VGA时序,时钟默认25MHZ。需要进一步修改。

- module vga_driver(

- clk ,

- rst_n ,

- din ,

- vga_hys ,

- vga_vys ,

- vga_rgb

- );

- parameter DATA_W = 16;

- input clk ;

- input rst_n ;

- input din ;

- output vga_hys ;

- output vga_vys ;

- output [DATA_W-1:0] vga_rgb ;

- reg vga_hys;

- reg vga_vys;

- reg [DATA_W-1:0] vga_rgb;

- reg [9:0] cnt_hys;

- reg [9:0] cnt_vys;

- wire add_cnt_hys;

- wire end_cnt_hys;

- wire add_cnt_vys;

- wire end_cnt_vys;

- reg display_area;

- always @(posedge clk or negedge rst_n)begin

- if(!rst_n)begin

- cnt_hys <= 0;

- end

- else if(add_cnt_hys)begin

- if(end_cnt_hys)

- cnt_hys <= 0;

- else

- cnt_hys <= cnt_hys + 1;

- end

- end

- assign add_cnt_hys = 1;

- assign end_cnt_hys = add_cnt_hys && cnt_hys== 800-1;

- always @(posedge clk or negedge rst_n)begin

- if(!rst_n)begin

- cnt_vys <= 0;

- end

- else if(add_cnt_vys)begin

- if(end_cnt_vys)

- cnt_vys <= 0;

- else

- cnt_vys <= cnt_vys + 1;

- end

- end

- assign add_cnt_vys = end_cnt_hys;

- assign end_cnt_vys = add_cnt_vys && cnt_vys==525-1 ;

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- vga_hys <= 0;

- end

- else if(add_cnt_hys && cnt_hys == 96-1)begin

- vga_hys <= 1;

- end

- else if(end_cnt_hys)begin

- vga_hys <= 0;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- vga_vys <= 0;

- end

- else if(add_cnt_vys && cnt_vys == 2-1)begin

- vga_vys <= 1;

- end

- else if(end_cnt_vys)begin

- vga_vys <= 0;

- end

- end

- always @(*)begin

- display_area = cnt_hys >= 141 && cnt_hys <= (141+646) && cnt_vys >= 32 && cnt_vys < (32+484);

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- vga_rgb <= 0;

- end

- else if(display_area)

- begin

- vga_rgb <= din;

- end

- else begin

- vga_rgb <= 0;

- end

- end

- endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号