FPGA用ROM存储正弦波数据

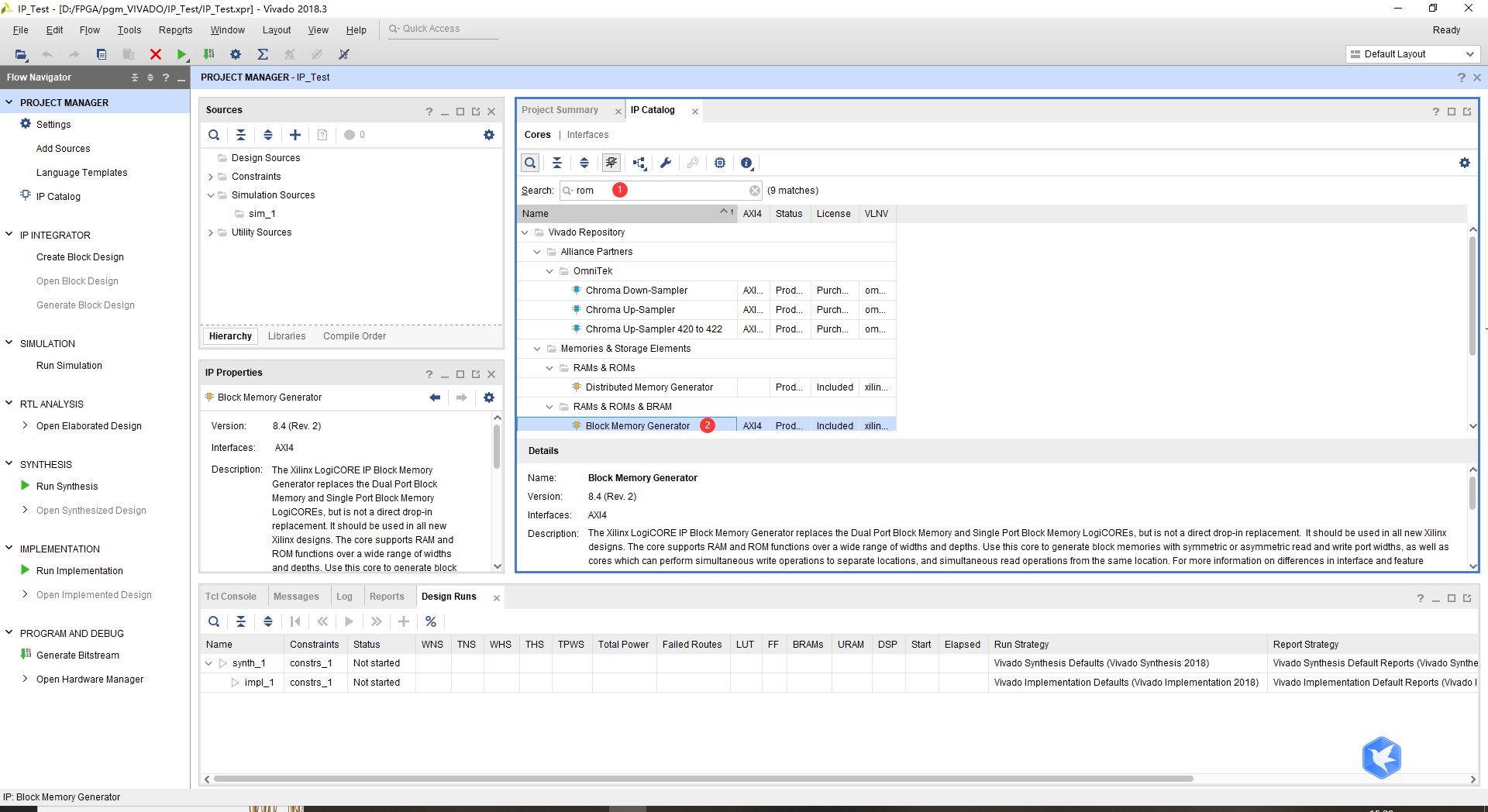

1、创建工程后点击IP Catalog

2、在搜索栏搜索ROM,并选择Block Memory Generator

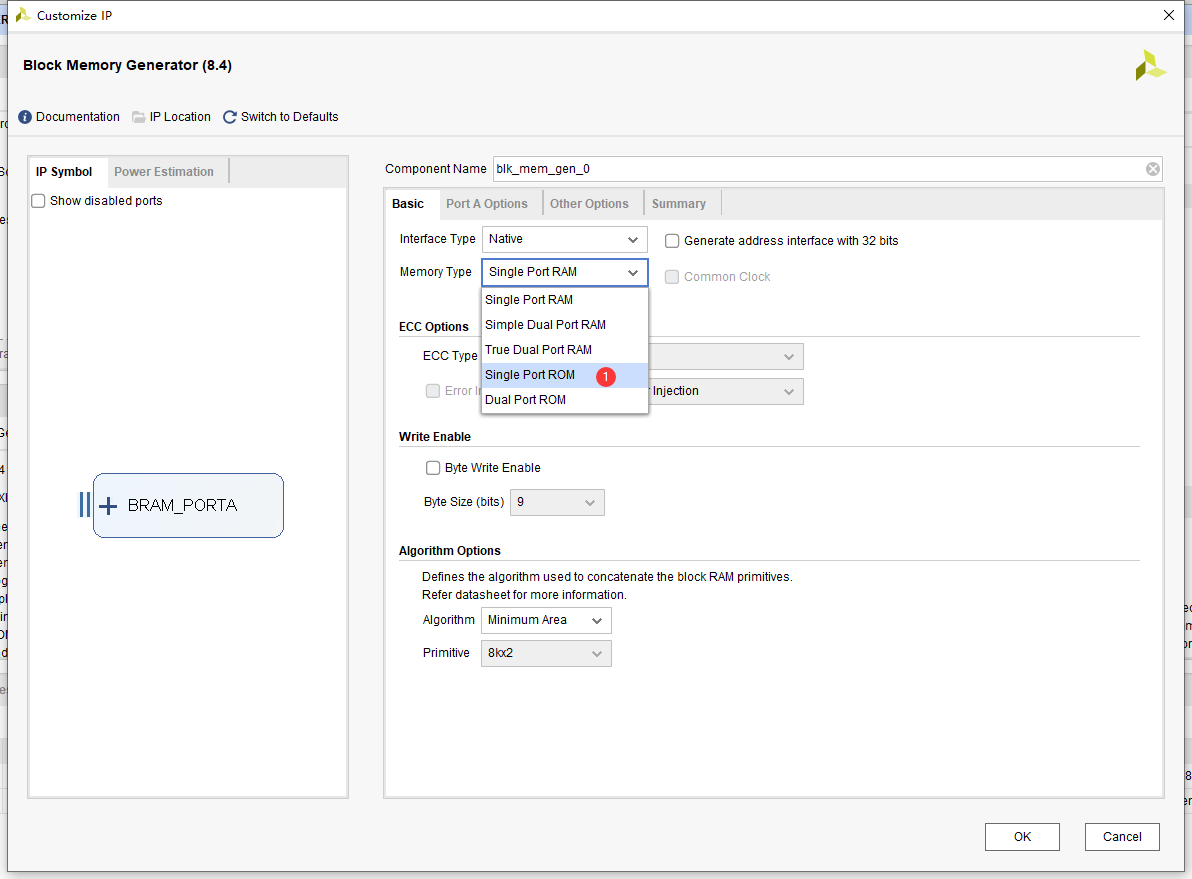

3、在弹出来的界面中选择单口ROM

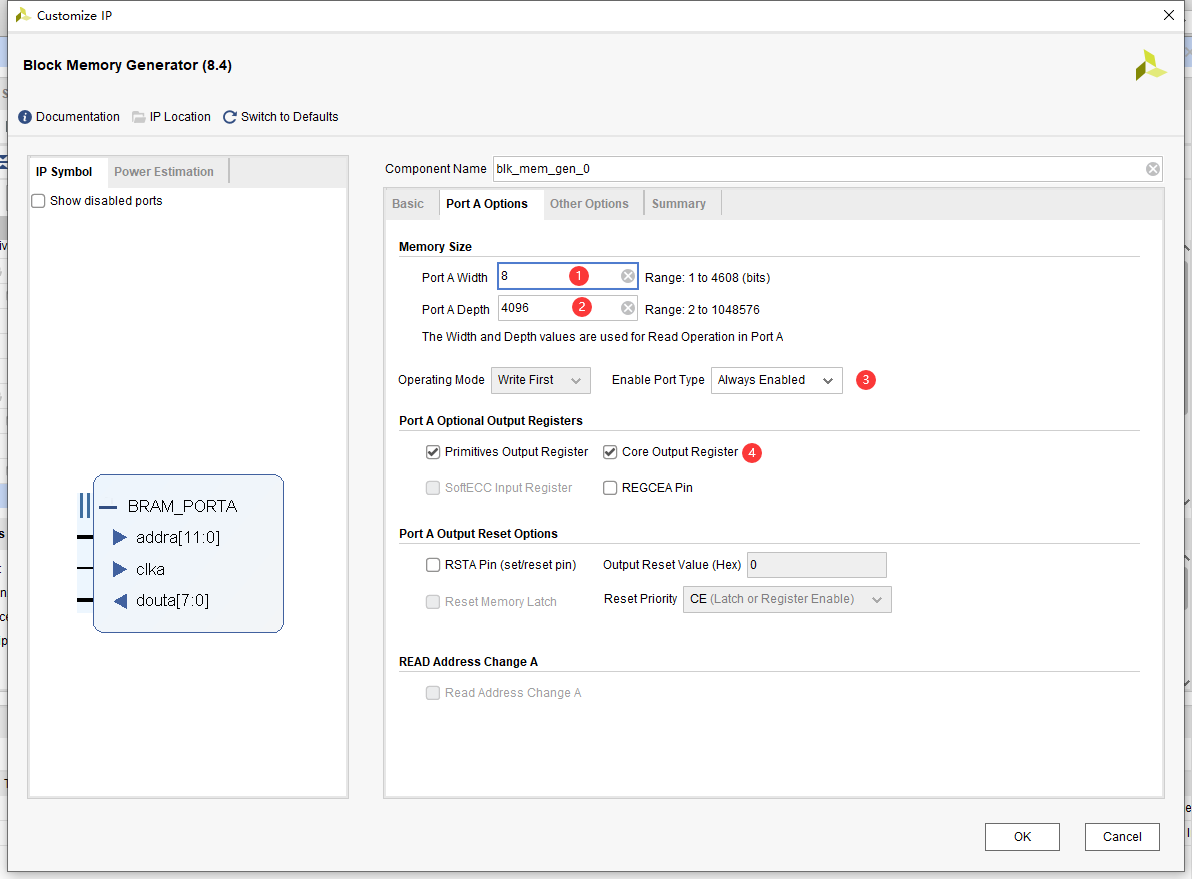

4、然后修改位宽和深度(这里根据我的需求设置为8位宽,4096深度);并把使能端口取消;勾上Core Output Register,使数据延迟一个时钟周期输出;由于有primitives Output Register的原因总的会延迟两拍输出。。

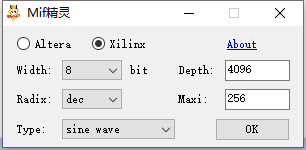

5、然后打开小梅哥的Mif精灵,选择Xilinx、位宽为8为,深度为4096、最大值为256然后点击OK后在软件所在的文件夹生成coe文件。

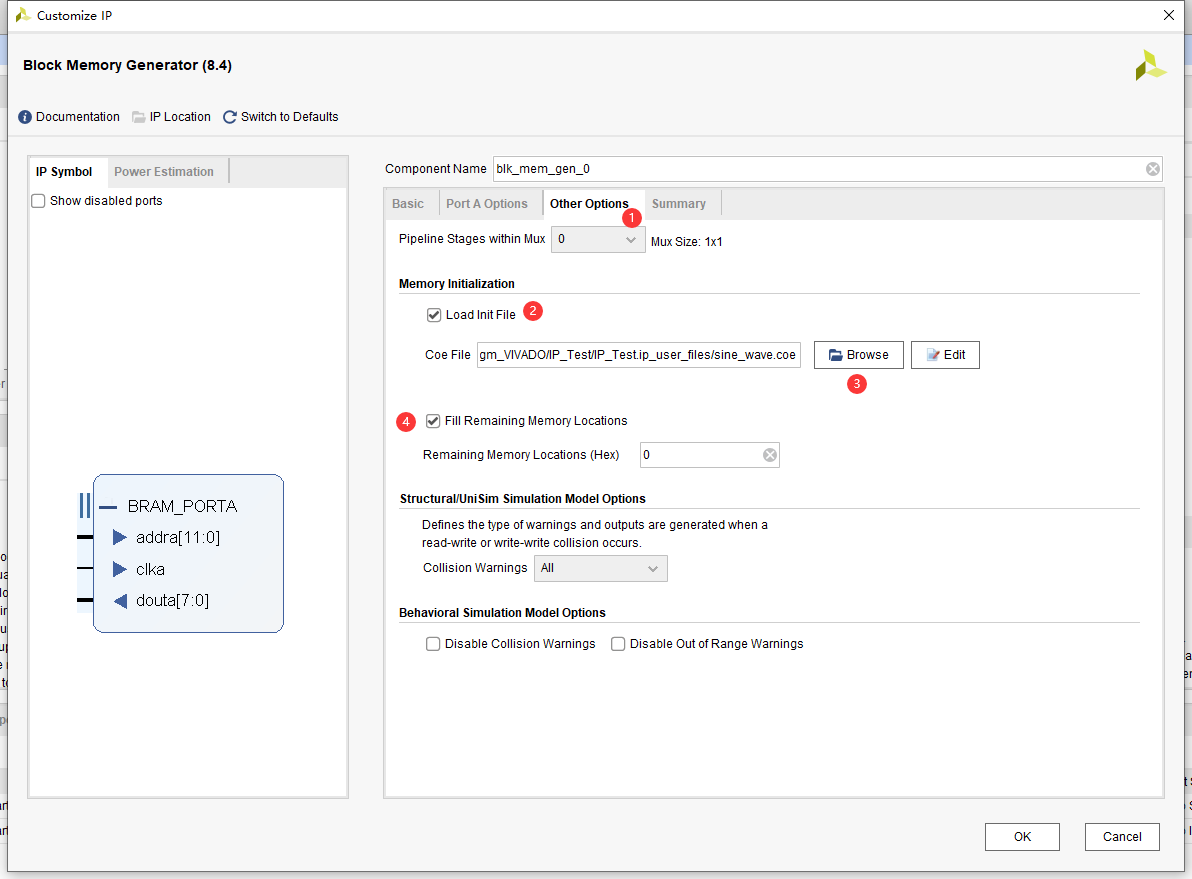

6、将coe文件放在找得到的地方,并来到Other Options,勾上Load Init File,点击Browse找到coe文件。第4步为将未用到的存储单元填充一个指定的数字,这里填充的数字为0。

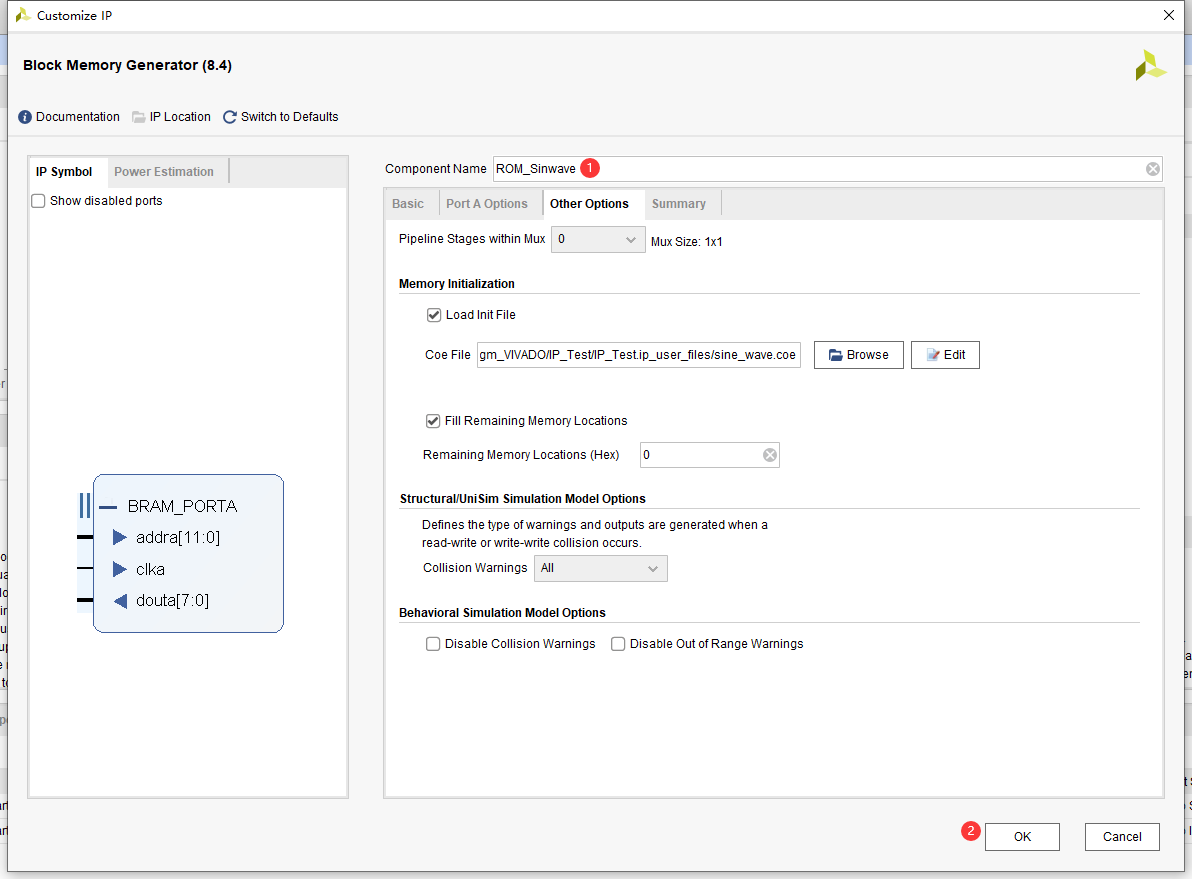

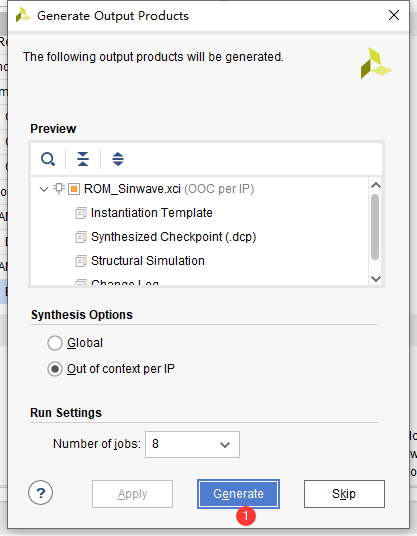

7、修改名字后点击OK生成该ROM核

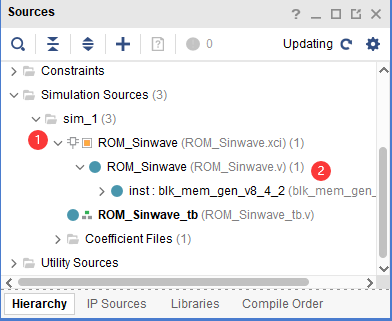

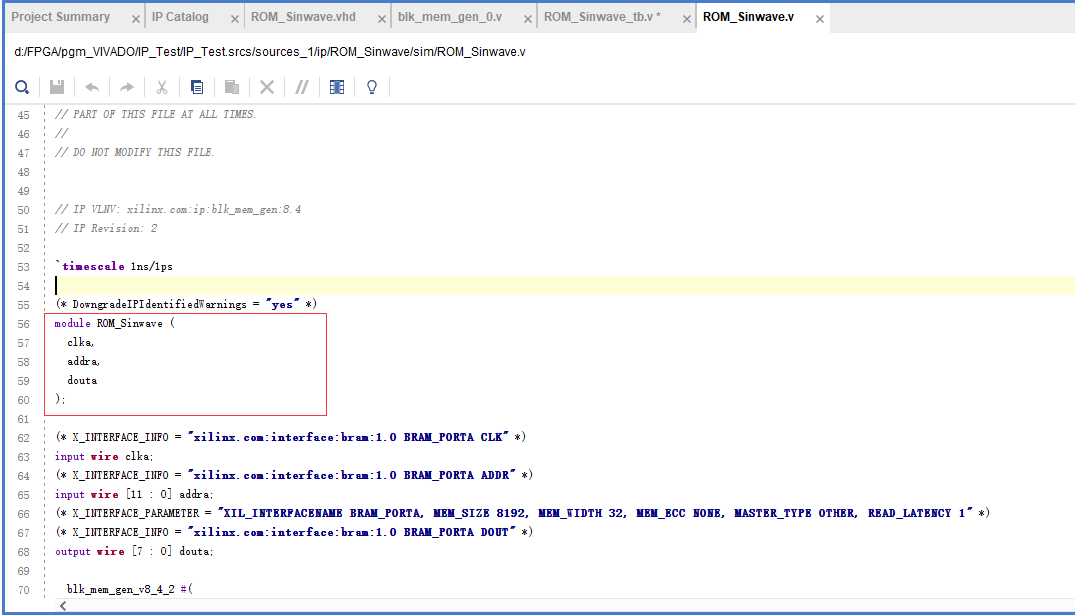

8、展开IP核,点击verilog文件,可以看到端口模块。(如果生成的是HDL文件,可以去旁边的IP Sources栏去找例化模板)

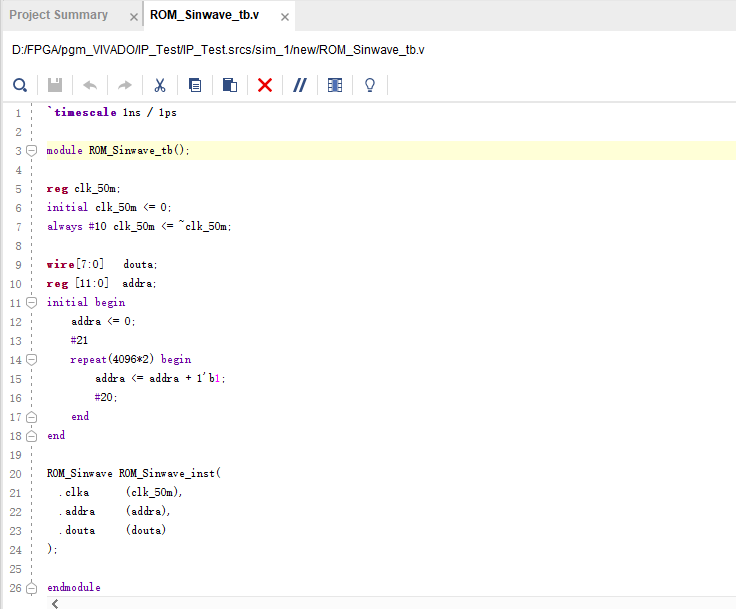

9、编写tb文件,例化IP核,进行仿真。

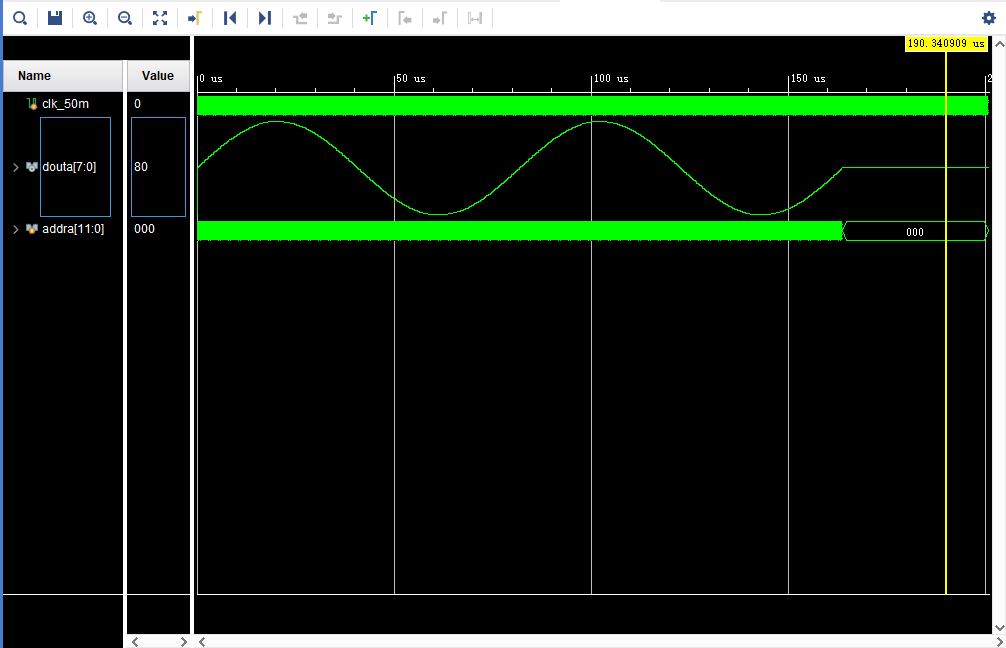

10、仿真结果

浙公网安备 33010602011771号

浙公网安备 33010602011771号