加/减法电路

基本门电路

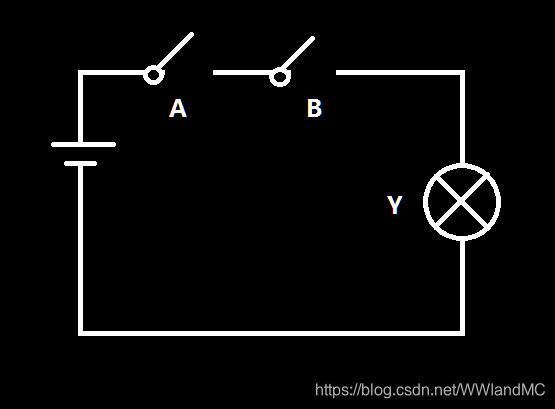

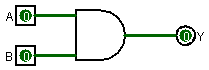

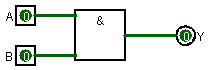

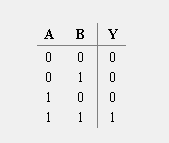

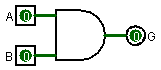

1.与门

门形状

真值表

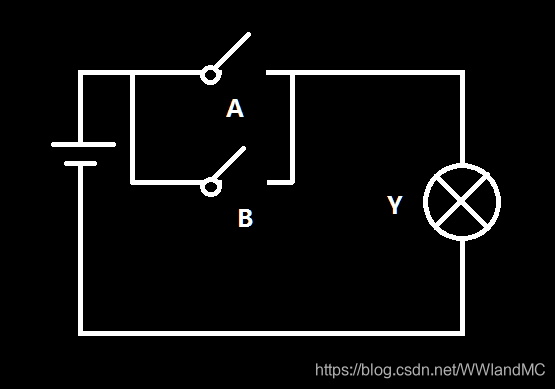

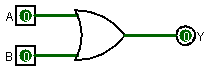

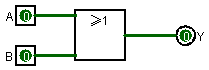

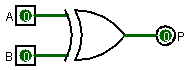

2.或门

门形状

大于等于1 可以理解为:当 A + B >= 1 时,Y输出高电平。

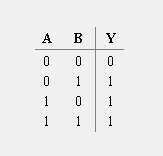

真值表

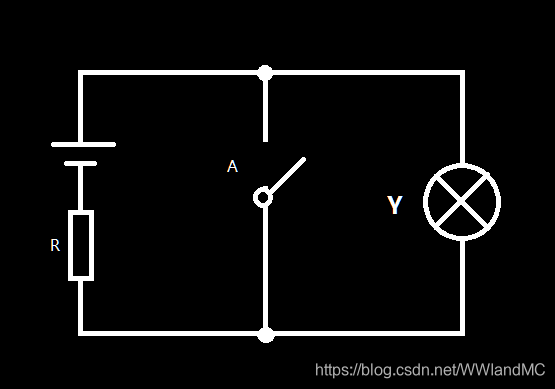

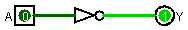

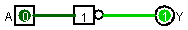

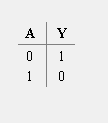

3.非门

门形状

真值表

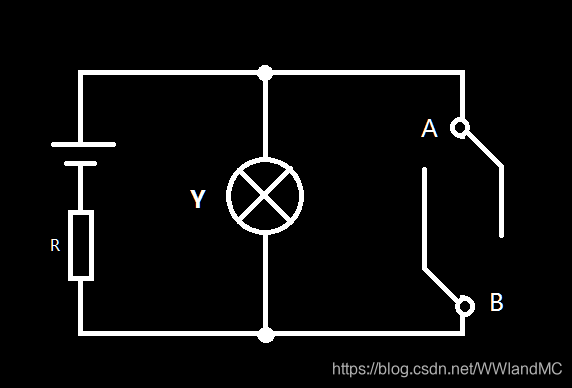

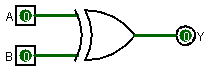

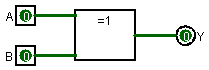

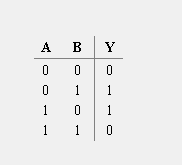

4.异或门

门形状

等于1 可以理解为: 当 A + B = 1时,Y输出高电平。

真值表

异或逻辑运算规则和加法规则很接近,可以用异或逻辑电路构成加法电路(没有进位的半加器)

典型逻辑元件

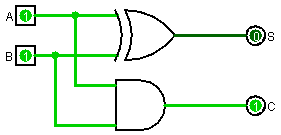

半加器

我的第一堂数电课-芯片内部是如何实现加法运算的?模拟信号和数字信号有什么区别?李永乐老师讲解门电路(2018最新)

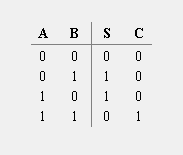

真值表

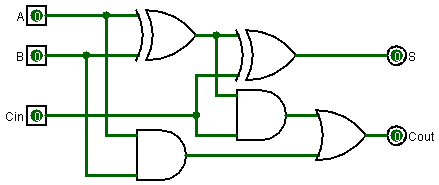

一位全加器

A为被加数

B为加数

Cin为相邻低位来的进位数

S为相加后输出本位

Cout为向相邻高位进位数

S = A ^ B ^ Cin

Cout = (A ^ B) & Cin + A & B

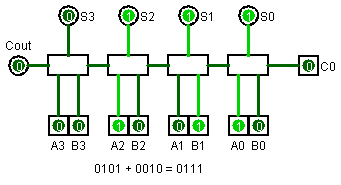

四位串行加法器

元件少成本低,可用于某些低速的专用运算器

串行进位链

C1 = A1B1 + (A1 ^ B1)C0 = G1 + P1C0

C2 = A2B2 + (A2 ^ B2)C1 = G2 + P2C1

C3 = A3B3 + (A3 ^ B3)C2 = G3 + P3C2

...

Cn-1 = An-1Bn-1 + (An-1 ^ Bn-1)Cn-2 = Gn-1 + Pn-1Cn-2

Cn = AnBn + (An ^ Bn)Cn-1 = Gn + PnCn-1

某位的进位信号的产生依赖于低位进位信号的产生。

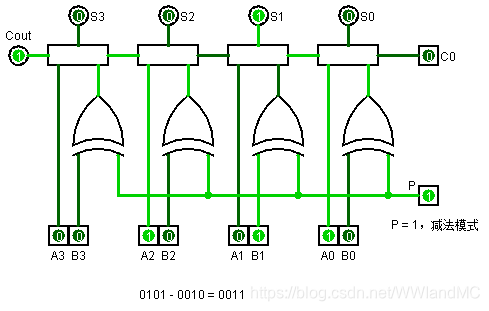

四位串行加/减法器

减法模式时,减数通过异或门按位取反,再相加。

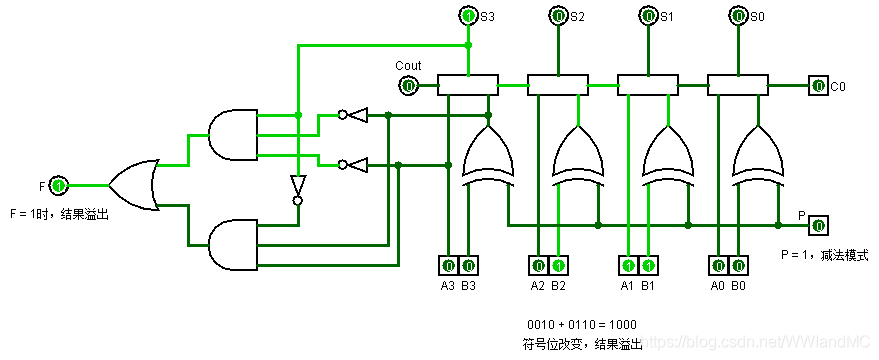

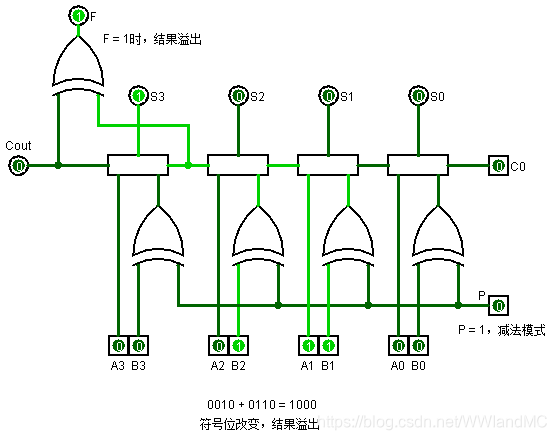

带溢出检测功能的串行加/减法器

1.检测同符号数之间相加是否溢出电路

2.检测最高有效数据位和符号位进位位是否同步

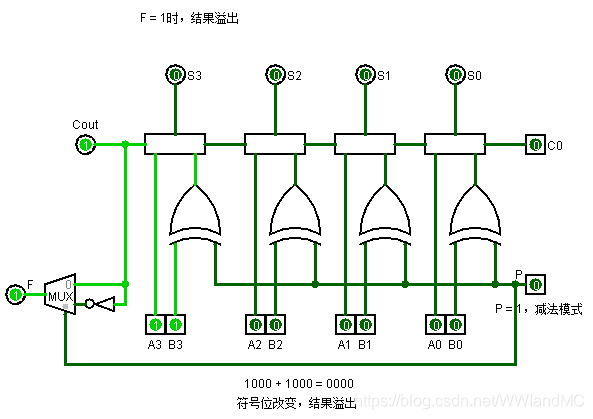

带无符号数溢出检测功能的串行加/减法器

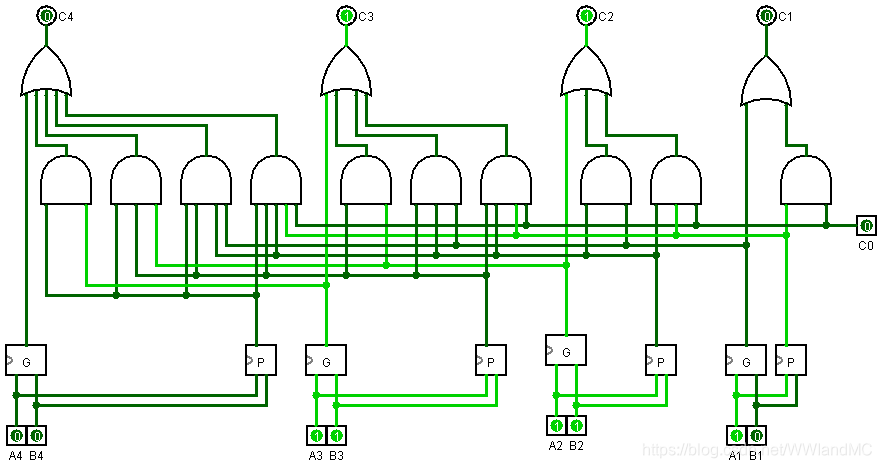

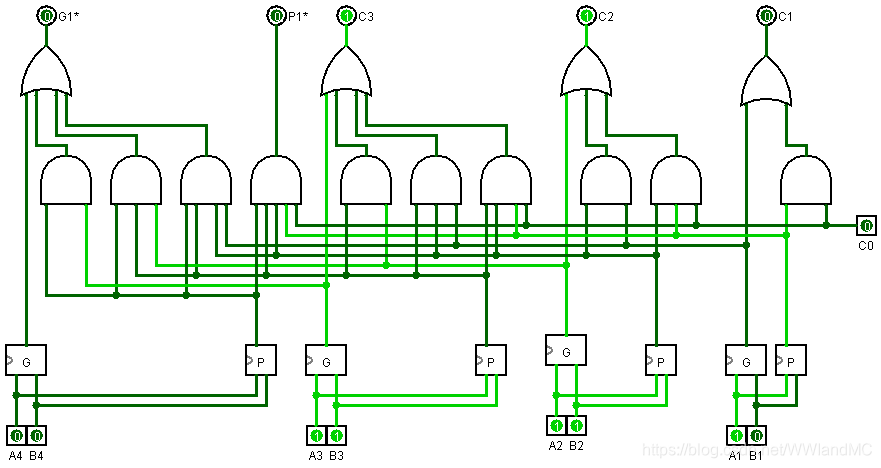

四位并行加法器

将串行进位链改写:

C1 = G1 + P1C0

C2 = G2 + P2C1= G2 + P2( G1 + P1C0) = G2 + P2G1 + P2P1C0

C3 = G3 + P3C2= G3 + P3( G2 + P2G1 + P2P1C0 ) = G3 + P3G2 + P3P2G1 + P3P2P1C0

...

Cn = Gn + PnGn-1 + PnPn-1Gn-2 + ... + PnPn-1Pn-2…P4P3P2P1G1 + PnPn-1Pn-2…P4P3P2P1G0

改写后,各进位信号的产生不再与相邻低位的进位信号有关,只与参加运算的数和C0有关。

按这组表达式的要求用逻辑电路形成各位的进位信号,则称形成这种进位信号的逻辑网络为并行进位链。

工程上对这组逻辑表达式的逻辑实现有一定困难。例如,表达式Cn的最后一项,在n = 16的情况下,就要求“与”门电路有17个输入端,逻辑电路的扇入系数不允许采用这种全并行方式。解决这个矛盾的基本方法,是根据元器件的特征将加法器分成若干个小组,对小组内的进位逻辑和小组间的进位逻辑作不同选择。

1. 组内并行,组间串行

每小组4位,每组内部采用并行进位结构,组间采用串行进位传递结构

C1 = G1 + P1C0

C2 = G2 + P2G1 + P2P1C0

C3 = G3 + P3G2 + P3P2G1 + P3P2P1C0

G4 = G4 + P4G3 + P4P3G2 + P4P3P2G1 + P4P3P2P1G0

来自低位的进位信号只有C0,送到高位小组的进位信号只有C4

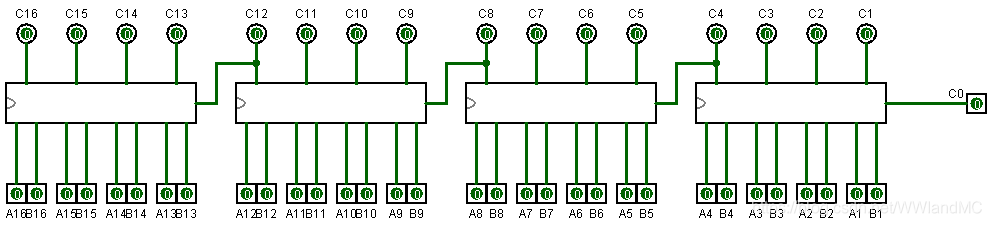

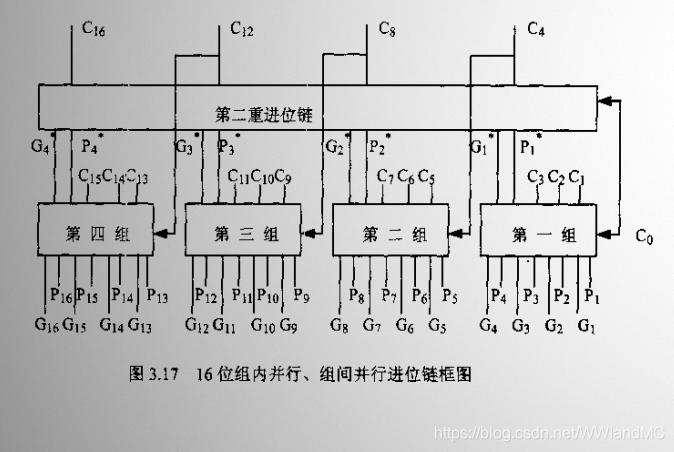

2. 组内并行,组间并行

仿照分析每一位进位信号的方法,将每个小组最高位进位分成进位传送函数和进位生成函数两个部分:

G4 = G4 + P4G3 + P4P3G2 + P4P3P2G1 + P4P3P2P1G0

- 只有最后一项 P4P3P2P1G0 依赖低位小组的进位信号,称为第一组的传送进位,其中P4P3P2P1为小组的传送函数,记作P1*

- 前面4项与C0无关,只与本小组内的Gi,Pi有关,称为第一小组的进位生成函数,记为G1*。

G1* = G4 + P4G3 + P4P3G2 + P4P3P2G1

因此 C4 = G1* + P1*C0

同理

- C4 = G1* + P1*C0

- C8 = G2* + P2*C4

- C12 = G3* + P3*C8

- C16 = G4* + P4*C12

继续展开得到:

- C4 = G1* + P1*C0

- C8 = G2* + P2*G1 *+ P2*P1*C0

- C12 = G3* + P3*G2* + P3*P2*G1*+ P3*P2*P1*C0

- C16 = G4* + P4*G3* + P4*P3*G2*+ P4*P3*P2*G1* + P4*P3*P2*P1*C0

- 第一小组产生G1*,P1*,C1,C2,C3,不在组内产生C4。

- 第二小组产生G2*,P2*,C5,C6,C7,不在组内产生C8。

- 第三小组产生G3*,P3*,C9,C10,C11,不在组内产生C12。

- 第一小组产生G4*,P4*,C13,C14,C15,不在组内产生C16。

各小组的进位生成函数和进位传送函数的逻辑表达式为:

- G1* = G4 + P4G3 + P4P3G2 + P4P3P2G1

- G2* = G8 + P8G7 + P8P7G6 + P8P7P6G5

- G3* = G12 + P12G11 + P12P11G10 + P12P11P10G9

- G4* = G16 + P16G15 + P16P15G14 + P16P15P14G13

- P1* = P4P3P2P1

- P2* = P8P7P6P5

- P3* = P12P11P10P9

- P4* = P16P15P14P13

进位产生次序如下:

_1. 产生第一小组的C1,C2,C3及所有Gi*,Pi*;

_2. 随后产生组间进位信号C4,C8,C12,C16;

_3. 然后再产生第二,三,四小组的C5到C15。

浙公网安备 33010602011771号

浙公网安备 33010602011771号