8086时序控制

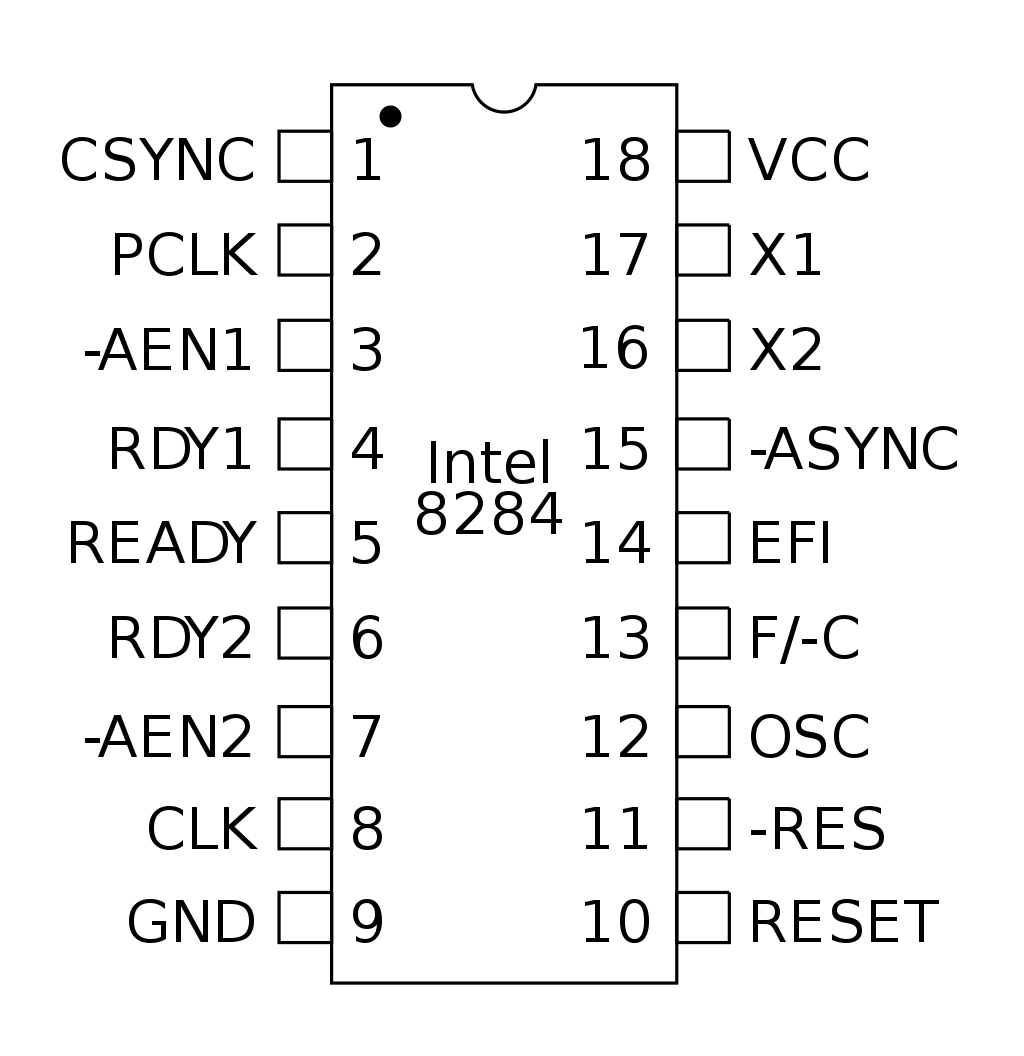

8284A 时钟产生器

8284A是8086/8088微处理器的一个辅助器件。负责时钟产生、RESET同步、READY同步以及TTL电平的外围设备时钟信号

| -AEN1和-AEN2 | Address Enable,地址允许 | 分别用来制约总线就绪信号RDY1和RDY2,CPU给出的READY信号受这两个输入信号控制 |

| RDY1和RDY2 | bus Ready,总线就绪输入 | 和-AEN1和-AEN2一起产生等待状态 |

| -ASYNC | 就绪同步旋转输入 | 为RDY1和RDY2输入选择一级同步或二级同步 |

| READY | 就绪输出 | 与8086/8088的READY输入引脚相连。此信号和RDY1和RDY2输入同步 |

| X1 和 X2 | 晶体振荡器引脚 | 与外部晶体相连,作为时钟产生器及所有功能的定时源 |

| F / -C | Frequency / -Crystal select | 为8284A选择时钟源。高电平时,外部时钟提供给EFI输入引脚,低电平由内部晶振提供定时信号 |

| EFI | External Frequency Input,外部频率输入 | 当F / -C引脚为高电平时,由EFI提供定时信号 |

| CLK | 为8086/8088及系统其他器件提供时钟输入信号 | CLK占空比为33% |

| PCLK | Peripheral CLocK | 频率是晶体或EFI频率的1 / 6,PCLK占空比为50%。为系统中其他外设提供时钟信号 |

| OSC | OSCillator output,振荡器输出 | 一个TTL电平信号,频率和晶体或EFI输入的频率相同。OSC输出在某些多处理器系统中为其他8284A提供EFI输入 |

| -RES | 复位输入 | 与8086/808的RESET引脚相连 |

| CSYNC | clock synchronization 时钟同步引脚。在多处理器系统中当EFI提供同步信号时使用。如果已使用内部晶振,该引脚必须接地 | |

| GND | 接地引脚 | |

| Vcc | 电源输入 | +5.0V,±10%电源输入 |

基本概念

- 时钟周期是计算机中最基本的时间单元,也是最短的时间度量单元。主频与时钟周期的转换关系:1 / 时钟周期 = 主频。例如,8086的主频为5MHz,时钟周期为200ns。

- BIU对存储器或外设读写一次所需要的时间,称为一个总线周期。在8086中,一个基本的总线周期由4个时钟周期组成,习惯上将4个时钟周期分别称为4个状态,即T1,T2,T3,T4。

- 执行一条指令所需要的全部时间,称为一个指令周期。一个指令周期可能包括若干个总线周期。不同的指令其指令周期可能不同。指令周期由一些基本的总线周期组成:存储器读/写,I/O端口读/写,终端响应。

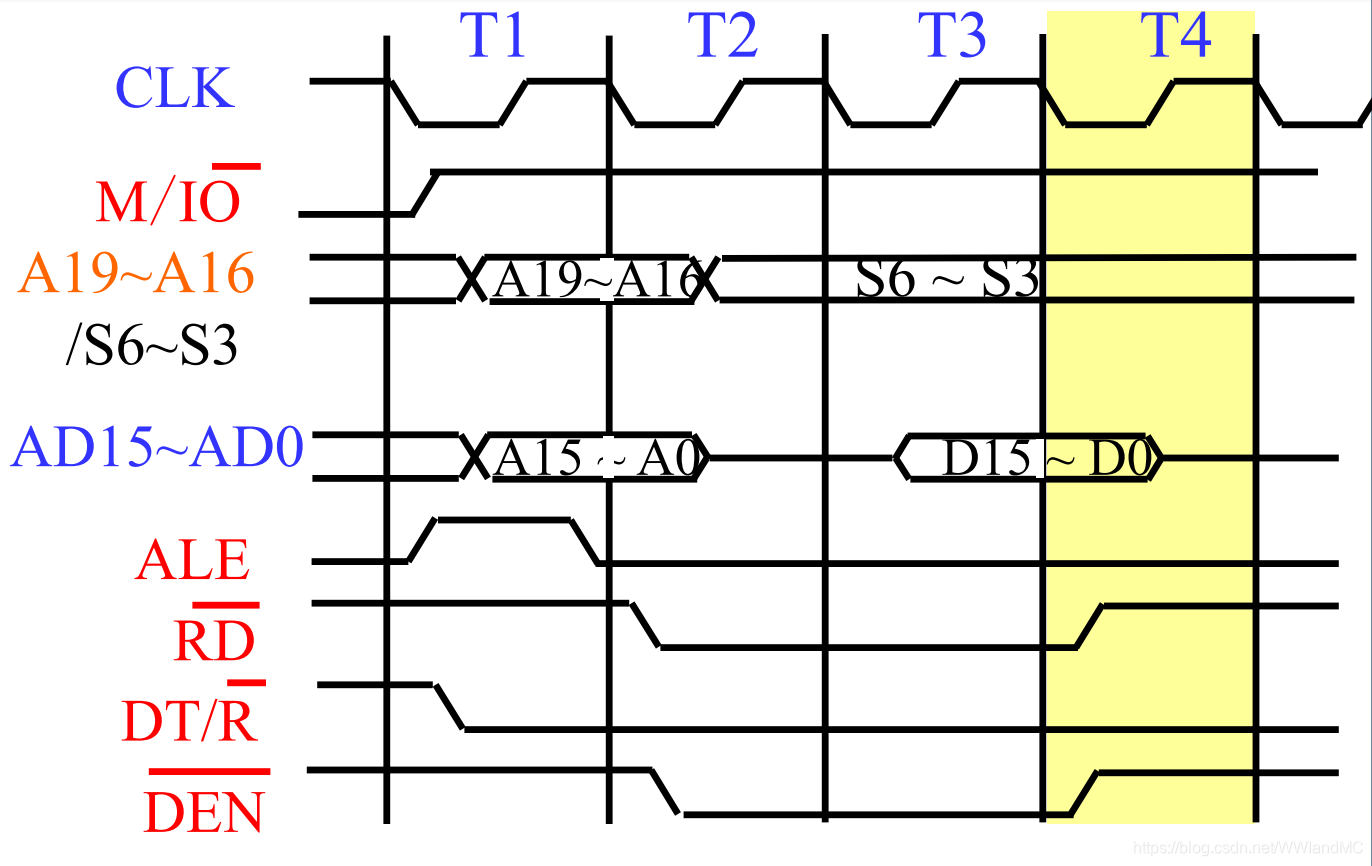

存储器读总线周期时序

T1状态

- M/IO*变高,CPU将对内存操作

- A19-A0上出现地址信号

- ALE上出现正脉冲信号(电平变化后又变回原状态)

- DT/R*变低,数据收发器处于接收状态

T2状态

- AD7-AD0变高阻态

- RD*变低,发给内存,CPU将进行读操作

- DEN*变低,允许数据收发器进行数据传送

T3状态

- AD7-AD0上出现数据信号,数据从内存单元送出

T4状态

- RD*变高,CPU从DB上读数据,将数据送到目的地(如寄存器)

- DEN*变高,数据收发器与总线断开,AD7-AD0变高阻态

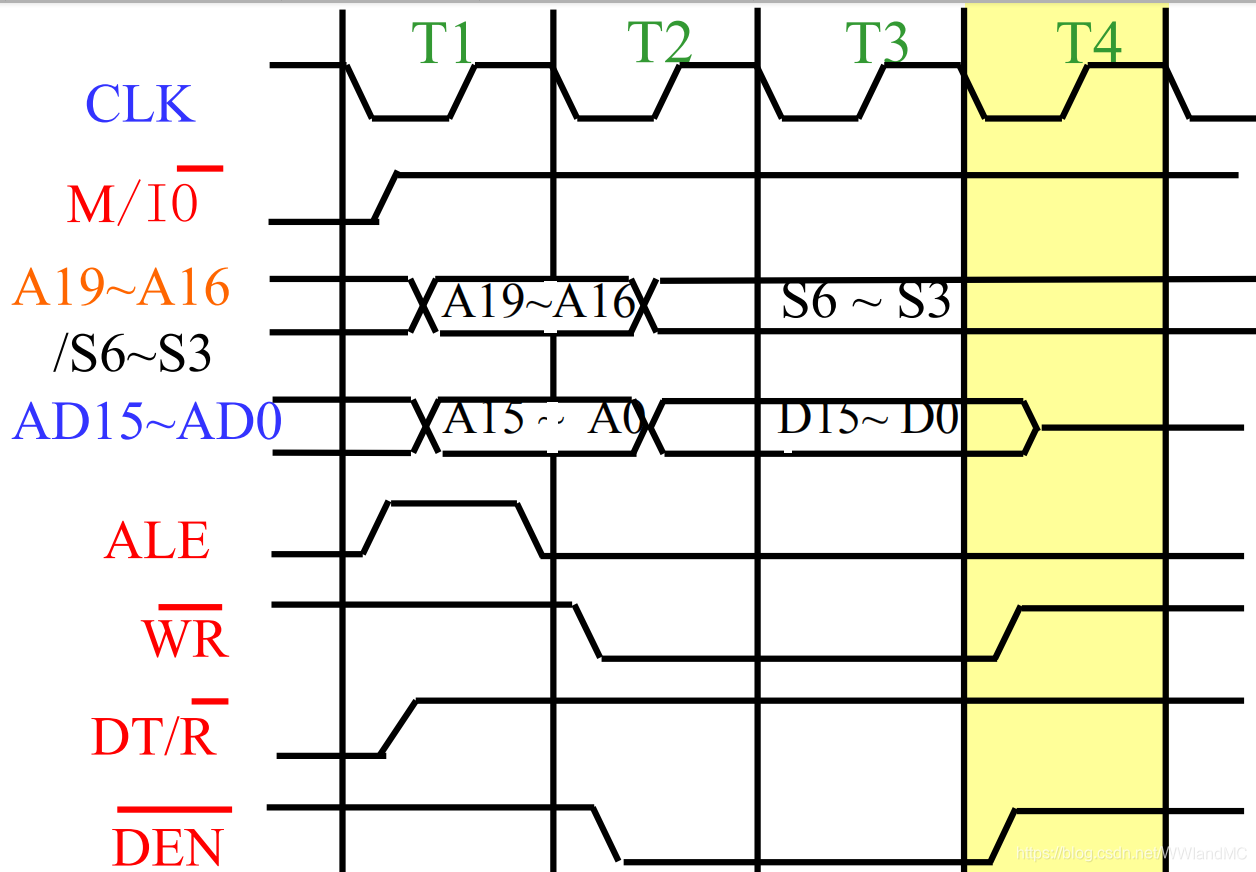

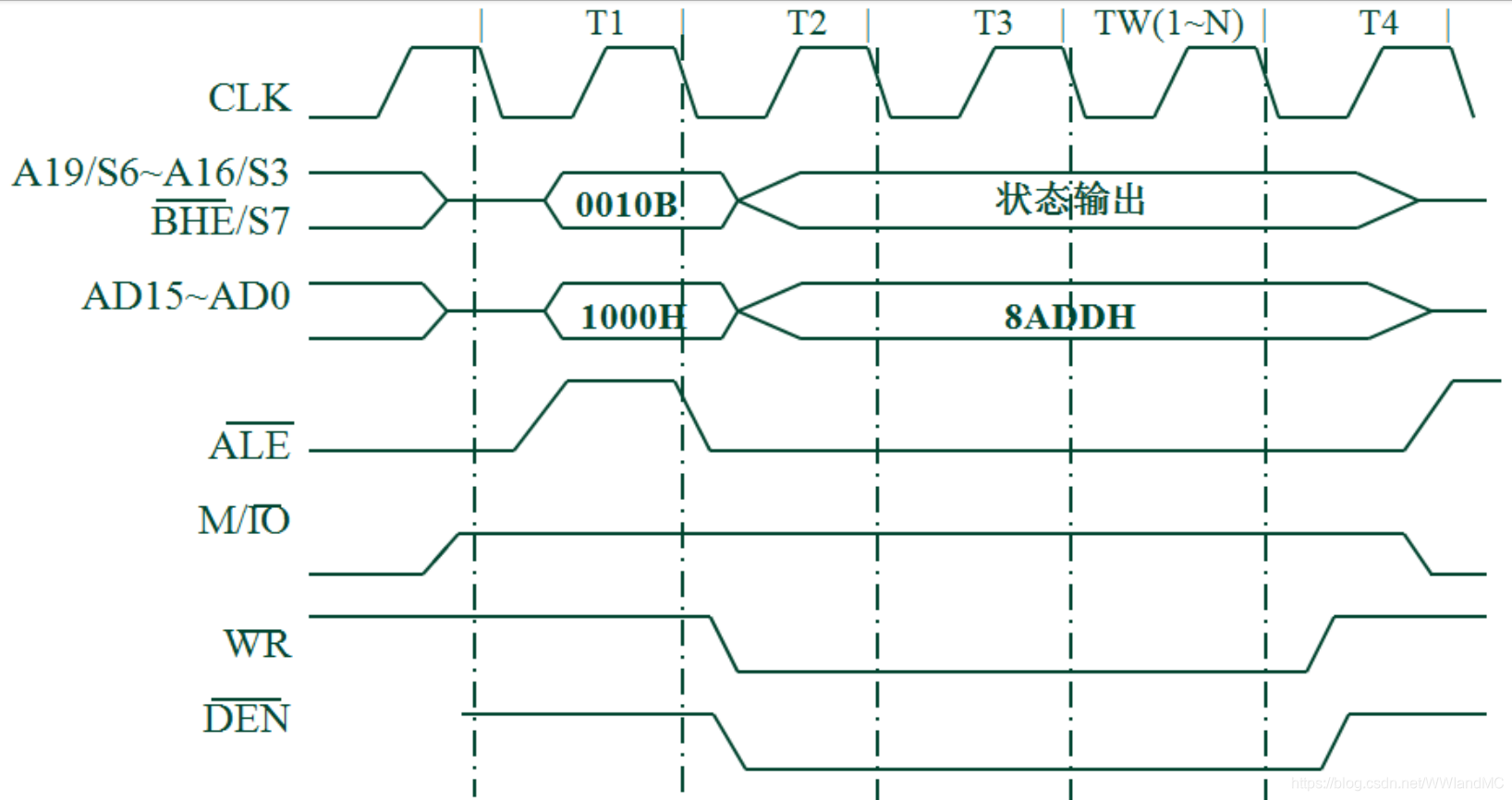

存储器写总线周期时序

T1状态

- M/IO*变高,CPU将对内存操作

- A19-A0上出现地址信号

- ALE上出现正脉冲信号(电平变化后又变回原状态)

- DT/R*变低,数据收发器处于发送状态

T2状态

- WR*变低,发给内存,CPU将进行读操作

- DEN*变低,允许数据收发器进行数据传送

- AD7-AD0上出现数据信号

T3状态

- 继续提供数据信号D7-D0

- 维持有关控制信号不变

T4状态

- WR*变高,将数据线上的数据写到目的内存单元

- DEN*变高,数据收发器与总线断开,AD7-AD0变高阻态

IO端口的读写总线周期

与存储器读写相比:

- M/IO*信号的电平不同

- CPU送出地址只出现在A15-A0

- 增加Tw等待周期(让CPU等待速度较慢的外设)

浙公网安备 33010602011771号

浙公网安备 33010602011771号