RAM

Random Access Memory

任何一个存储单元的内容都可以随机存取,且存取时间与存储单元的物理位置无关

技术指标

| 存储字长 | 主存的一个存储单元所包含的二进制位数 |

| 存储容量 | 主存能存放二进制代码的位数。存储容量 = 单元个数 x 字长 |

| 存储速度 | 由存取时间(Memory Access Time)和存取周期(Memory Cycle Time)来表示。MAT是指启动一次存储器操作(RD 或 WR)到完成该操作所需的全部时间。MCT是指存储器进行连续两次独立的存储器操作(如连续两次读操作)所需的最小间隔时间,通常MCT大于MAT |

| 存储器带宽 | 单位时间内存储器存取的信息量。决定了以存储器为中心的机器获得信息的传输速度 |

| 大端小端 | Big-endian:最高字节地址(MSB)是数据地址;Little-endian:最低字节地址(LSB)是数据地址 |

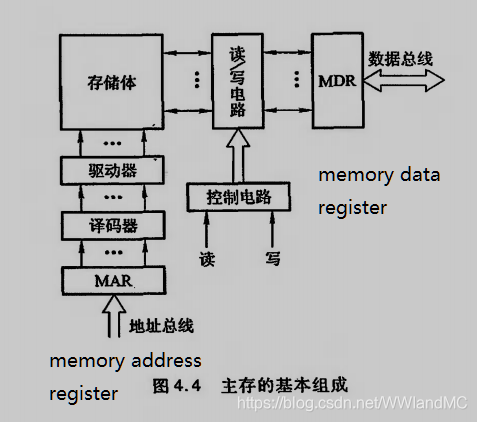

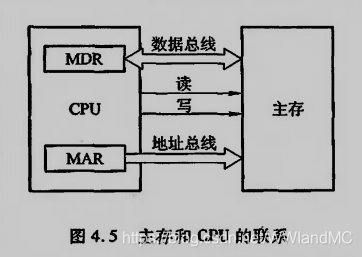

半导体存储芯片

采用超大规模集成电路制造工艺,在一个芯片内集成:

| 具有记忆功能的存储矩阵 | |

| 译码驱动电路 | 能把AB送来的地址信号翻译成对应存储单元的选择信号,该信号在读 / 写电路的配合下完成对被选中单元的读 / 写操作 |

| 读 / 写电路包括读出放大器和写入电路 | 用来完成读 / 写操作 |

|

|

|

地址是单向输入的,其位数与芯片容量有关。

数据线是双向的,其位数与芯片可读出或写入的数据位数有关。

地址线和数据线的位数共同反映存储芯片的容量。

例:地址线为14根,数据线为8根,则其容量为 16K × 8位

控制线分:

| 写控制线 WE* | |

| 片选控制线 CS | 由于半导体存储器是由许多芯片组成的,片选信号用来选择哪个存储芯片 |

相关术语

| MOS | Metal-Oxide-Semiconductor,即场效应管 |

| CMOS | Complementary MOS,即互补对称MOS |

P(Postive)型半导体:又称空穴导电半导体,在纯硅中掺入微量3价元素,与周围4价硅原子共价结合的时候少1个电子

N(Negative)型半导体:又称电子型导电半导体,在纯硅中掺入微量5价元素,与周围4价硅原子共价结合的时候多1个电子

PN互补半导体特点:两端分别是P型和N型,电流只能从P流向N

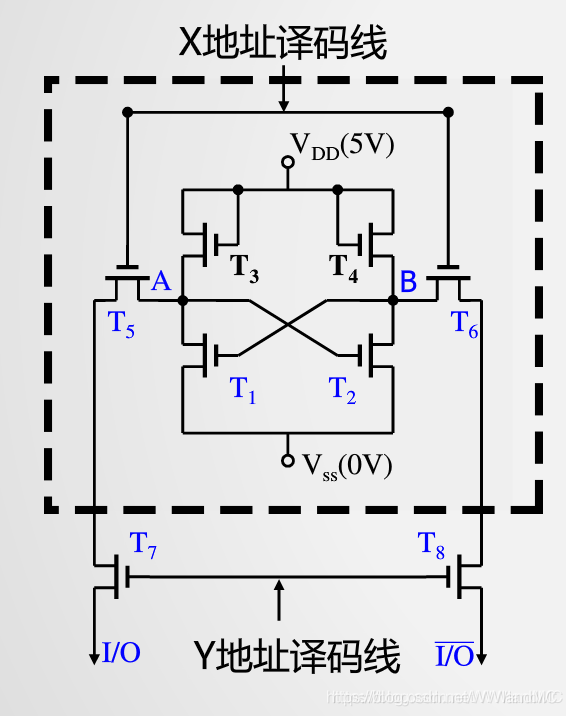

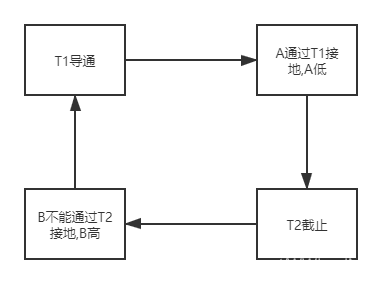

六管MOS SRAM存储单元工作原理

| 工作管 | T1,T2 | 保存数据 |

| 负载管 | T3,T4 | 补充电荷 |

| 门控管 | T5,T6,T7,T8 | T5,T6受行地址选择信号控制; T7,T8受列地址选择信号控制 |

写过程

前提:X有效(T5T6导通,A与I/O连通)且Y有效(T78导通,B与 N I/O导通)

写入0:

写入1:

读过程

前提:X有效(T5T6导通,A与I/O连通)且Y有效(T78导通,B与 N I/O导通)

读出0:

读出1:

通过判断I/O线有无电流即可判断读出的是1还是0。

保持状态

X,Y选通信号撤销后,T5T6T7T8均截止。

保持1:

保持0:

半导体存储芯片的译码驱动方式

单译码结构:用一根字选择线直接选中一个存储单元的各位。只适用用容量不大的存储芯片。

双译码结构:被选单元由X,Y两个方向的地址决定。

SRAM芯片实例

| 地址线A9-A0 | 存储单元数量 = 210 bytes = 1KB |

| 数据线I/O4-I/O1 | 每个存储单元有4位 |

| 读写控制线WE* | 低电平为写操作,高电平为读操作 |

| 片选线CS* | 低电平时选中此存储芯片 |

| 电源线 GND VCC | 提供电源输入和参考地电平 |

|

|

| 行地址和列地址的位数不能从外部引脚判断,需要得知其内部结构中才能看出,如图所示,2114行地址为6 bit,列地址为4 bit。 |

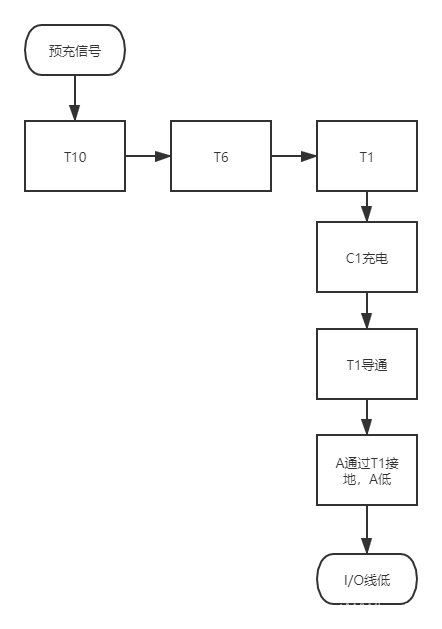

四管MOS DRAM基本单元工作原理

写过程

前提:X有效(T5T6导通,A与I/O连通)且Y有效(T78导通,B与 N I/O导通)

写入0:

写入1:

读过程

前提:X有效(T5T6导通,A与I/O连通)且Y有效(T78导通,B与 N I/O导通)

- 读0:

- 读1:

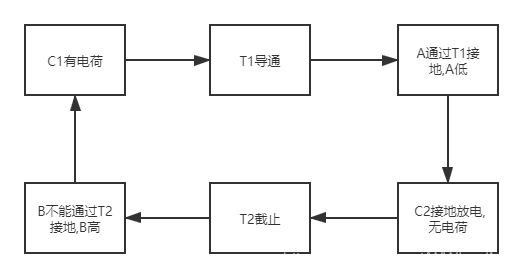

保持操作

X,Y选通信号撤销后,T5T6T7T8均截止。

保持1:

保持0:

刷新

随着时间的推移,栅极电容上的电容会泄露,存储元本身不能补充电荷,需要外加电路给存储元充电,所谓刷新。

前提:(X选通信号有效,Y选通无效)

- C2有电荷,C1无电荷:

- C1有电荷,C2无电荷:

读出时(XY均有效)可以刷新,但刷新时(仅X有效)不读出。

刷新概念

- 刷新和重写(再生)是两个完全不同的概念。

- 重写是随机的,刷新是定时的。存储单元在破坏性读出才需要重写。如果不定时为存储体补充电荷,信息会丢失。

- 重写一般按存储单元操作,刷新按存储矩阵的一行为单位进行。

- 刷新周期:两次刷新之间的时间间隔,双译码结构的DRAM刷新按行进行,需知道存储矩阵的行数

- 刷新地址由刷新地址计数器给出(刷新需要遍历存储器所有地址,而CPU指令集是离散的,不能完成这项工作)

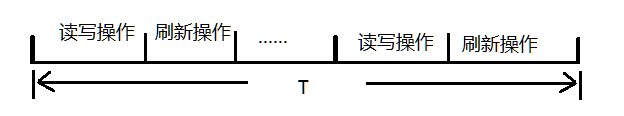

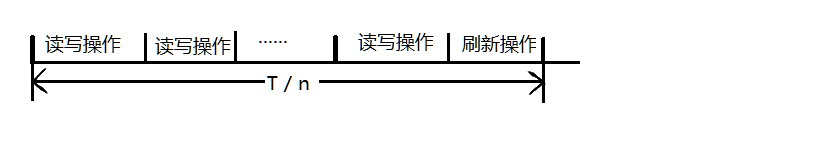

刷新方式

- 集中刷新

集中刷新时,有一段连续的时间不能进行存取访问,这段时间称为死时间 - 分散刷新

读写一次,刷新一次

虽然不存在死时间,但刷新过于频繁,不适合高速存储器 - 异步刷新

根据行数将刷新周期均分,前一段时间读写,后一小段时间刷新

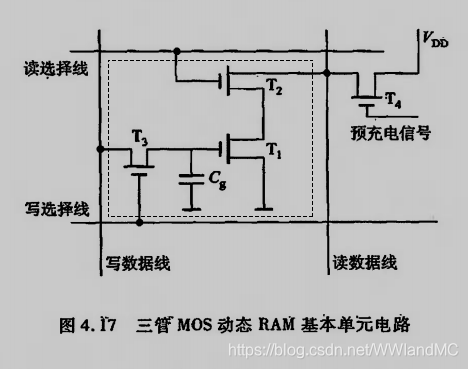

三管MOS DRAM基本单元工作原理

在存储矩阵中,每一列共用一个T4

写过程

读过程

读出线的高低电平与原存信息相反

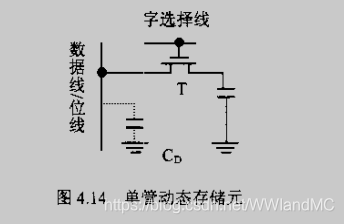

单管MOS DRAM基本单元工作原理

写过程

读过程

读出后,存储内容就被破坏,需要重写。

保持

由于MOS管的栅极电阻很大,泄露电流很小,在一定时间内存储的信息的电荷可以维持住

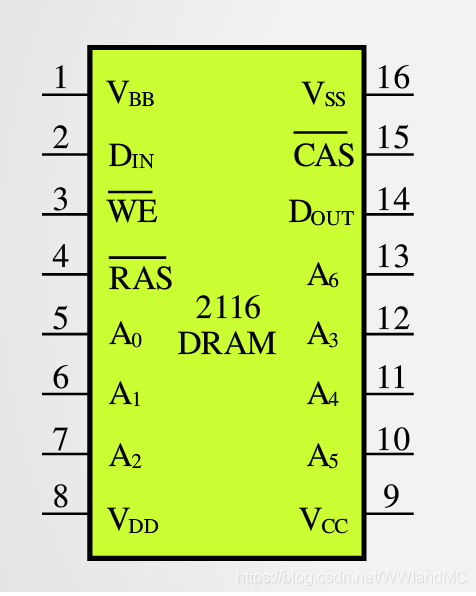

DRAM芯片实例

| 地址线A6-A0 | 由于地址线复用,存储单元数量 = 27*2 bytes = 24 * 210 = 16KB |

| 数据线DIN,DOUT | 每个存储单元有1位 |

| 读写控制线WE* | 低电平为写操作,高电平为读操作 |

| RAS* CAS* | RAS(Rank)行选择信号 CAS(column)列选择信号,RAS兼为片选信号 |

| 电源线 GND VCC | 提供电源输入和参考地电平 |

SDRAM

Synchronous DRAM

同步DRAM

存储特点:

- 采用DRAM存储结构,但半导体工艺和工作机制较DRAM有改进

如果CPU的速度比DRAM快,CPU要等待DRAM完成操作,等待降低了CPU的执行速度

- 和CPU时序同步,以CPU-存储总线的最高速度运行,不需要插入等待状态

- CPU给出的地址和控制信号会被SDRAM锁存,直到指定的时钟周期数后再响应(时钟上升沿),期间CPU可以执行其他任务,无须等待

- 具备对芯片的行、列单元整体锁定功能

- CPU发出一个地址可以连续访问一个数据块(通常为32字节)

- 采用了支持并行操作的分组结构,多个存储体可以轮流工作,与外部交互数据

DDR SDRAM

Double Data Rate SDRAM

双倍数据率SDRAM

存储特点:

- 和CPU时序同步,时钟上升沿和下降沿各触发一次存储读写操作,每周期两次向CPU送出数据

- 提供数据预读

| DDR1 | DDR2 | DDR3 | DDR4 | DDR5 |

|---|---|---|---|---|

| 2位 | 4位 | 8位 | 16位 | 32位 |

从1到5:存储器频率越来越高,带宽越来越高,工作电压越来越低,能耗越来越低

GDDR SDRAM

Graphics Double Data Rate DRAM

专用于显存的DDR存储器

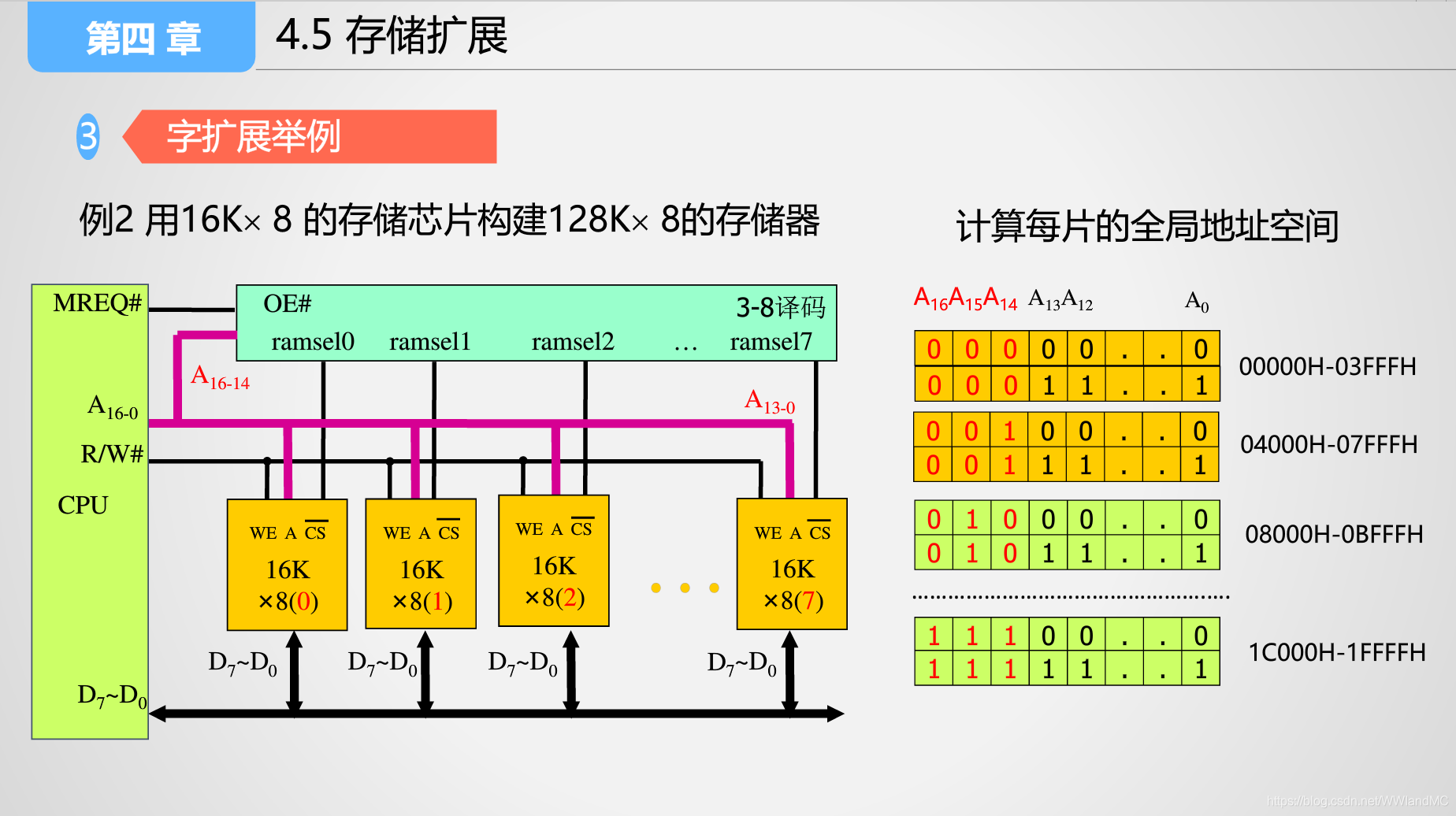

RAM存储器扩展

扩展方案:

-

位扩展:多芯片存储器的A,CS,WE相应并联,D分别引出,并行工作。

按整数边界存放的要求:

如果存储字长为8位,则将CPU的A0与存储器的A0连接;

如果存储字长为16位,则将CPU的A1与存储器的A0连接, CPU的A0用于选择从存储器中读出的16位中的哪个8位;

如果存储字长为32位,则将CPU的A2与存储器的A0连接, CPU的A1A0 用于选择从存储器中读出的32位中的哪个8位或哪个16位;依次类推 -

字扩展:各芯片A,D,WE相应并联,用CS来区分各芯片的地址范围

-

字位扩展:两者结合

SRAM和DRAM的对比

- DRAM由于使用简单的单管单元作为存储单元,因此每片容量较大,约是SRAM的4倍;

- 由于DRAM的地址是分批进入的(复用),DRAM的外部引脚比SRAM少很多,封装尺寸也比较小

- 存储量大和封装小的特点使得同一块电路板上,使用DRAM比SRAM能多出4倍的存储空间

- DRAM价格比较便宜,大约只有SRAM的1 / 4

- DRAM由于使用动态元件,速度比SRAM低

- DRAM需要刷新,浪费时间,需要配套的刷新电路,占用一部分功率

- SRAM一般用作容量不大的高速存储器(如Cache),DRAM一般用作主存

- DRAM和SRAM的共同特点是断电信息消失

浙公网安备 33010602011771号

浙公网安备 33010602011771号