Cache

什么是Cache

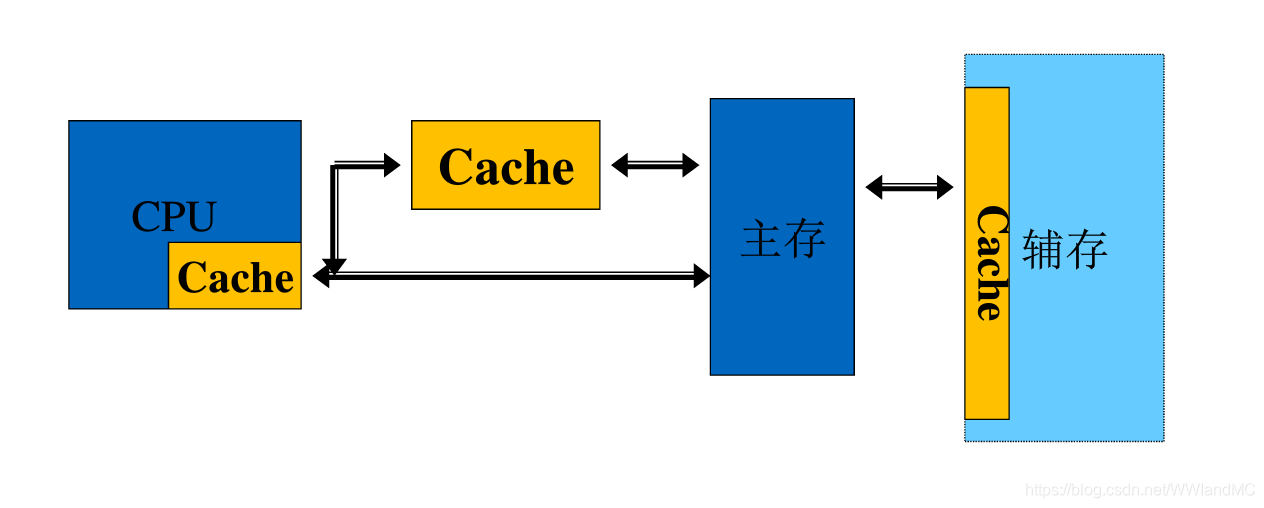

高速缓存(Cache)存储器是一种位于CPU和主存之间的规模较小但工作速度较高的缓冲存储器,通常由SRAM组成。

Cache的功能

目的:使存储器的速度逼近可用的最快存储器的速度,同时以比较便宜的半导体存储器的价格提供一个大的存储器容量

理论基础

局部性原理

在一个较短时间间隔内,CPU对局部范围的存储器地址频繁访问,而对此地址范围之外的地址访问很少,这种现象被称为程序访问的局部性。

Cache的结构

字块的划分

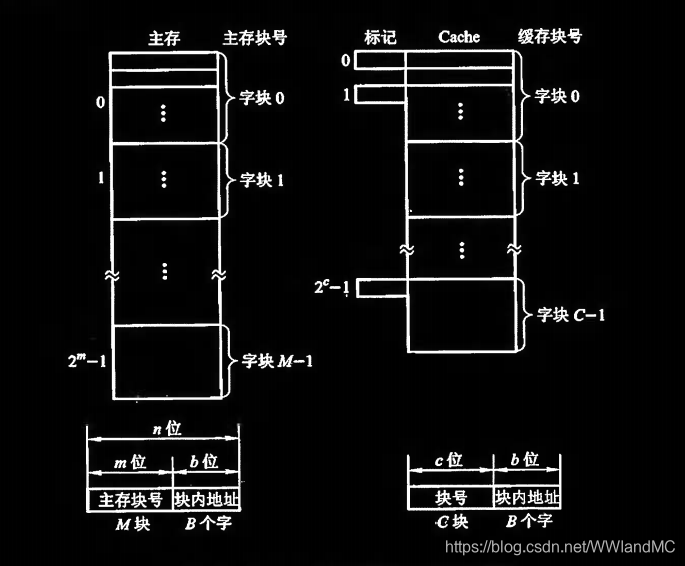

设主存有2n个单元,地址码为n位,将主存分块(block),每块内有2b个字节:

设n = m + b,有主存块数M = 2m,块内字节数 = 2b。

Cache地址码为(c + b)位,Cache的容量 = 2c+b,Cache的块数为2c,块内字节数与主存相同。

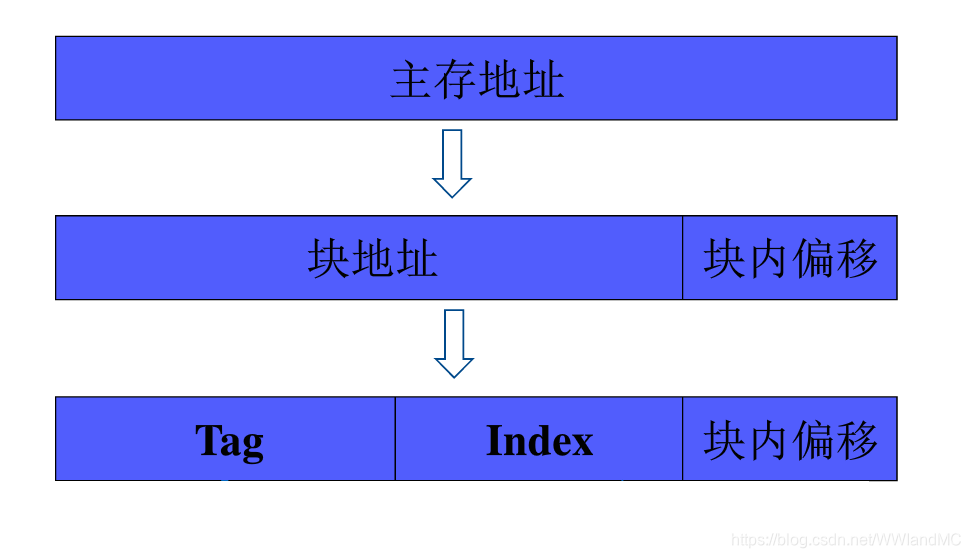

进一步划分主存地址码,块地址分为

- Tag:判断数据是否在Cache

- Index:数据在Cache的位置

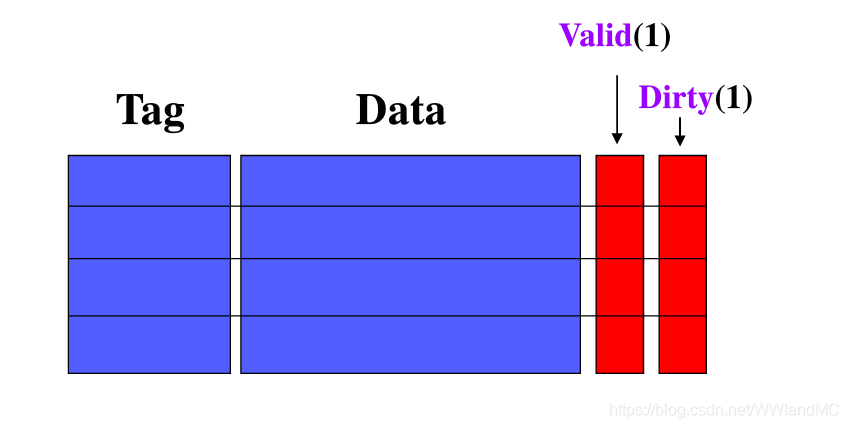

Cache被分成若干行(line),每行的大小与主存块相同

Cache每行包含四部分:

| Tag | 主存地址剥离出来的一部分特征信息,用来判断数据是否在Cache |

| Data | 与主存交换的数据块 |

| Valid | 表示Cache中的数据是否有效 |

| Dirty | 在写回策略中表示主存中的数据是否是最新 |

相联存储器

相联存储器既可以按地址寻址,又可以按内容寻址,又称为按内容寻址存储器。

逻辑视图

工程视图

作用:判断CPU要访问的内容是否在Cache中

查找依据key:根据不同规则从主存地址中抽取的部分内容

工作原理:硬件并发查找

| 检索寄存器 | 存放检索字 |

| 屏蔽寄存器 | 存放屏蔽码 |

| 存储体 | 存放有效位,标记,数据等信息 |

| 符合寄存器 | 存放Cache命中行信息 |

| 代码寄存器 | 存放从存储体中读出的代码,或存放写至存储体中的代码 |

工作流程:

- 从地址中剥离出查找依据key

- 以key为关键字全局硬件并发比较

- 根据符合寄存器的信息取出命中行的数据

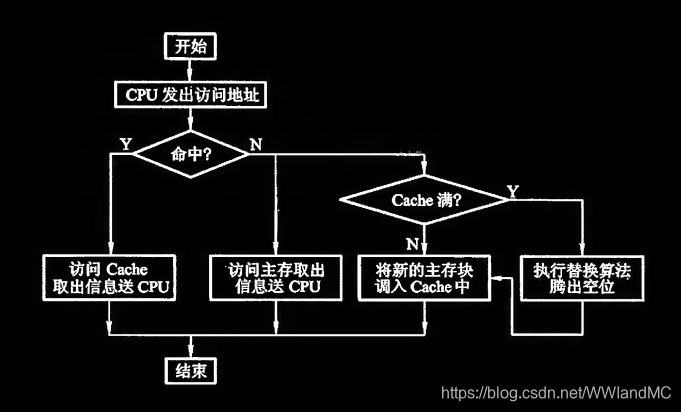

Cache读流程

- CPU与Cache之间,通常一次传送一个字

- Cache与主存之间,通常一次传送一个块

Cache写流程

如果程序执行过程中要对该字块的某个单元进行写操作,就会遇到如何保持Cache与主存一致性的问题。

- 写穿策略(Write Through)

每次写入Cache同时也写入主存,使Cache和主存保持一致。

| 优点 | 缺点 |

|---|---|

| 能随时保持主存数据的正确性 | 有可能增加多次不必要的向主存写入 |

- 写回策略(Write Back)

只把数据写入Cache而不写入主存,当Cache数据被替换出去时才写回主存。用Dirty标志位来识别Cache中的数据是否与主存一致:

| 状态 | 意义 |

|---|---|

| 清 | 表示未修改过,和主存一致 |

| 浊 | 表示修改过,和主存不一致 |

| 优点 | 缺点 |

|---|---|

| 写操作速度快 | 主存中的字块未经随时修改而可能失效 |

三种映射方式

- 全相联(Fully-associated)

- 直接相联(direct mapped)

- 组相联(set-associated)

全相联

全相联映射允许主存中的每一个字块映射到Cache的任意行,也允许从被占满的Cache中替换除任何一个旧字块,全相联映射一般应用在小容量Cache。

| 映射方式 |

|--|--|

|主存分块,Cache分行,两者大小相同 |

|主存地址分为:块号(从1开始) + 块内地址 |

访问Cache时,需要和Cache的全部标记进行比较,判断出所访问主存地址的内容是否已在Cache中。

|特点|

|--|--|

| Cache利用率高 | |

| 块冲突率低 | |

| 淘汰算法复杂 |

直接相联映射

|映射方式 |

|:-|--|

| 主存分块,Cache分行,两者大小相同 | |

| 主存分块后以Cache行数k为标准进行分区,一个区有k块。 | |

|主存地址分为:区号(从1开始) + 区内块基址(从0开始) + 块内地址(从0开始)

主存的数据块映射到Cache特定行,直接相联映射一般应用在大容量Cache。

i = j mod n

其中:

i为cache的行号

j为主存的块号

n为cache的行数

| cache行 | 被分配的主存块 |

|---|---|

| 0 | 0,n,2n,... |

| 1 | 1,m+1,2m+1,... |

| ... | ... |

|特点|

|--|--|

| Cache利用率低 | |

| 块冲突率高 | |

| 淘汰算法简单 |

例题

假定主存和Cache之间采用直接联映射方式,设主存容量为512KB,Cache容量为4KB,每个字块为16个字,每个字32位。

- Cache地址有多少位?能容纳多少块?

- 求直接映射方式下主存地址的各段的位数。

- 在直接映射方式下,主存的第几块映射到Cache中的第5块(设起始字块为第1块)?

解:

-

Cache的容量 = 4KB = 212,Cache地址有12位;

块的大小 = 16 × 4B = 26B;

容纳量 = 212 / 26 = 64块。 -

主存的容量 = 512KB = 219B,主存地址有19位;

Cache有64行,主存分成64个区,区号为6位;

一个区的大小为 = 512KB / 64 = 213B,块数 = 213B / 26B = 27,区内块号为7位;

块的大小 = 64B,块内地址为6位。 -

由i = j mod n得5 = j mod 64,解得j = 5,64 + 5,2 × 64 + 5,…,213 - 64 + 5

组相联映射

组相联映射是全相联映射和直接映射的折中方案

|映射方式 |

|:-|--|

|主存分块,Cache分行,两者大小相同 | |

|Cache分组(每组包含k行) | |

| 主存分块后以Cache组数n为标准进行分组,主存一组有n块。 | |

|主存地址分为:组号(从1开始) + 组内块号(从1开始) + 块内地址(从0开始)

m = v * k

i = j mod v

其中:

m = cache行数

v = 组数

k = 每组的行数

i = cache的组号

j = 主存块号

例题

设某机内存容量为16MB,Cache的容量16KB,每块8个字,每个字32位。设计一个四路组联映射(即Cache内每组包含4个字块)的Cache组织方式。求满足组相联映射的主存地址字段中各字段的位数。

解:

主存容量16MB = 224,主存地址位数24位;

块大小 = 8 × 4B = 32B,块内偏移地址5位;

Cache行数 = 16KB / 32B = 512行;

Cache组数 = 512 / 4 = 128组;

主存一组128块,组内块号有7位;

主存分为4096组,组号是有12位。

替换算法

当Cache被占满时,又有新数据需要调入Cache,需要通过某种机制决定被替换的对象。

常见替换算法

- 先进先出 FIFO(First In First Out)

- 最近经常不使用 LFU(Least Frequently Used)

设置使用频率计数器,当需要替换数据时,将使用频率最低的替换掉,若有多个频率相同低的数据时,则根据FIFO或随机替换法选择一个。 - 近期最少使用法 LRU(Least Recently Used)

设置使用次数计数器,当需要替换数据时,将使用次数最少的替换掉,若有多个使用次数相同少的数据时,则根据FIFO或随机替换法选择一个。 - 随机替换

Cache的改进

-

两级缓存

L1级缓存和CPU制作在同一个芯片内,能够提高外部总线的利用率,L2缓存设置在主存和CPU之间,不使用系统总线,使用一个独立的数据路径以减轻系统总线的负担,从而提高L2缓存调入L1缓存的速度,而CPU占用系统总线的时间大大下降,提升整机性能。 -

统一缓存和分立缓存

统一缓存是指指令和数据都存放在同一缓存,分立缓存是指令和数据分别存放在两个缓存,分为指令Cache和数据Cache。统一和分立的选择要考虑主存结构和机器对指令执行的控制方式。

浙公网安备 33010602011771号

浙公网安备 33010602011771号