DPARAM

双端口RAM

Dual Port Access RAM

存储器不断接受CPU访问,还要频繁地和I/O设备通信。如果只有一套MAR,ID,MDR和读写电路。任一时刻只能接受一方的访存请求。同时访问两个主存单元时,CPU和I/O经常有访存的矛盾。

逻辑结构

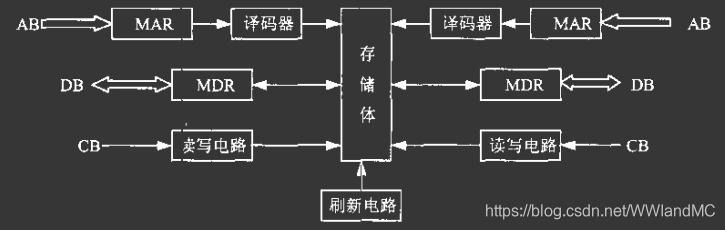

同一个存储器具有两组独立的读写控制线,两个端口分别具有各自的地址线,数据线和控制线,可进行独立的存取操作。

DPARAM的结构

有两个访存端口,两套MAR,两套ID,两套MDR,两套读写电路,分别连接两套独立的BUS

访存冲突

无冲突访存:两个端口地址不同

有冲突访存:两个端口地址相同

设置BUSY标志位,采用仲裁逻辑,由判断逻辑决定哪个端口优先访存,暂时关闭另一个被延迟的端口。被延迟到端口等待时间很短,小于一个存取周期,同样可以达到提高存取速度的效果

浙公网安备 33010602011771号

浙公网安备 33010602011771号