存储系统——主存模型

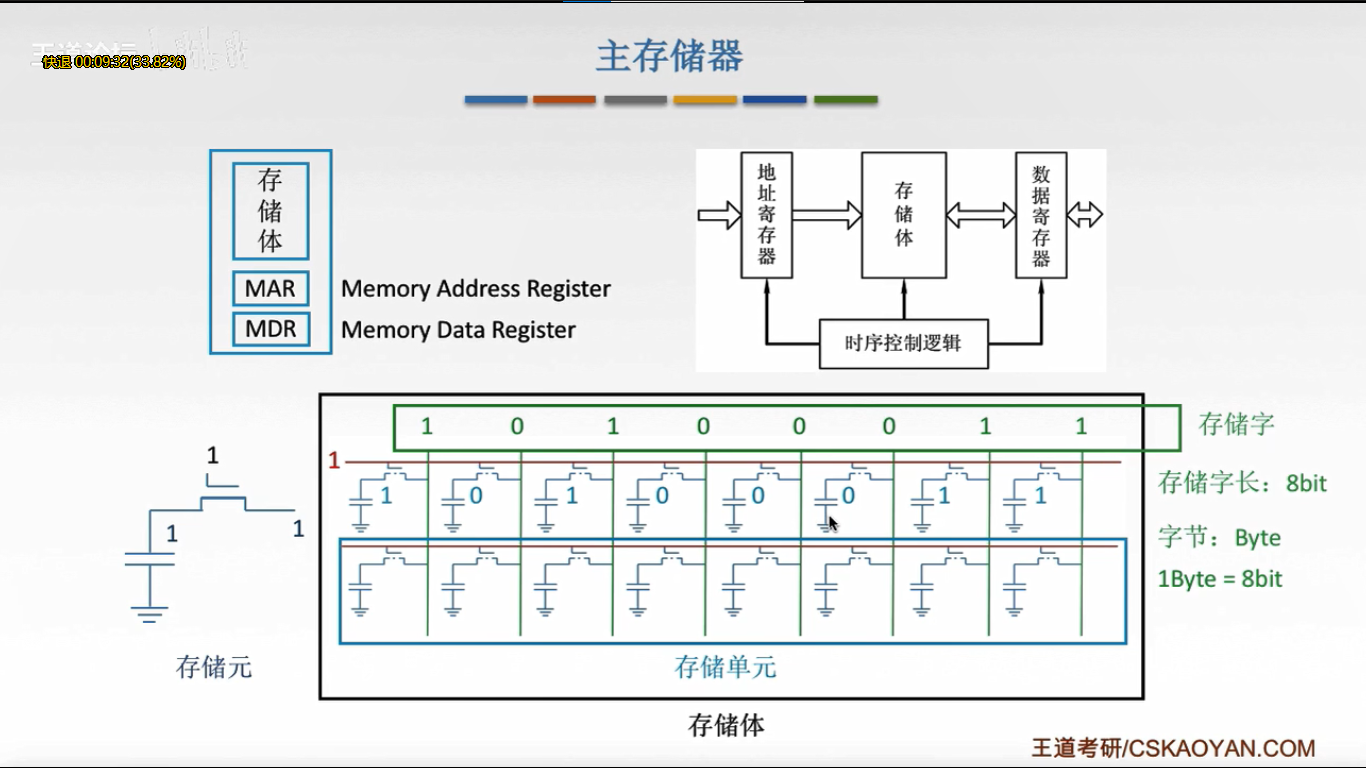

主存由存储体,地址寄存器MAR,数据寄存器MDR组成

时序控制逻辑负责协调存储体,地址寄存器,数据寄存器之间的工作

例如:读数据:通过地址寄存器里的地址找到存储体中数据,再将数据放到数据寄存器中;写数据:将数据寄存器中的数据按地址寄存器中的地址存入存储体中

多个存储元构成一个存储单元,多个存储单元构成一个存储体

位:(bit)是电子计算机中最小的数据单位。每一位的状态只能是0或1。1B=8b

字节:8个二进制位构成1个"字节(Byte)",它是存储空间的基本计量单位。1个字节可以储存1个英文字母或者半个汉字

字:字是计算机进行数据处理和运算的单位。字通常由多个字节(8位)组成。

字长:一个字的位数。现代计算机的字长通常为16位(2个字节)、32位(4个字节)、64位(8个字节)。

存储单元:以8位二进制作为一个存储单元,也就是一个字节。

存储字:存储字是指存放在一个存储单元中的二进制代码组合。一个存储字可代表一个二进制数,也可代表一串字符。

存储字长:存储字的位数,也就是存储字的长度。

存储单元的工作原理:读信号1给到一个存储单元,沿横轴传到每个存储元,每个存储元按竖轴传出信号,构成存储字

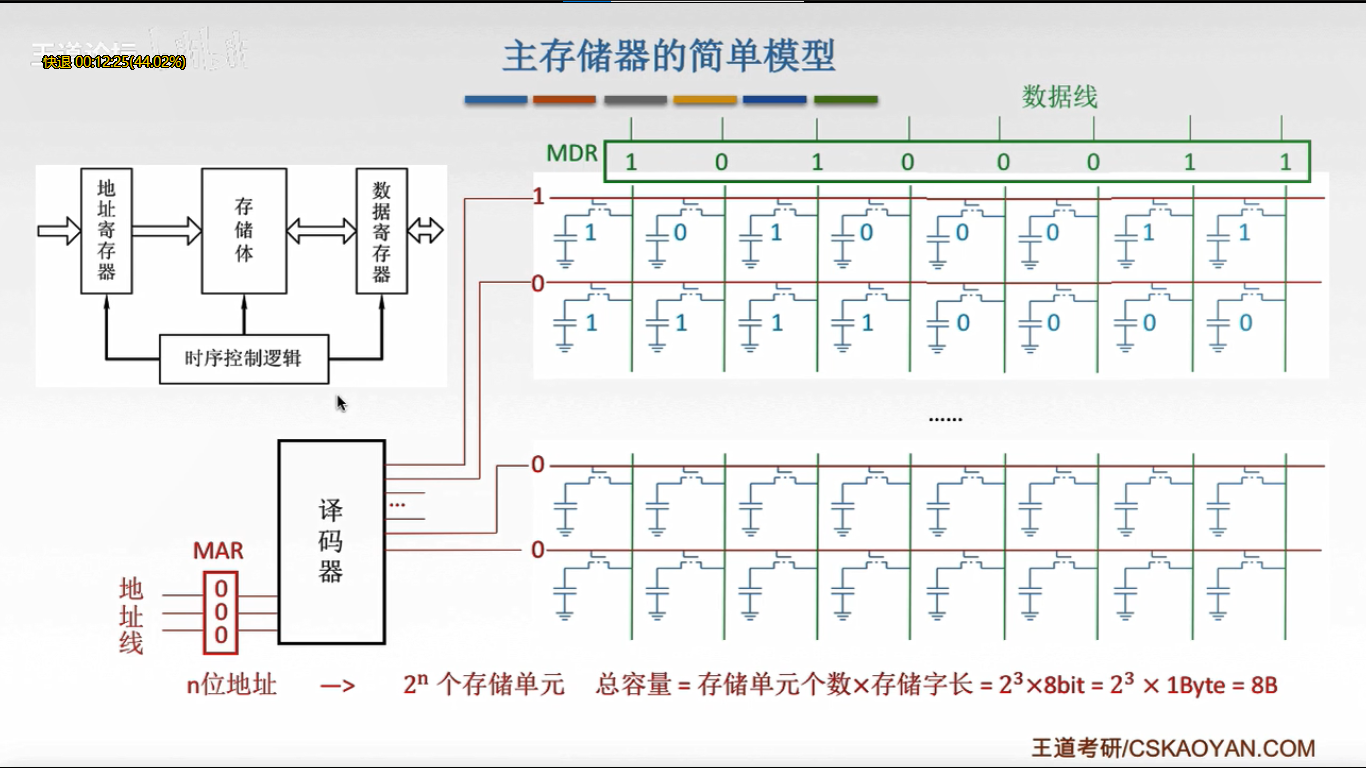

地址线连接地址寄存器MAR,数据线连接数据寄存器MDR

一块存储芯片中有许多存储单元,当给一个存储单元发送有效信号时,给其他的存储单元必须是无效信号。要想控制所有存储单元,每个存储单元都要有一条信号线,太多了。

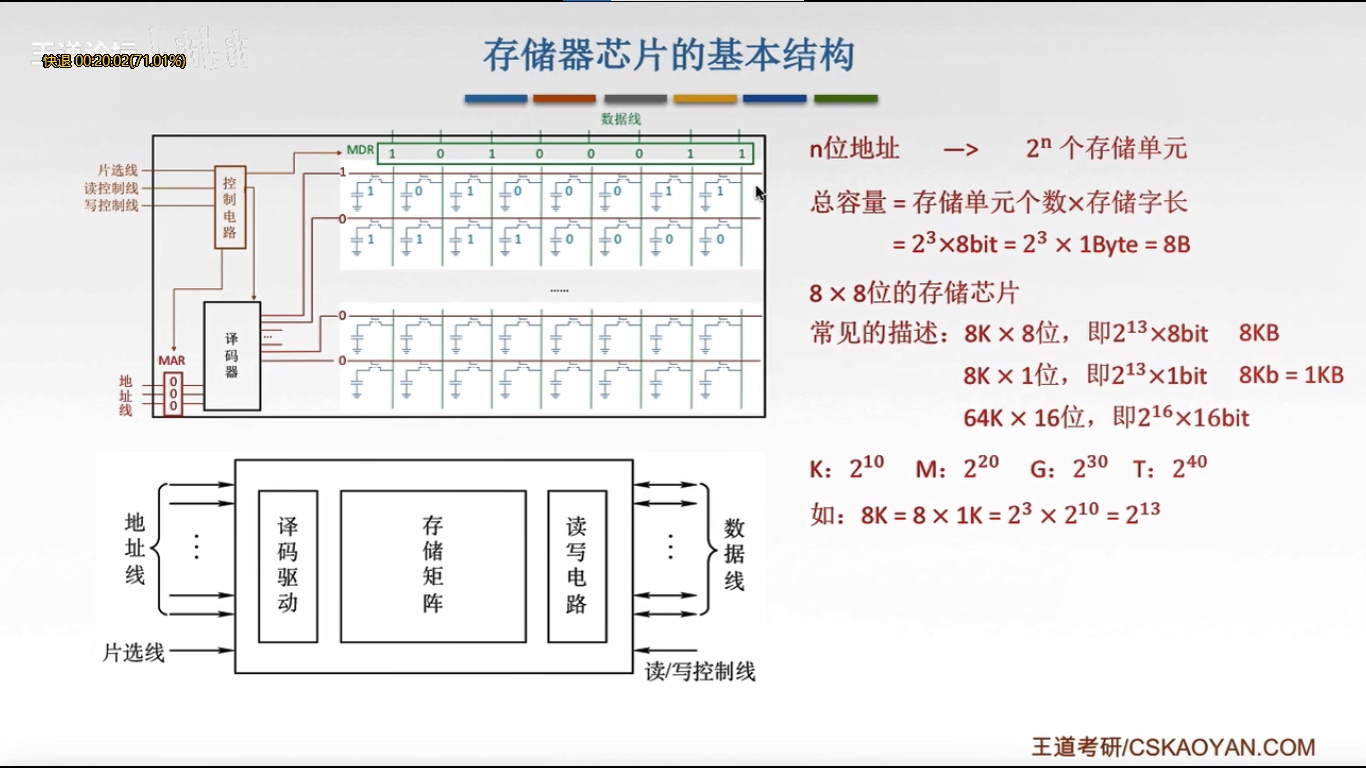

减少信号线的办法:译码器(使N条信号线控制2的N次方个存储单元);映射功能(将二进制信号映射为输出信号一个为1其余为0的形式)

存储芯片的总容量=存储单元(行)× 存储字长(列)

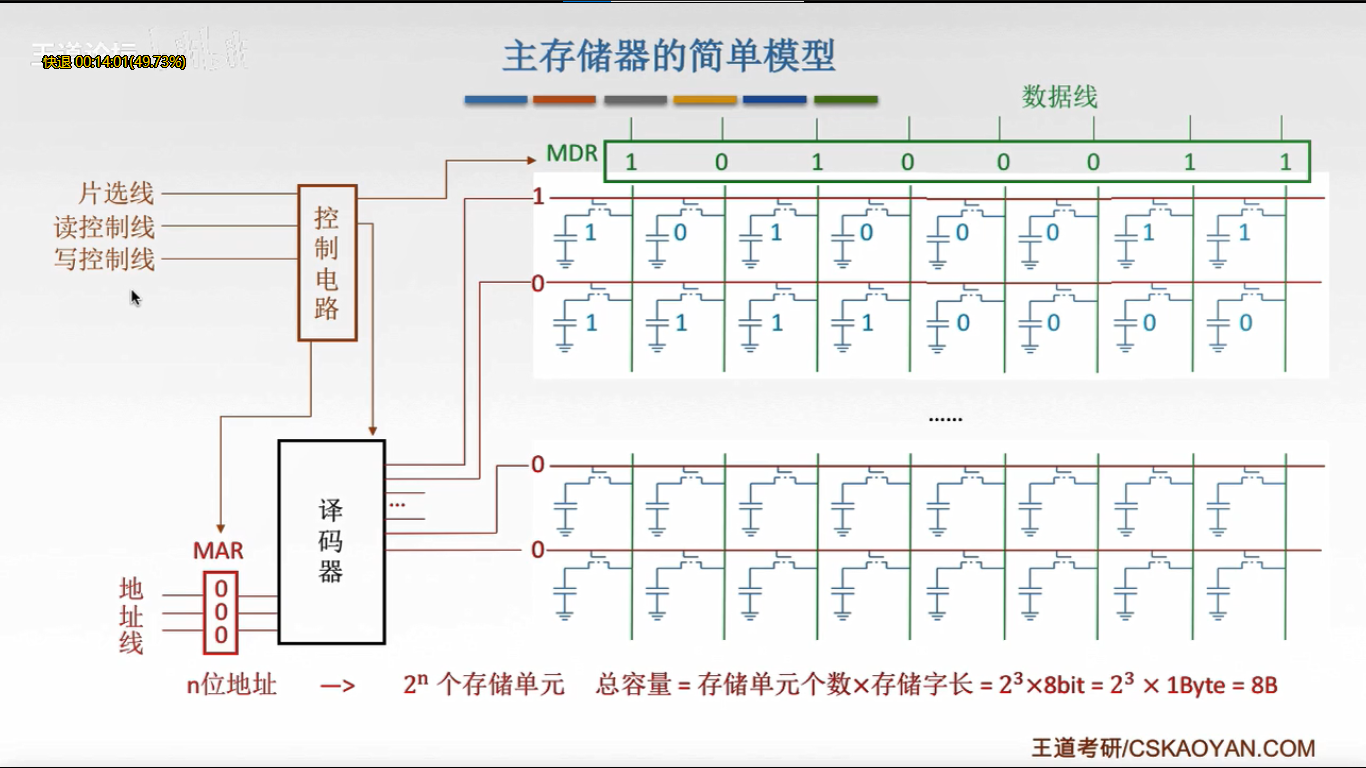

控制电路(时序控制逻辑)

片选线:控制电路的开关,分为高电平有效和低电平有效

读写控制线:决定信号是写是读?何时写何时读?

译码驱动:扩大输送信号能力的辅助电路

浙公网安备 33010602011771号

浙公网安备 33010602011771号