Verilog HDL门级建模

Verilog HDL内部定义了12个基本门级元件可以直接用,用这些门级原件直接对逻辑图进行描述,称为门级建模。

每个门输入可能是逻辑0,逻辑1,不确定态x和高阻态z四个值之一。

1.多输入门

主要有与门(and),与非门(nand),或门(or),或非门(nor),异或门(xor),同或门(xnor)。

符号都知道,为了省事我选择直接拍照。

相比于之前,就加了一个高阻态和不确定态,除了正常用法,其他输出的值都是x,多输入门不可能输出z。

在verilog中,一般引用格式为:

Gate_name <instance> (OutputA, Input1, Input2, ..., InputN);

输出在前,输入在后,instance是我们自己命名的实例引用名字,可以省略。

举例:

and U1(out, in1, in2);

xnor (out, in1, in2, in3, in4); //省略instance

2.多输出门

主要有缓冲器(buf),反相器(非门,not)。

还是输出在前,输入在后。图和真值表如下:

举例:

buf B1(out1, out2, ..., in);

not (out1, out2, ..., in) //省略instance

3.三态门

输出为低电平0,高电平1,高阻态z,所以叫三态门。verilog中有四个元件模型,分别是bufif1,bufif0,notif1,notif0。图、功能、真值表分别如下:

4.门级建模举例

一个2线-4线译码器,功能和真值表如下:

(1)verilog HDL门级代码Decoder2x4_gates.v

module Decoder2x4_gates(

input [1:0]A,

input En,

output [3:0]Y);

wire A1not, A0not; //声明电路内部节点

not (A0not, A[0]);

not (A1not, A[1]);

nand U0(Y[0], En, A0not, A1not),

U1(Y[1], En, A[0], A1not),

U2(Y[2], En, A0not, A[1]),

U3(Y[3], En, A[0], A[1]);

endmodule

(2)激励文件Test_Decoder2x4.v

`include "Decoder2x4_gates.v"

`timescale 1us/1us

module Test_Decoder2x4;

reg En;

reg [1:0] A;

wire [3:0] Y;

Decoder2x4_gates U0(A, En, Y);

initial begin

En = 1'b0; A = 2'b10;

#4 En = 1'b1;

end

always begin

#2 A = A + 1'b1;

end

initial begin

//变化一次monitor执行一次

$monitor($time, ":A[2]A[1]A[0]=%b%b%b\ten=%b\tY[2][1][0]=%b%b%b\t\ttest=%d", A[2], A[1], A[0], En, Y[2], Y[1], Y[0], 4'sd9);

$dumpfile("Decoder2x4.vcd");

$dumpvars;

#15 $finish;

end

endmodule

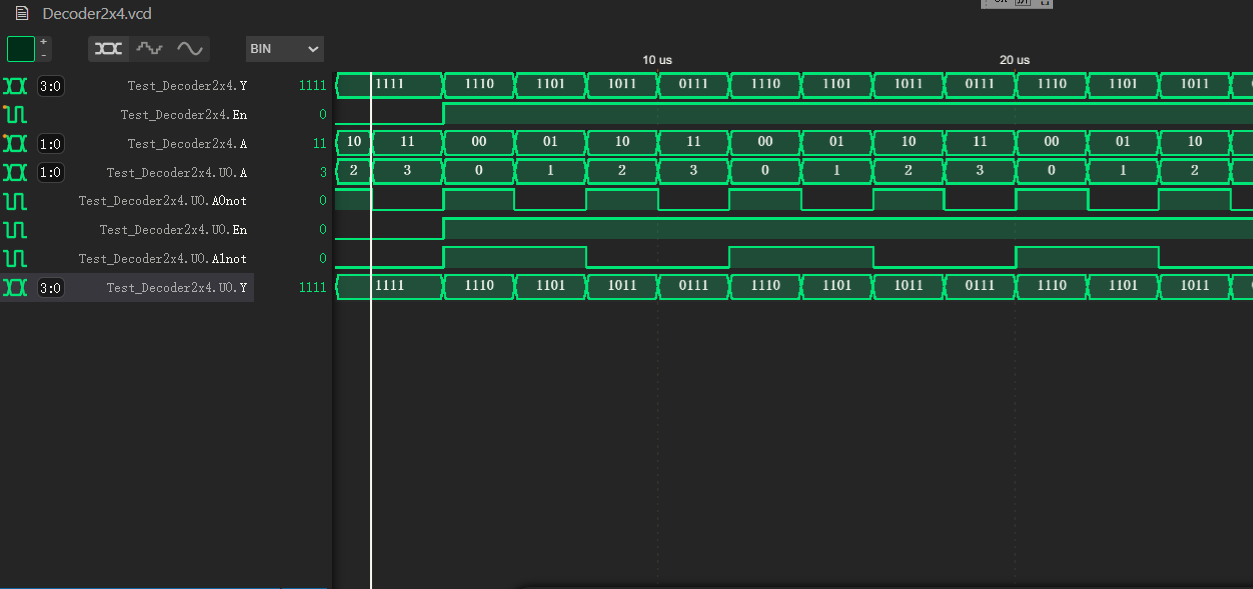

(3)我用$dumpfile生成了Decode2x4.vcd文件,直接使用vscode的WaveTrace插件打开即可,嘎嘎好用啊。

浙公网安备 33010602011771号

浙公网安备 33010602011771号