vivado(测试一)PS端通过串口输出helloword

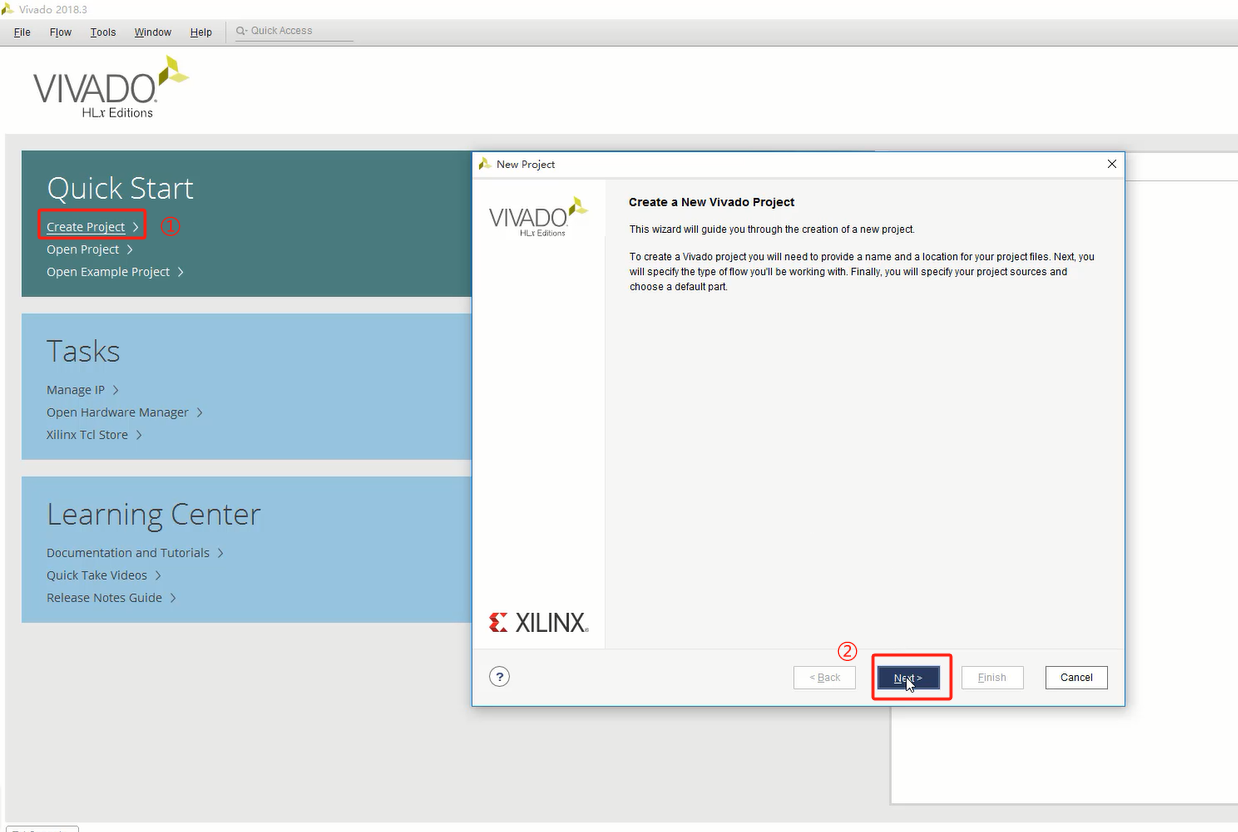

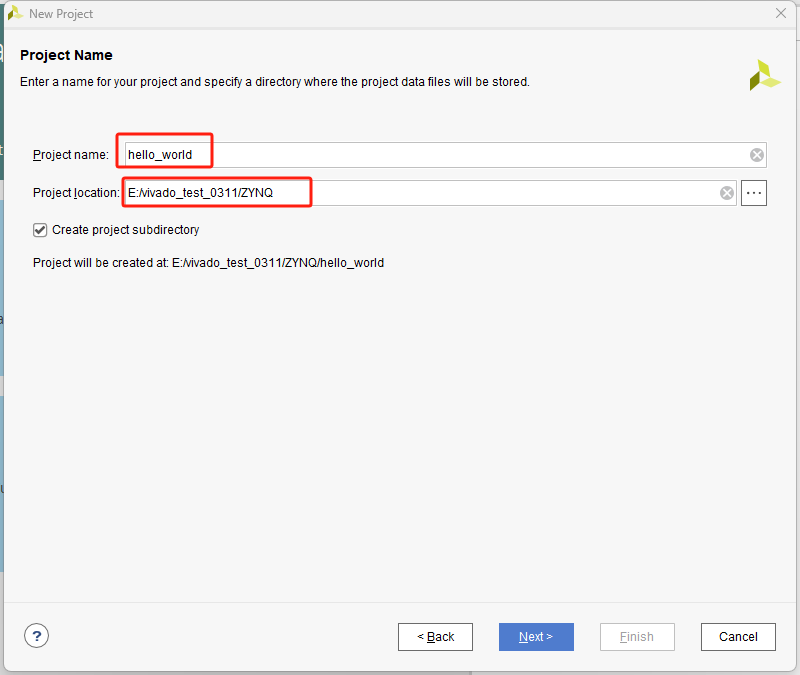

创建工程:

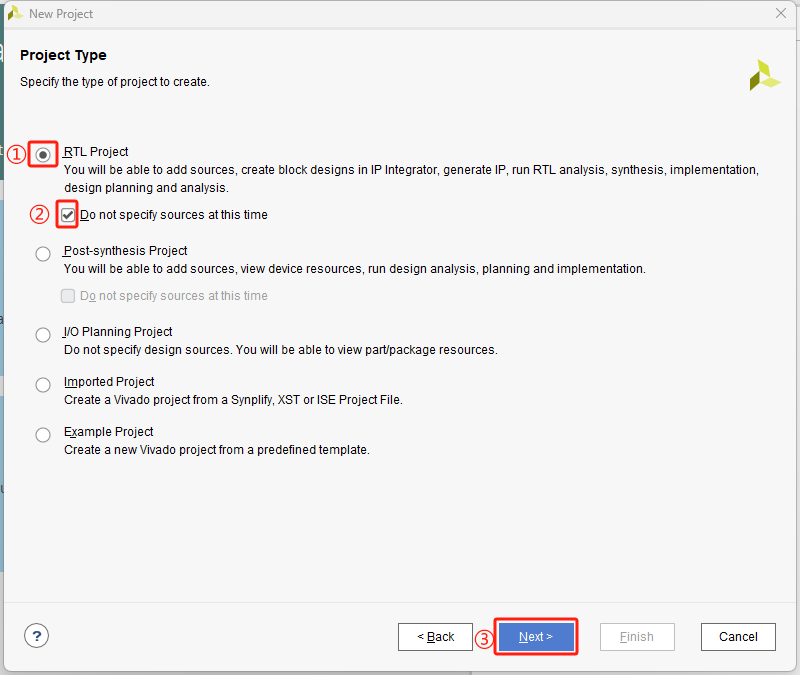

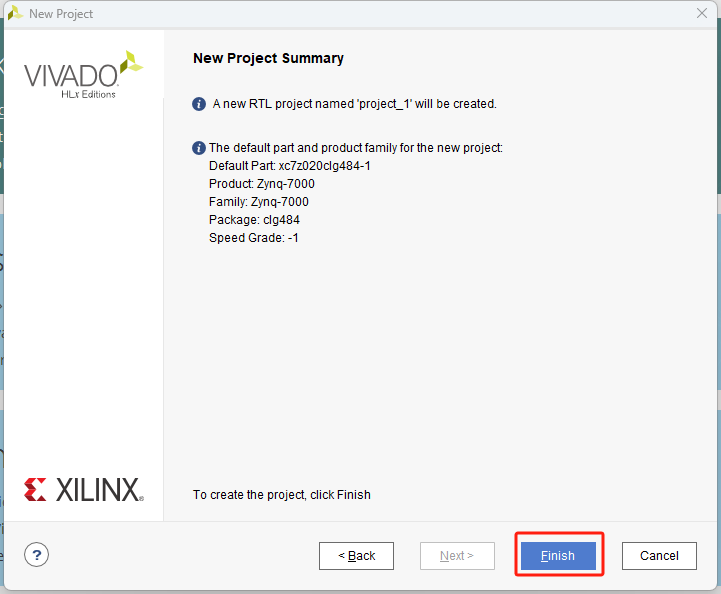

创建一个RTL工程:

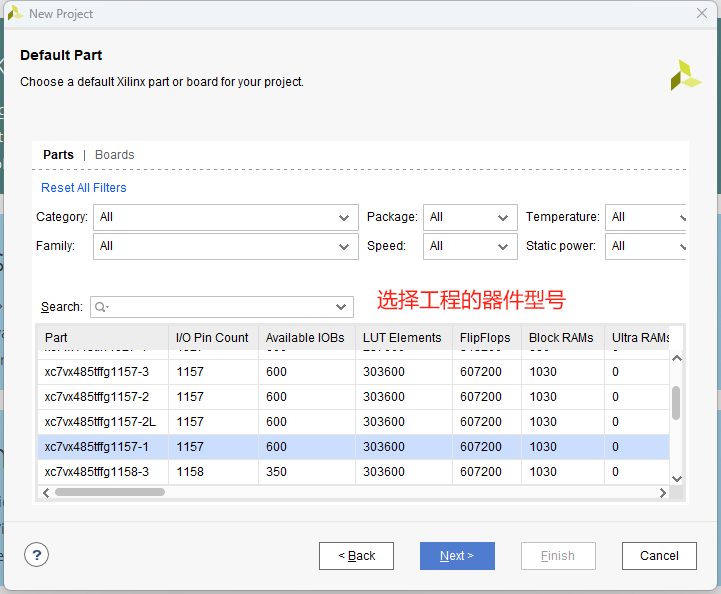

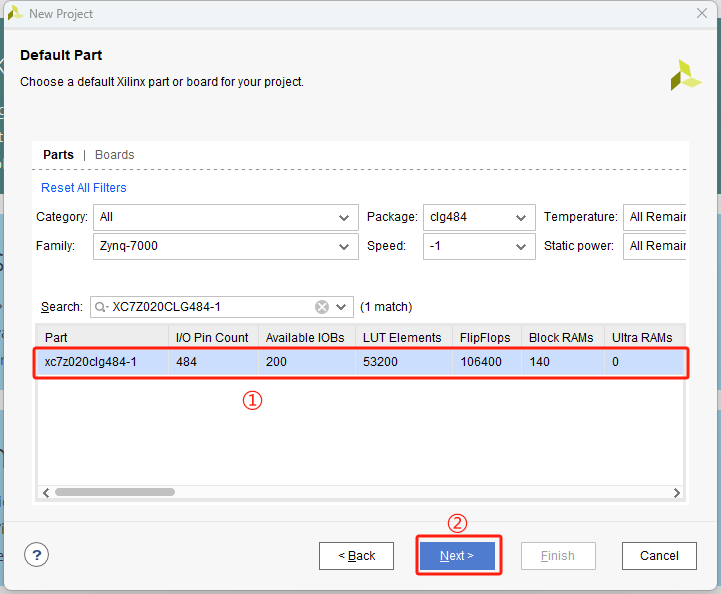

选择器件:

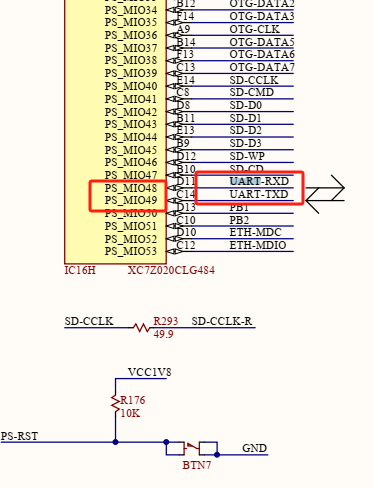

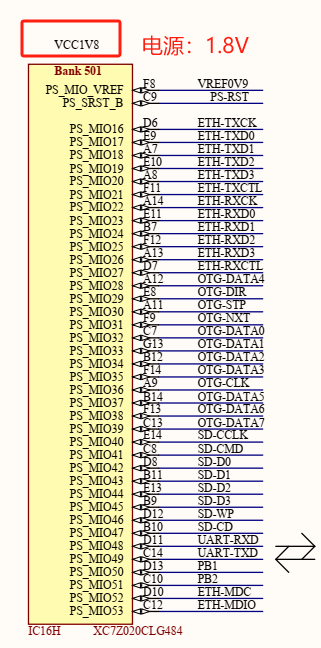

而我用的zedboard的SOC型号:XC7Z020CLG484-1

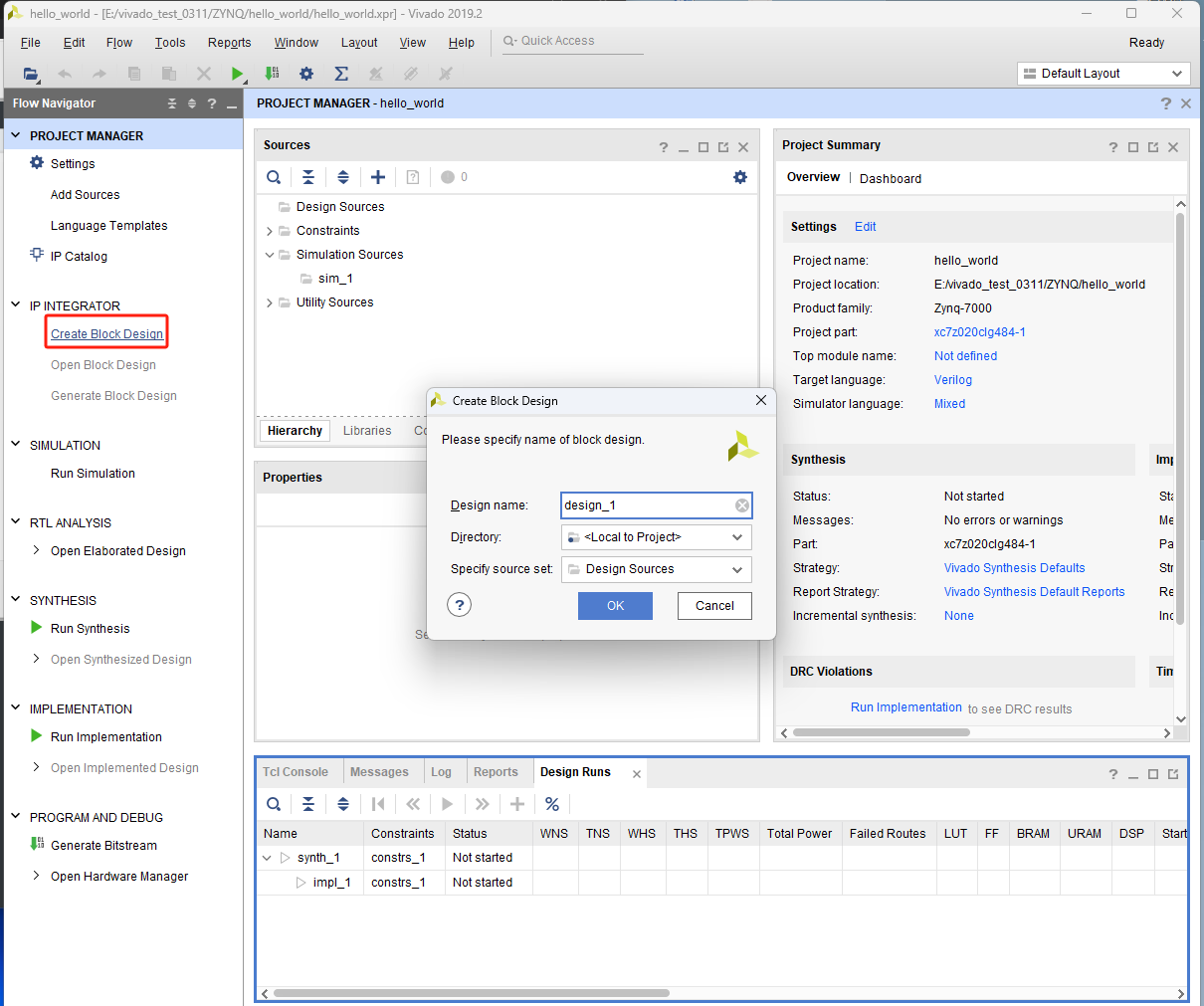

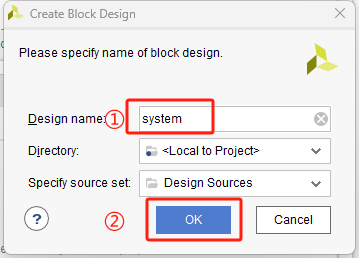

创建PS工程:

第1步:对设计进行命名:

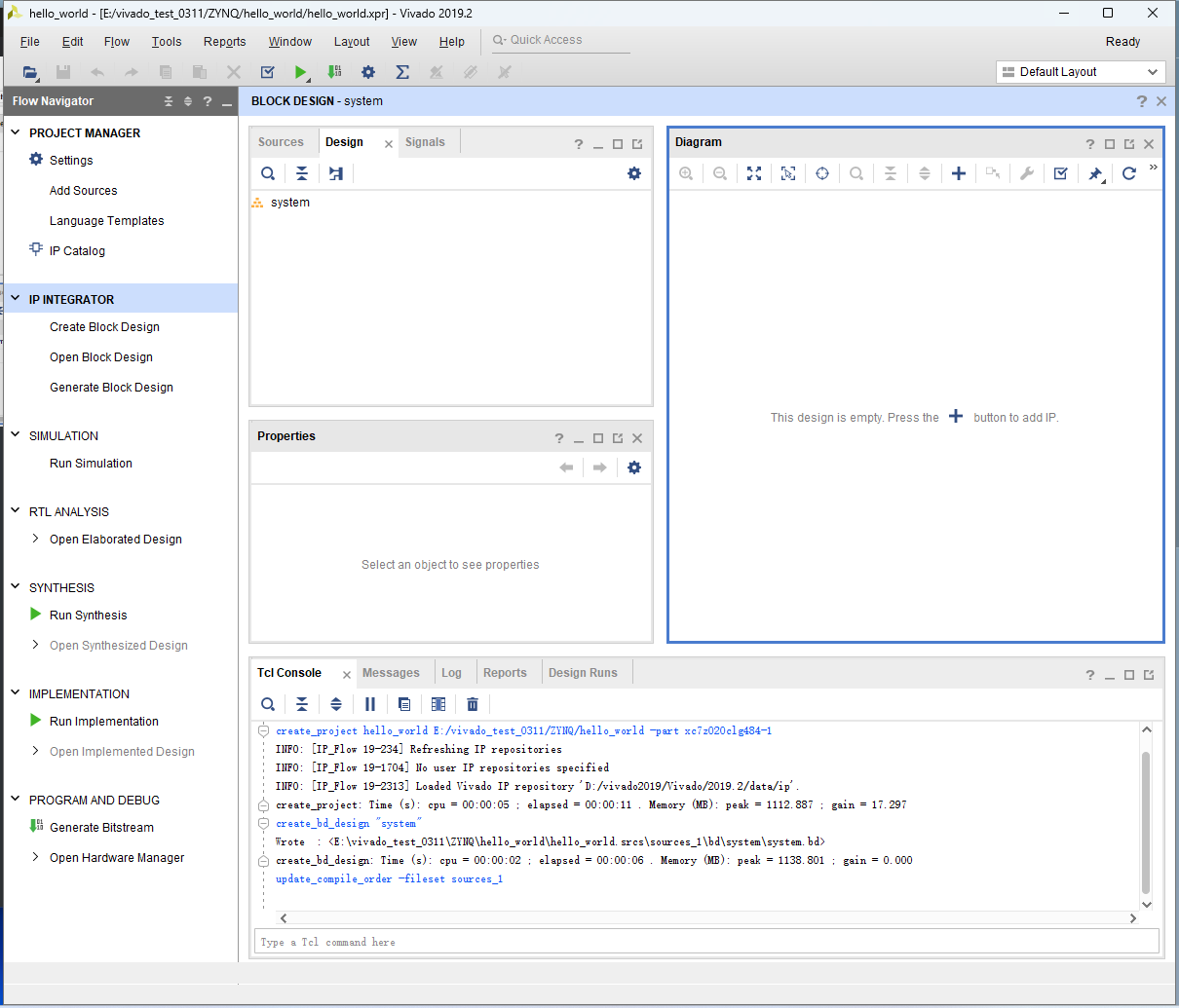

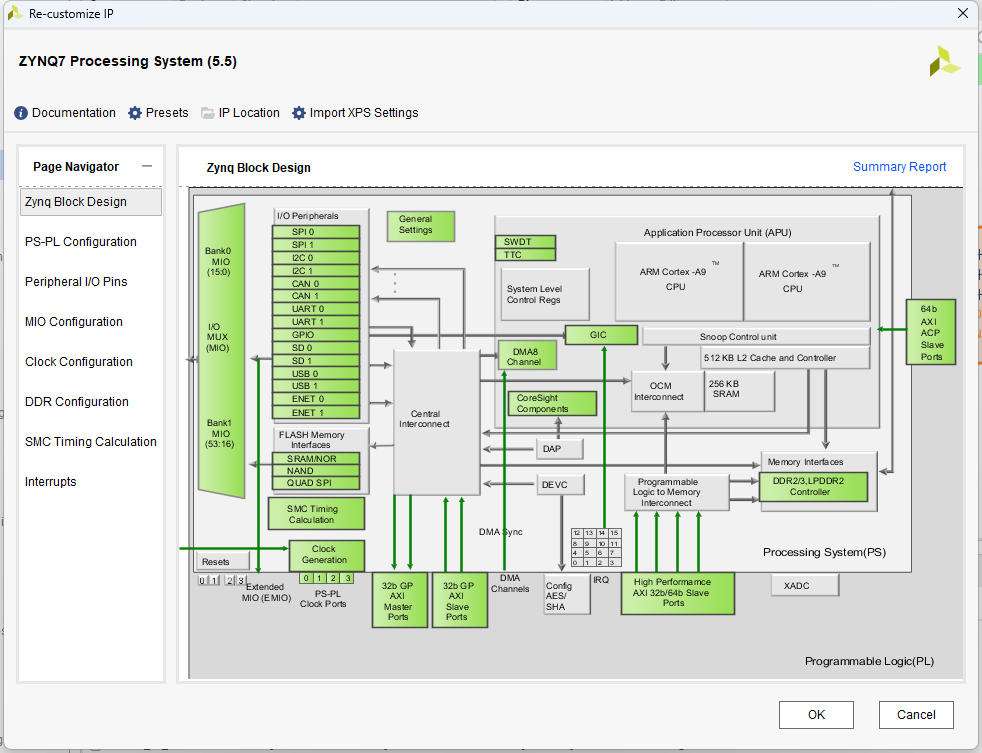

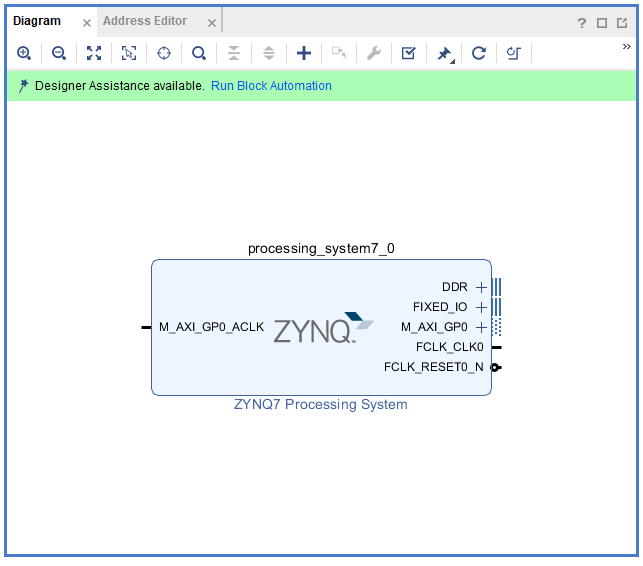

等待一会后出现如下的界面:

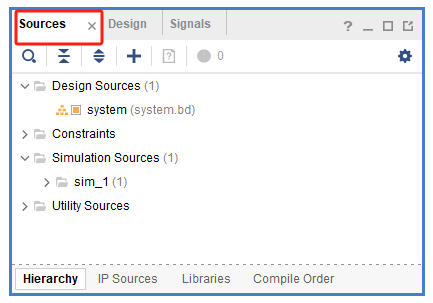

第2步:选择sources

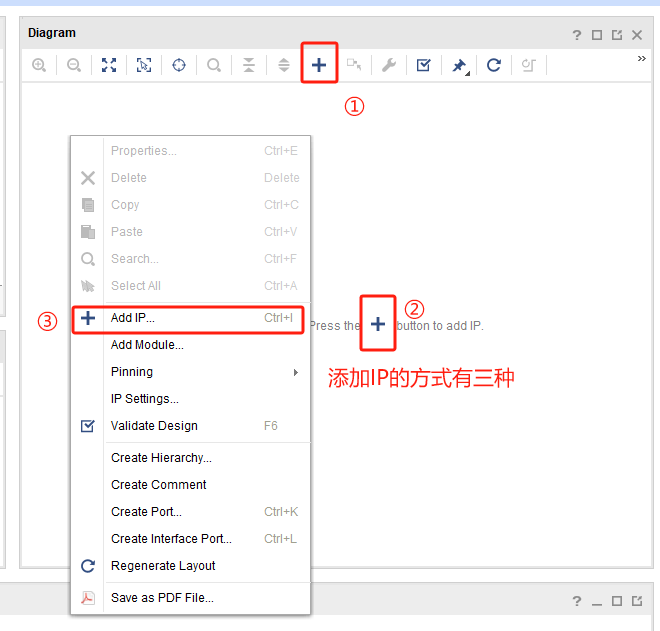

第3步:添加IP:

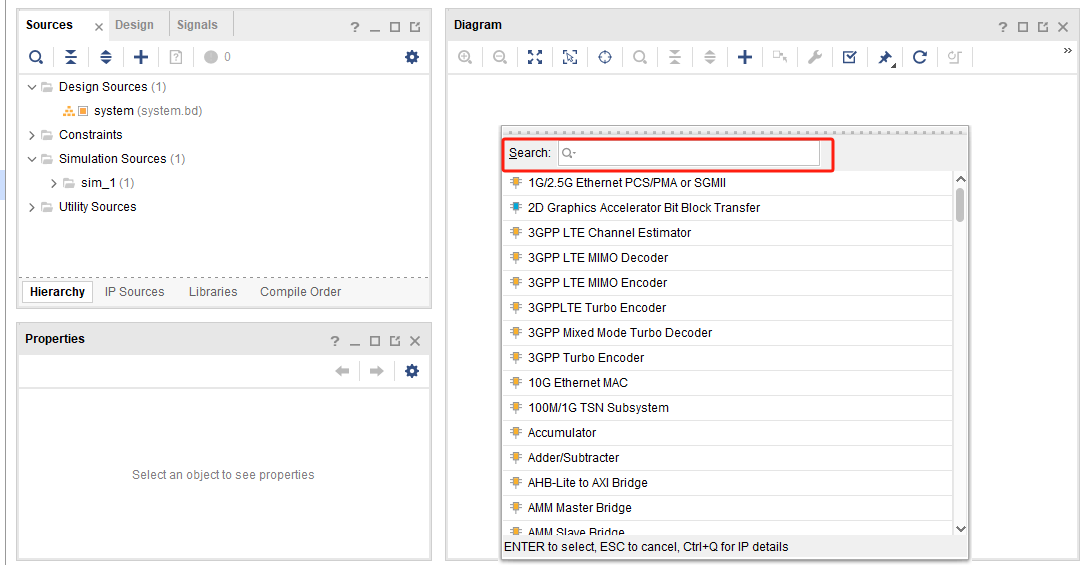

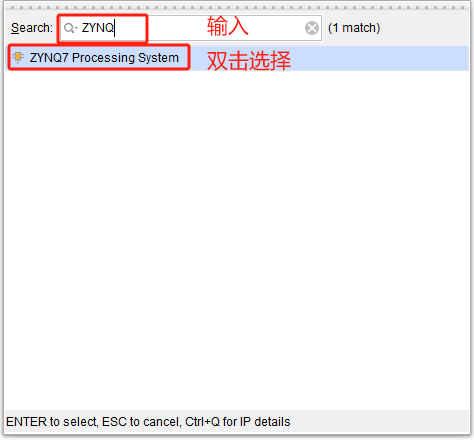

第4步:搜索ZYNQ的PS部分的IP核:

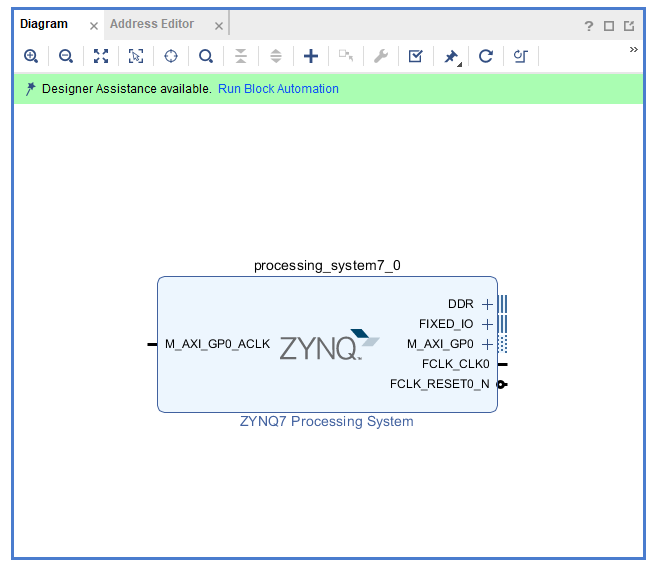

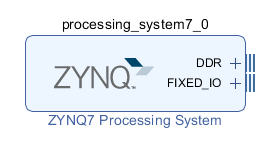

等待一段时间后

此界面的放缩方法:

①Ctrl+鼠标滚轮

②左键按住从左上角框选到右下角

③左键按住 朝着 左上、右上、左下 分别对应一种界面放缩模式。

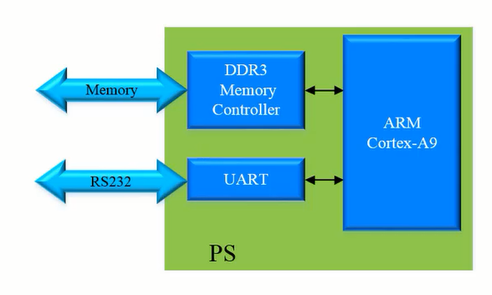

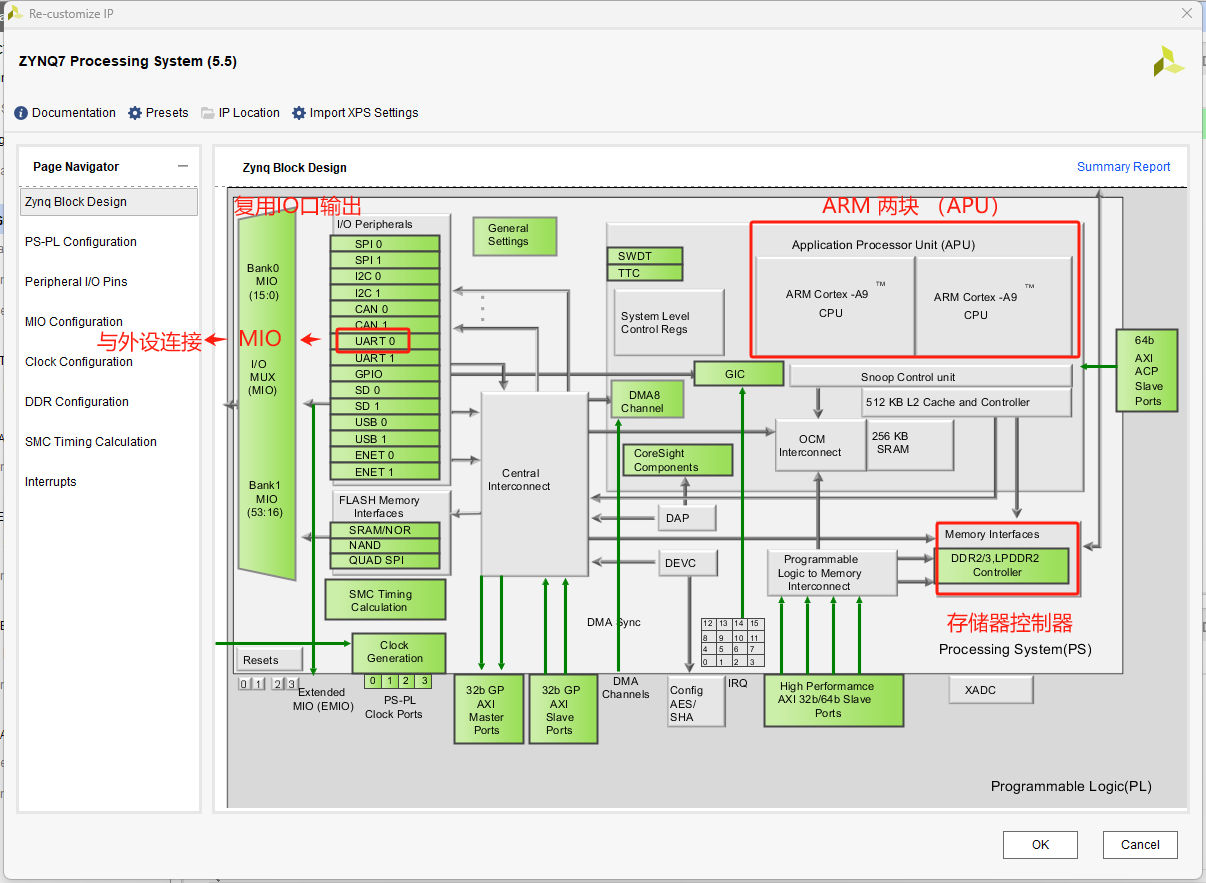

ZYNQ的嵌入式最小系统:

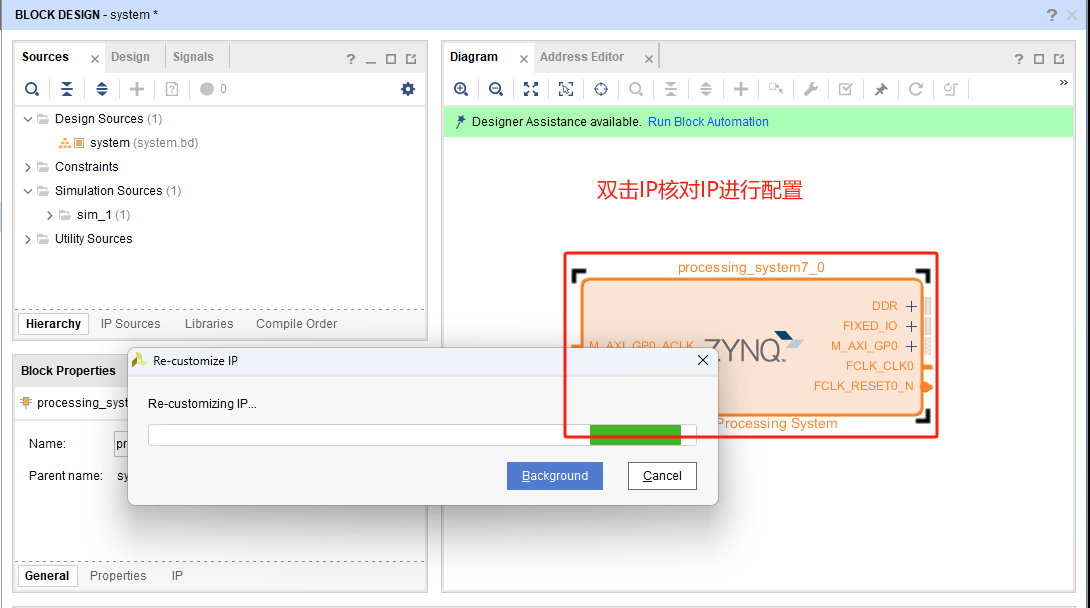

双击PS模块,进入PS模块的配置界面。

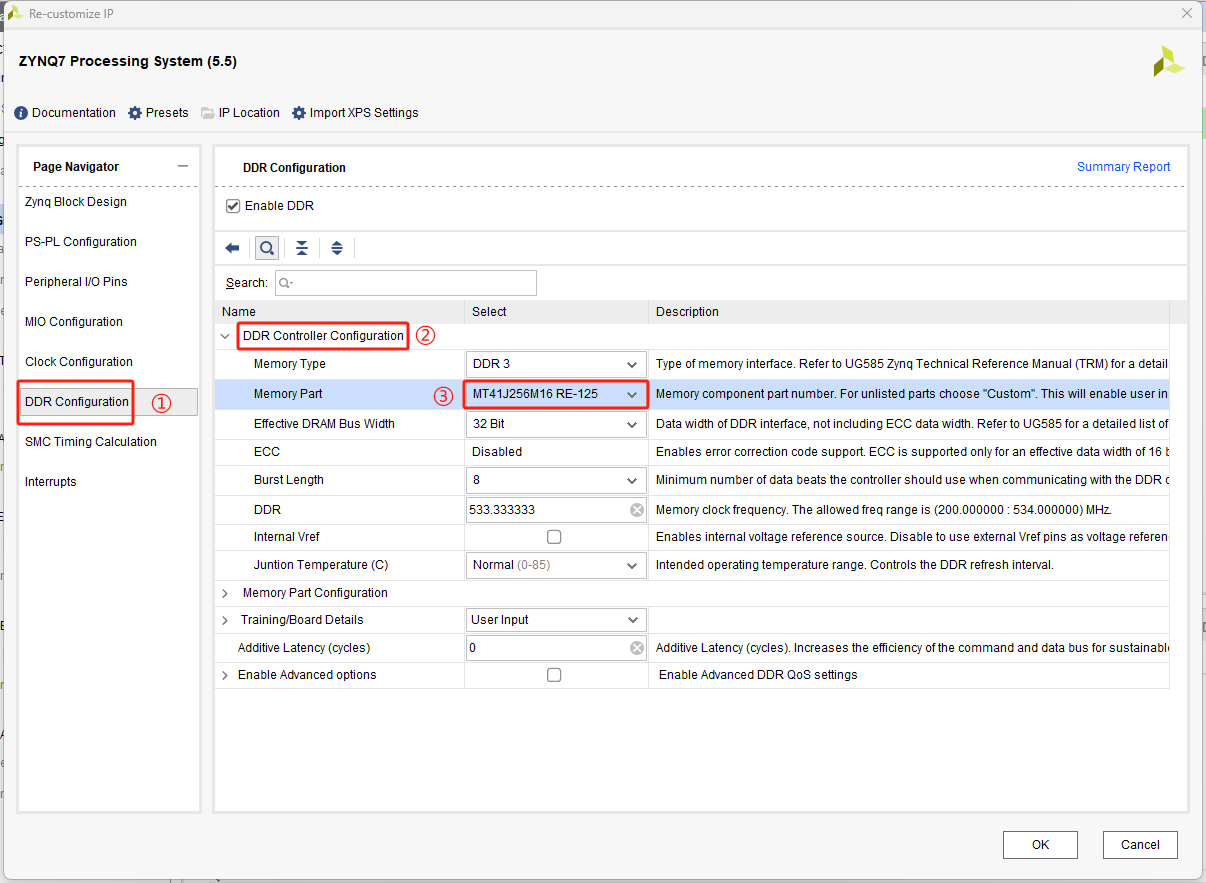

第5步:DDR configuration设置:

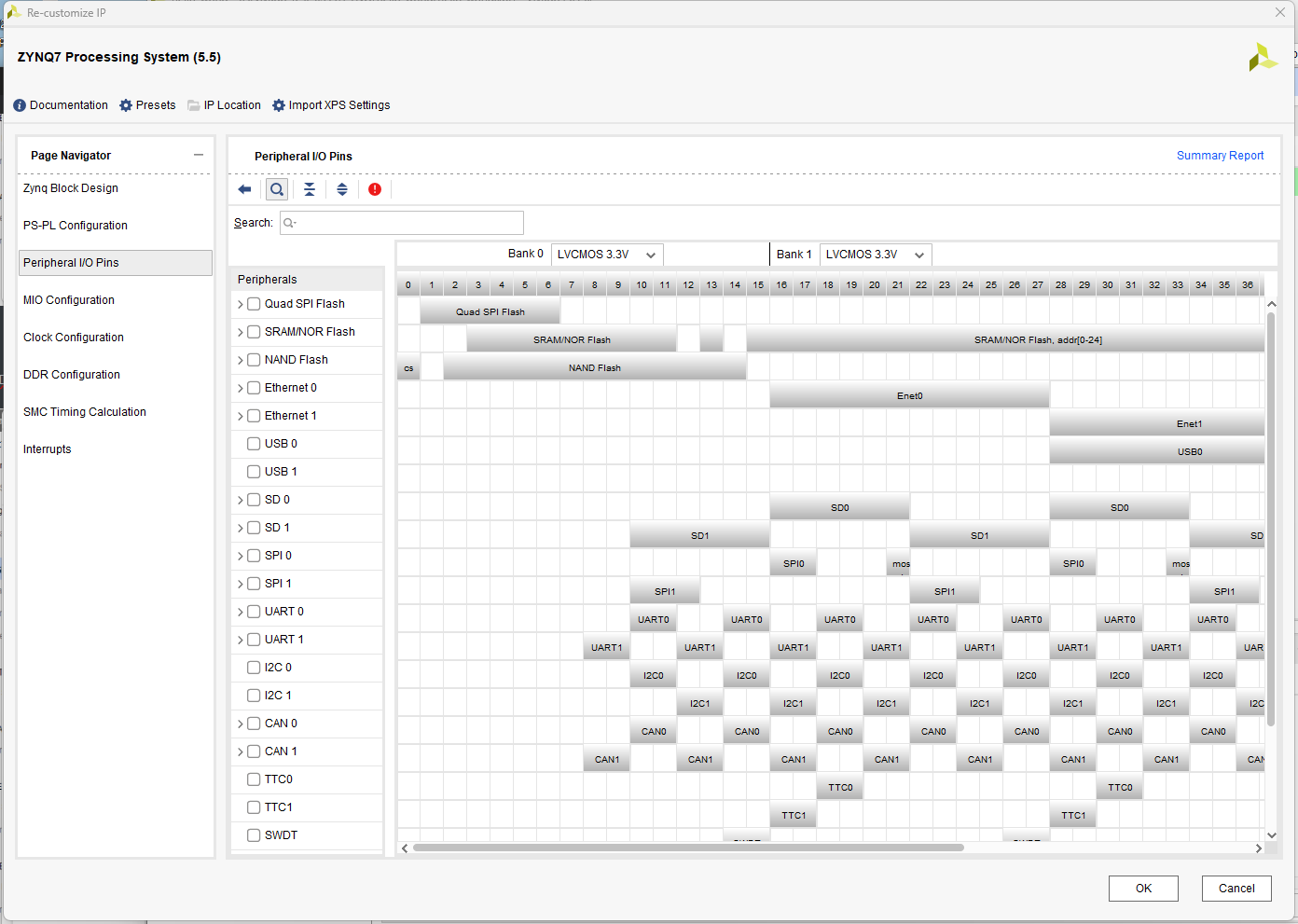

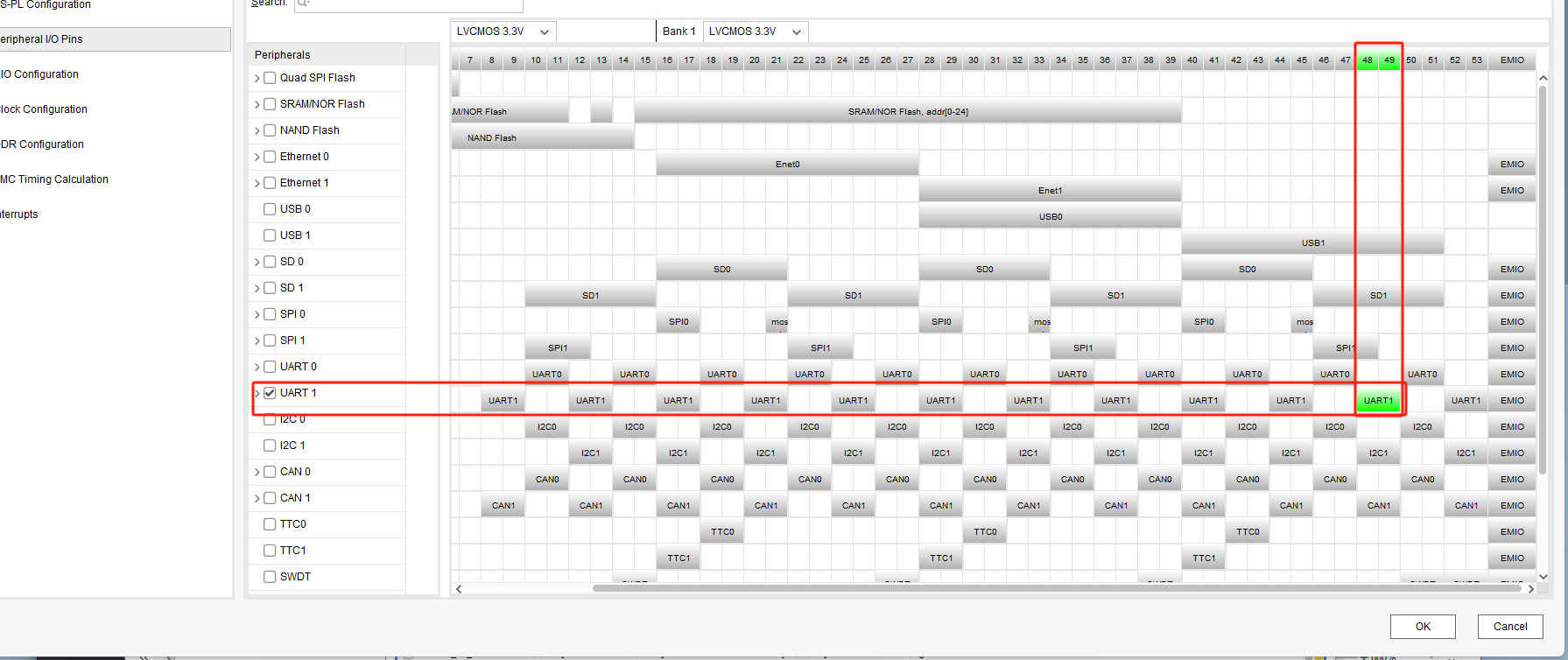

第6步:Peripheral I/O Pins 设置:

在zedboard的原理图上面搜索:UART

检索到的结果为 对应着 PS_MIO48, PS_MIO49

先找到MIO 然后找MIO48,MIO49

选择UART行对应的有MIO列的选项。

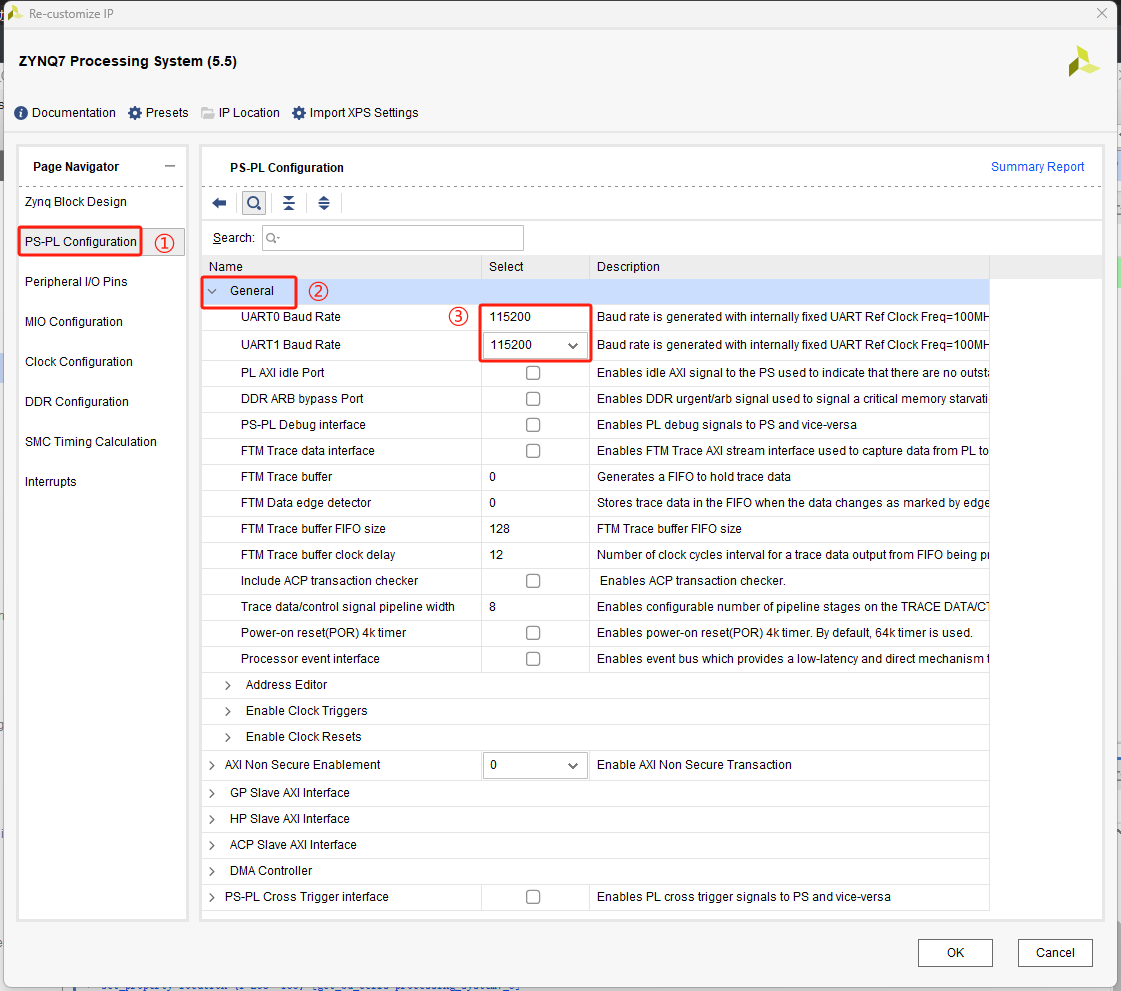

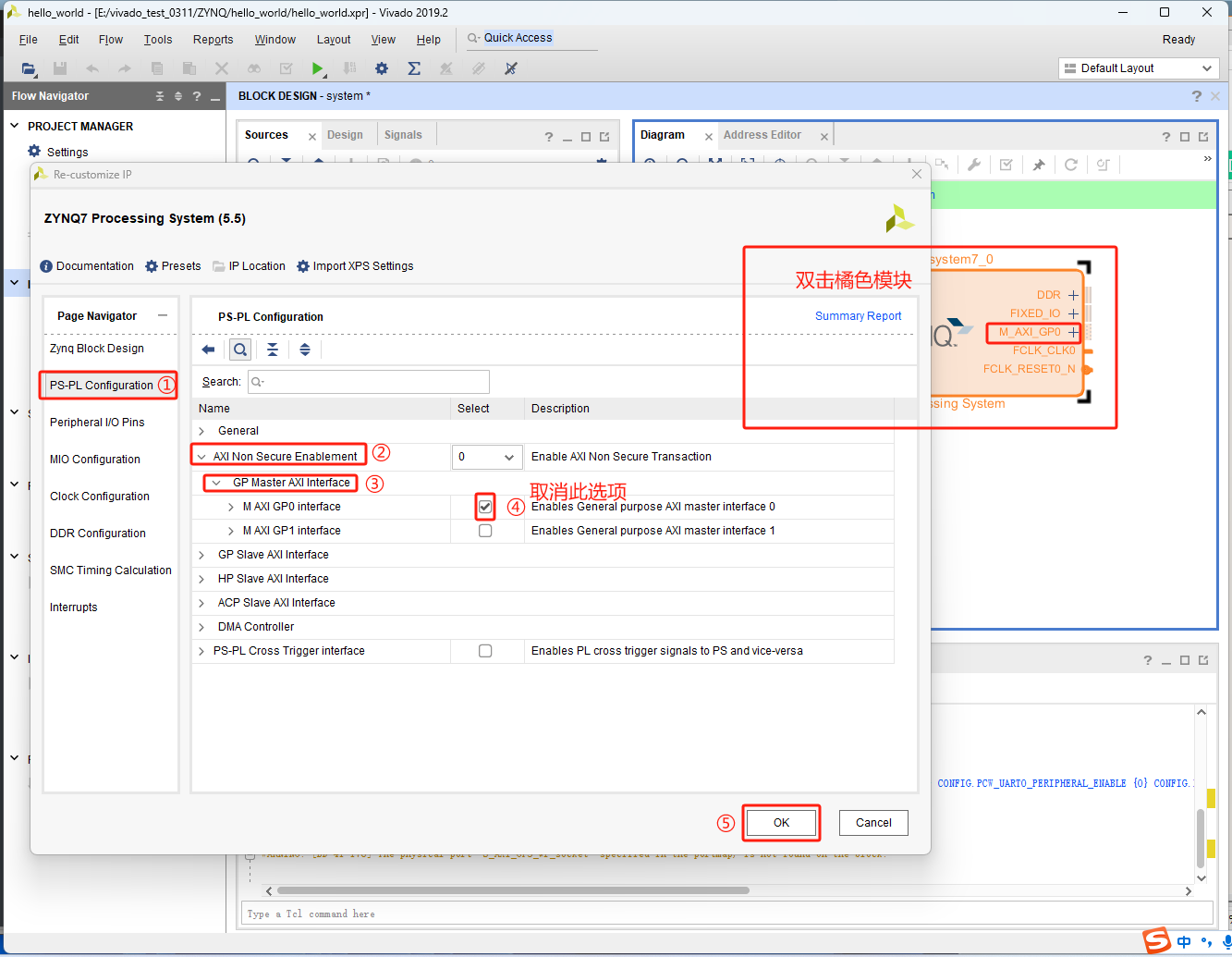

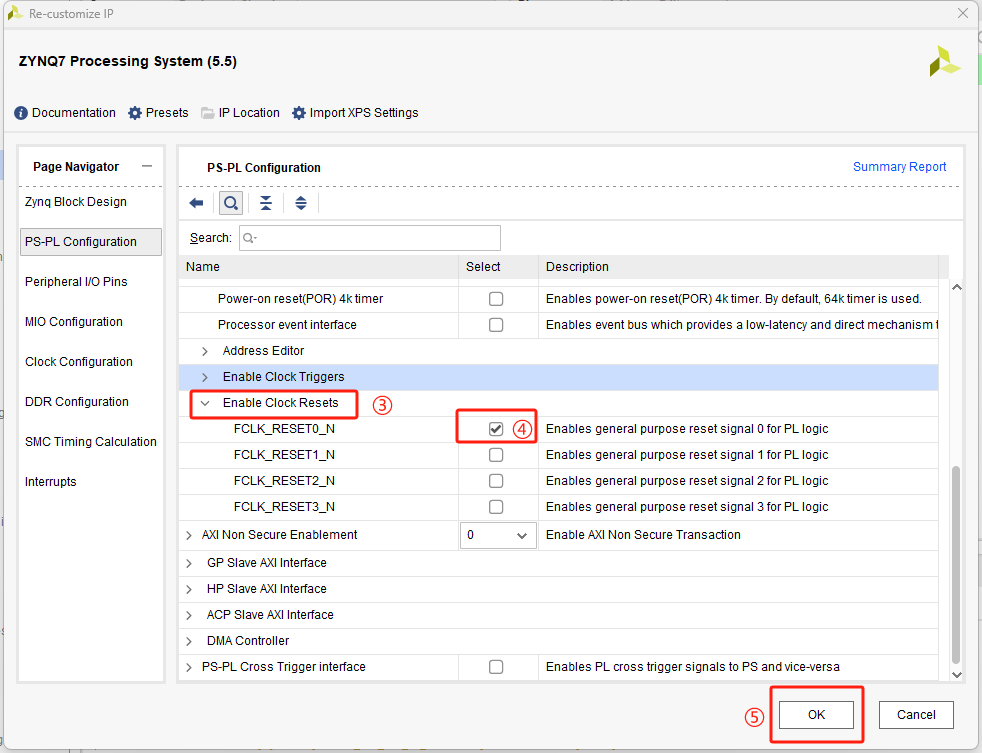

第7步:PS-PL configuration

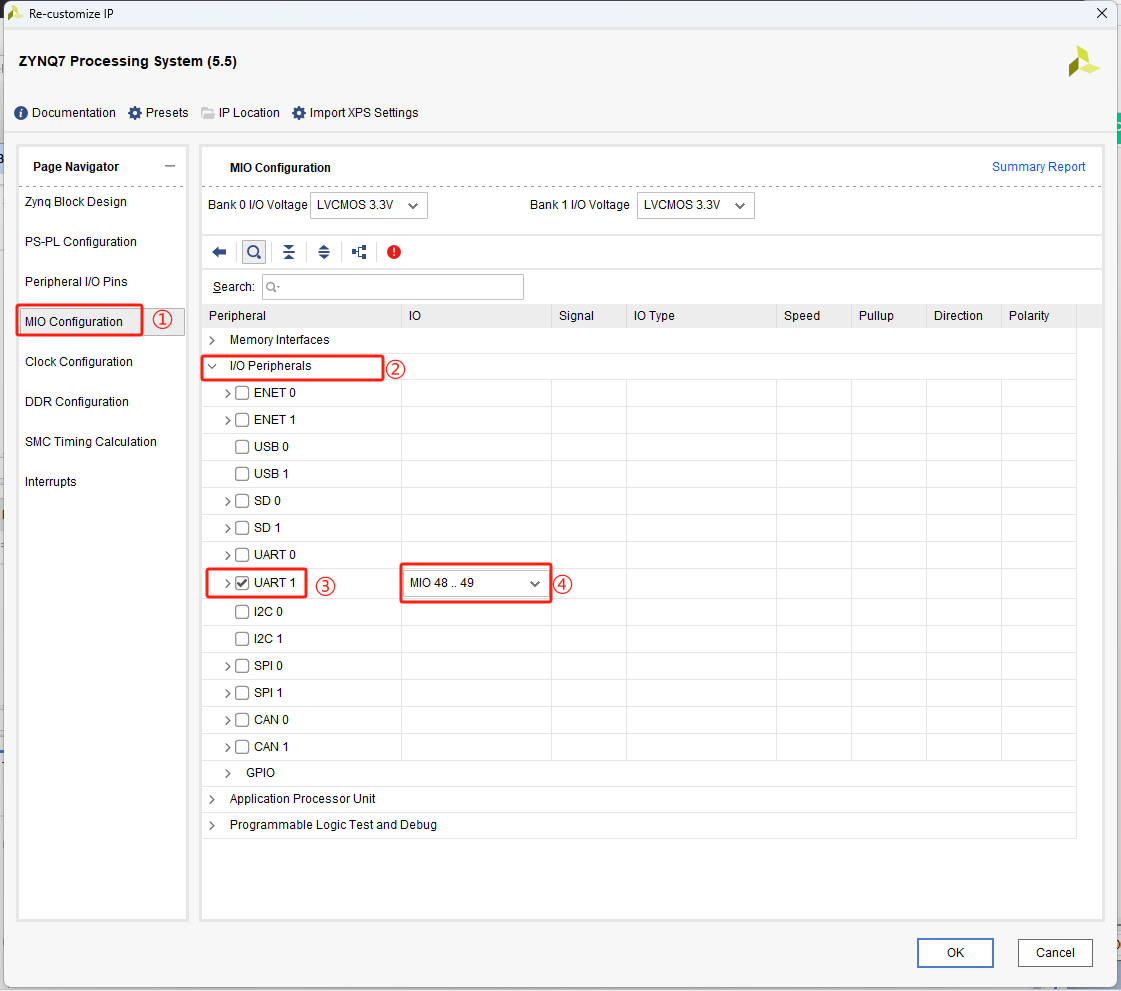

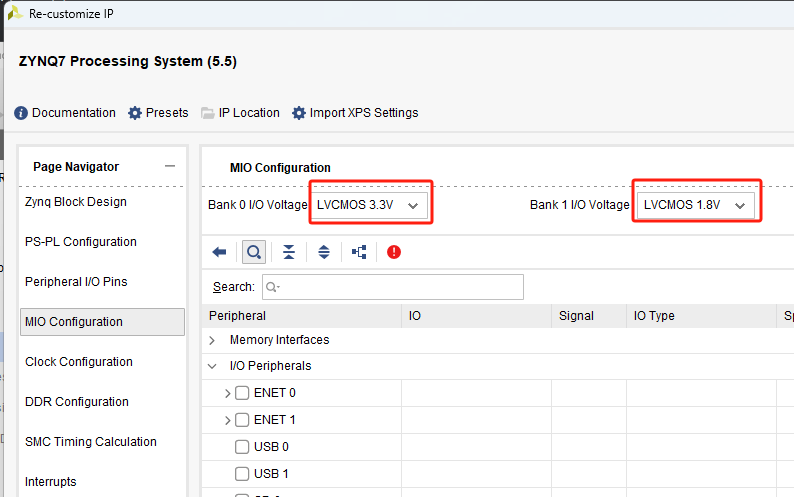

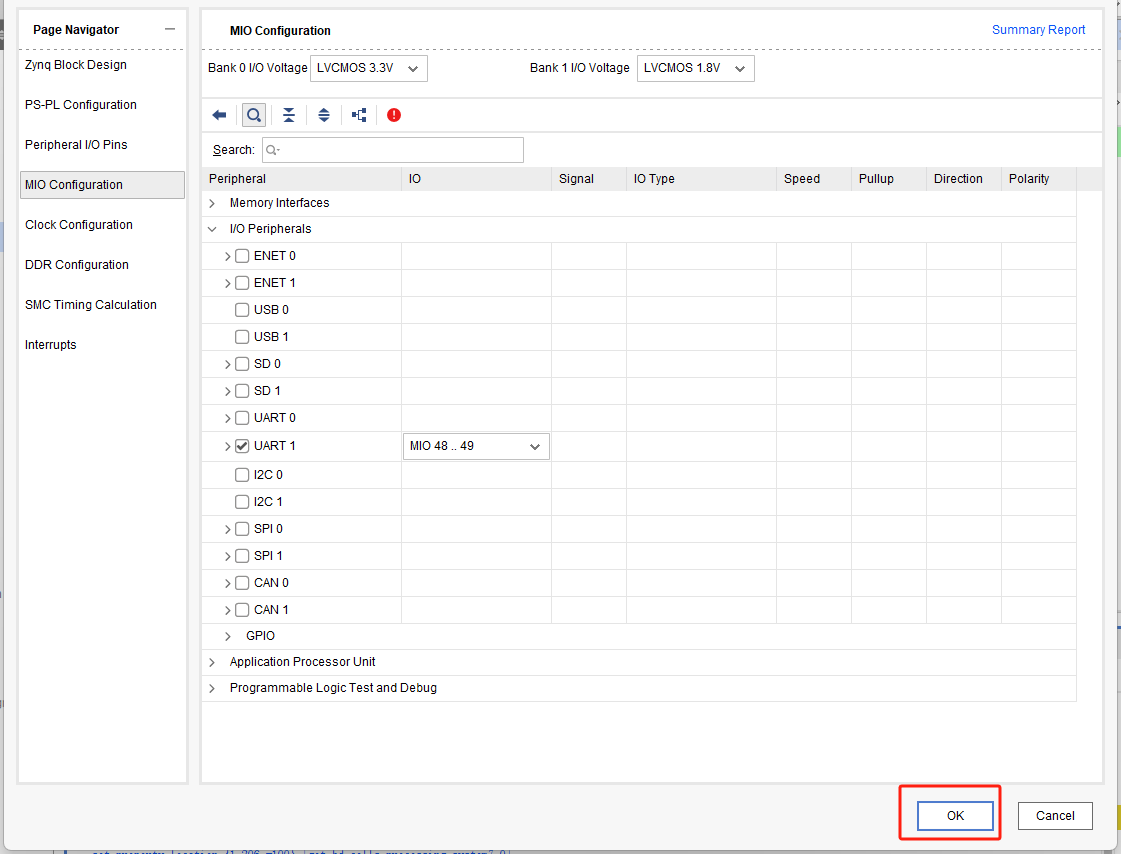

第8步:MIO configuration 复检之前的MIO选项

第9步:原理图上确认电压

因为bank501为1.8V

对照着原理图仔细检查各部分的供电系统。

完成上述操作后,点击OK.

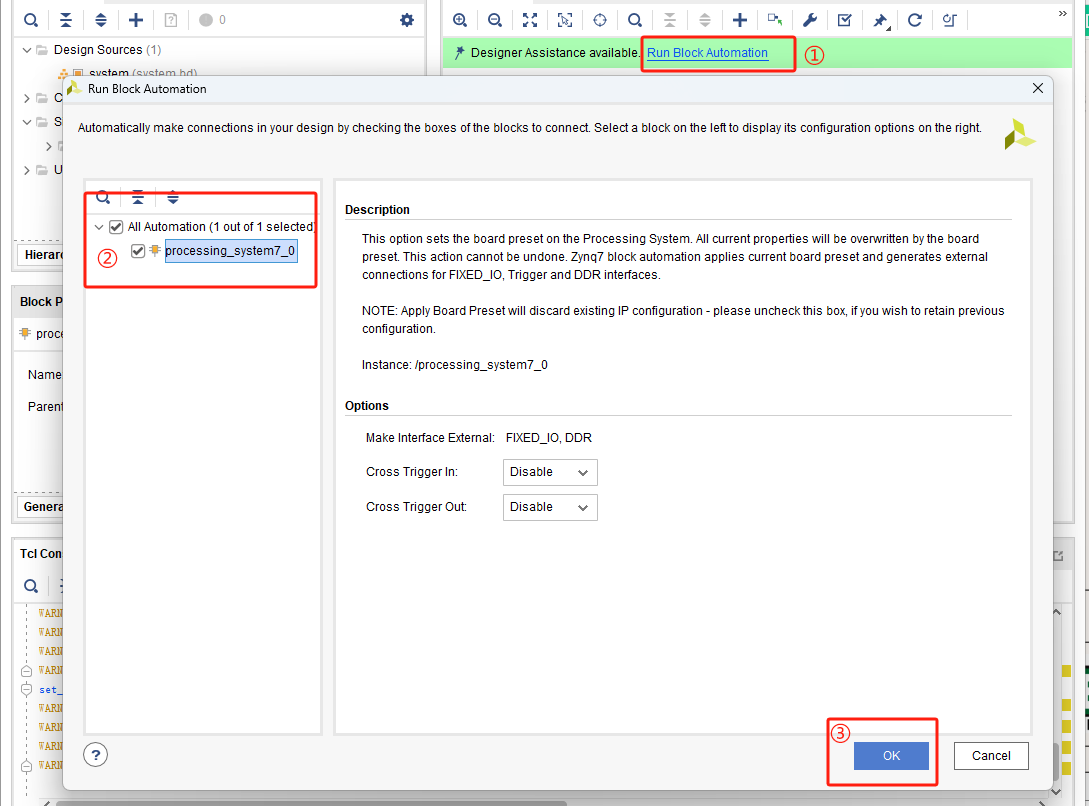

第10步:对PS模块进行设置:

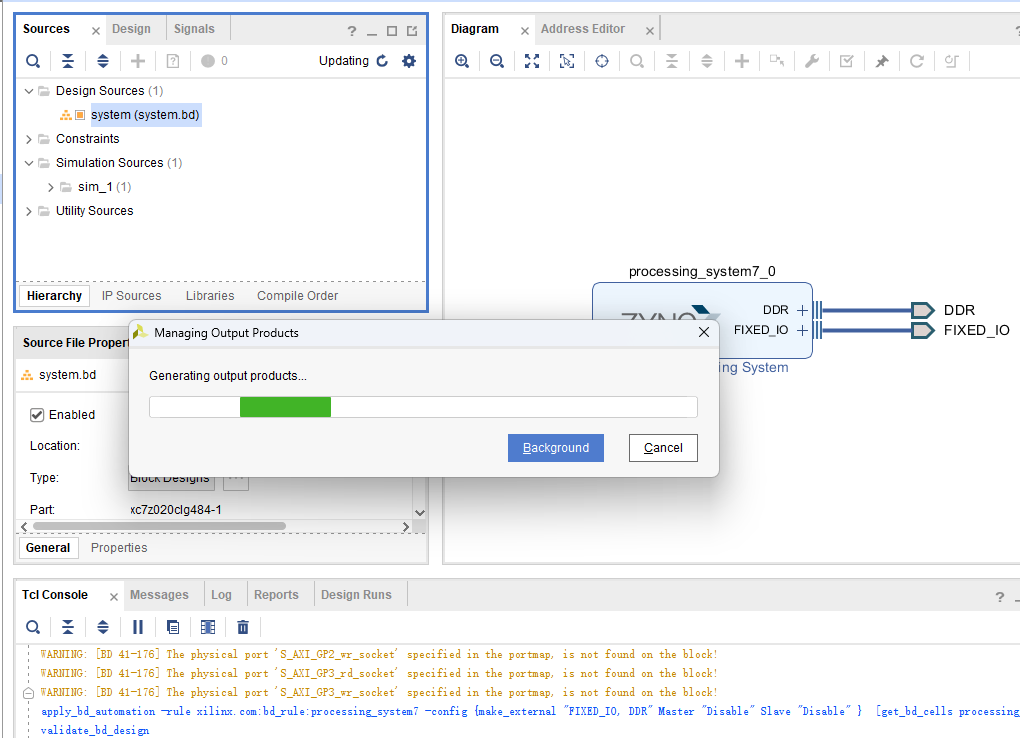

等待一段时间后:

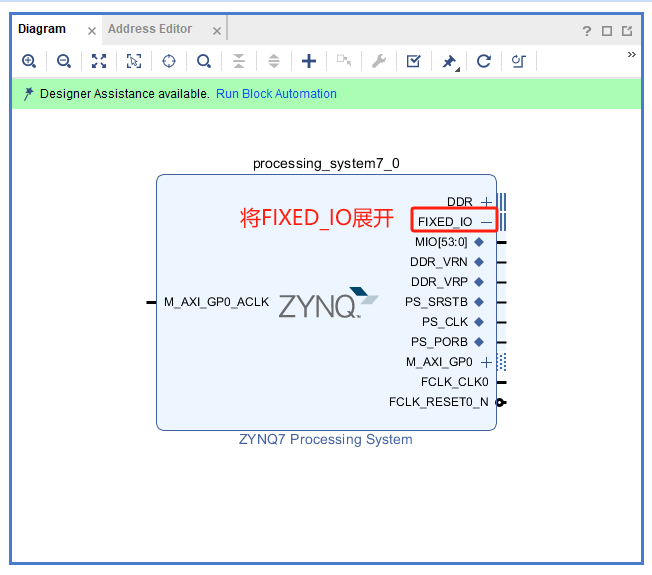

将FIX_IO展开(进行仔细检查)

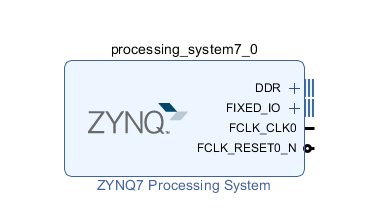

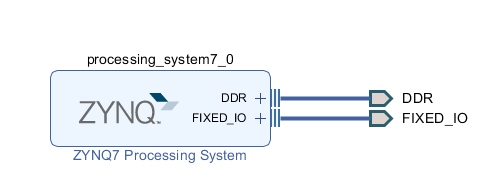

设置完之后,模块变为如下状态。

然后:

双击模块

向下滑动:

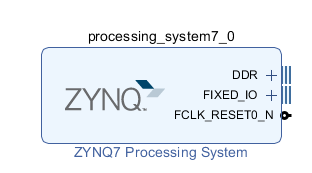

至此硬件配置完成:

开始创建端口:

端口自动创建完成

至此zynq的PS的配置结束了

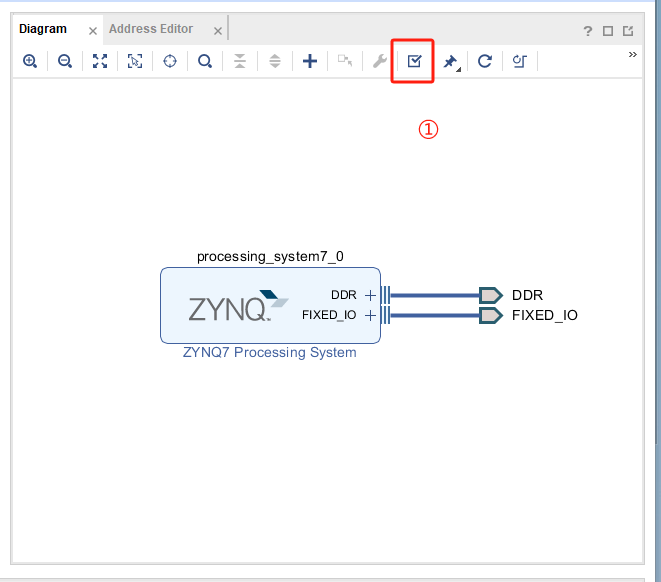

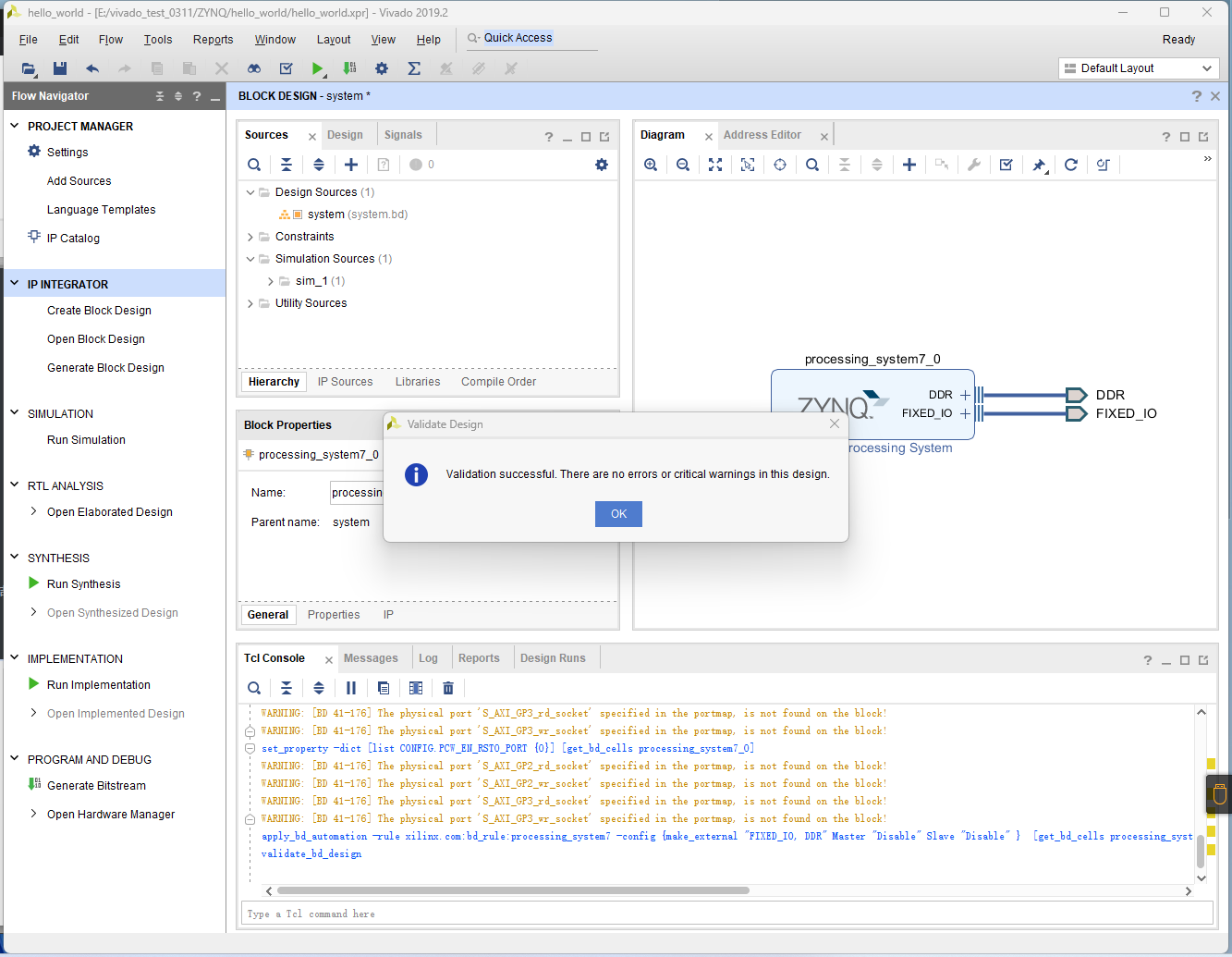

第11步:开始验证设计

验证成功:无报错和警告

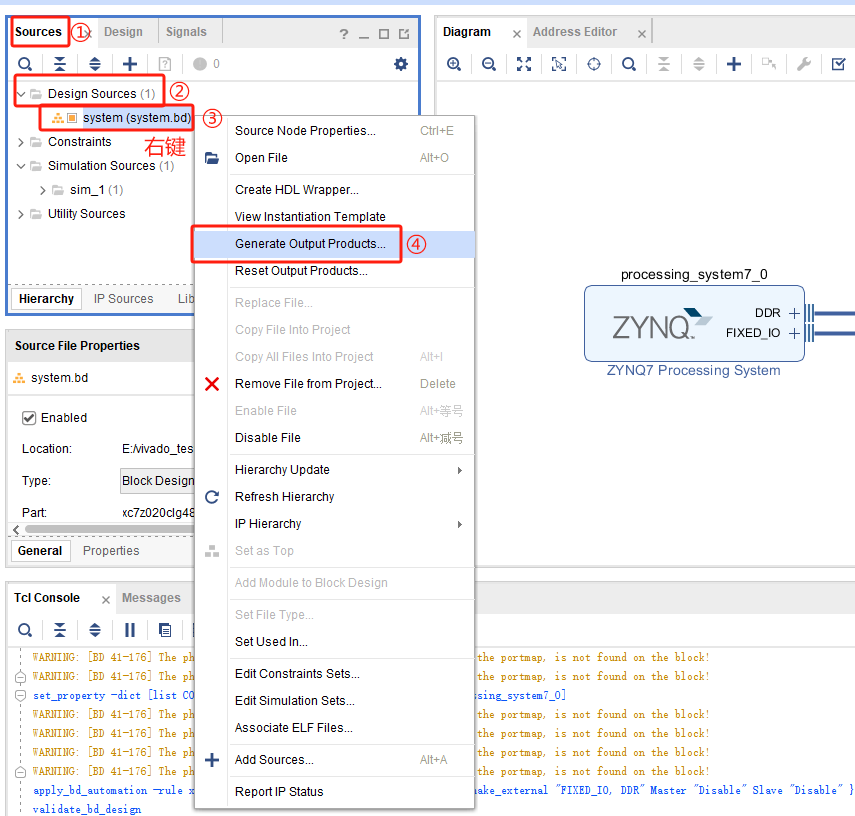

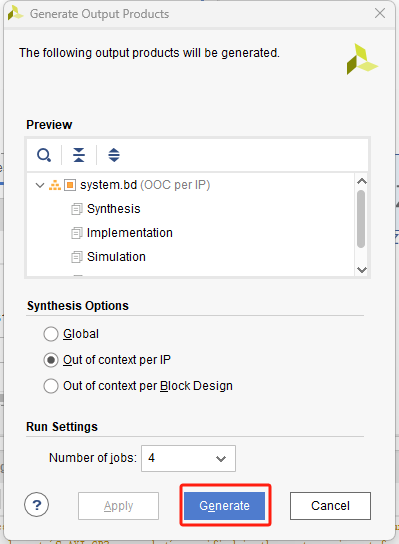

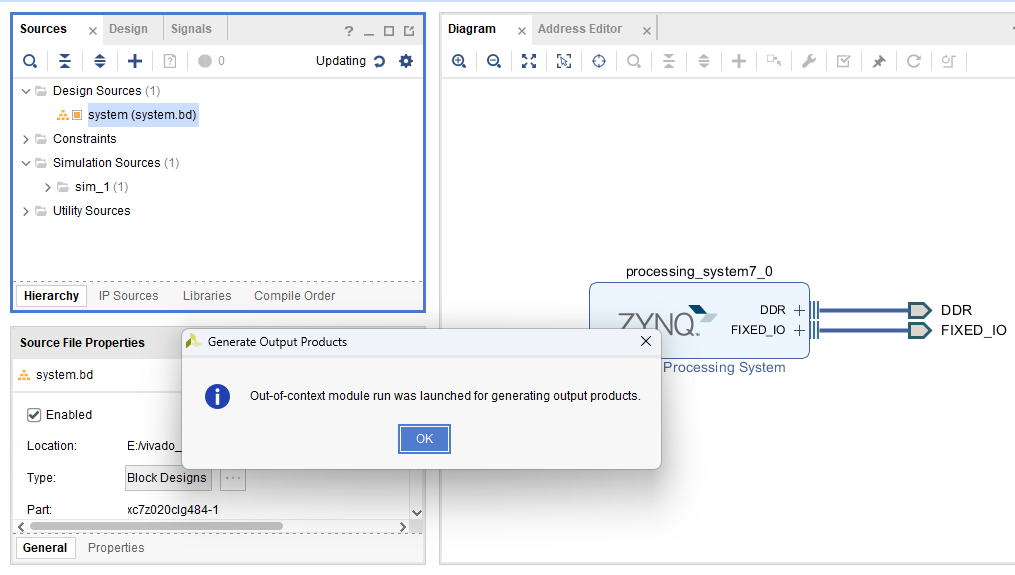

第12步:生成管脚约束

等待许久之后:

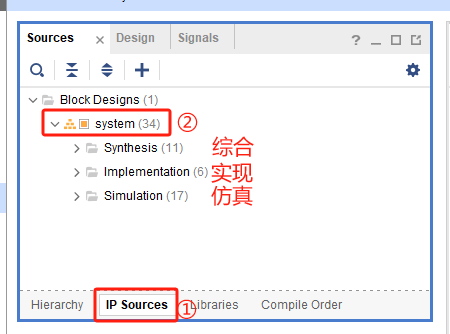

查看管脚约束,DDR约束

PS不需要手动的去对每一个管脚进行约束;

工具会自动的去进行管脚分配;

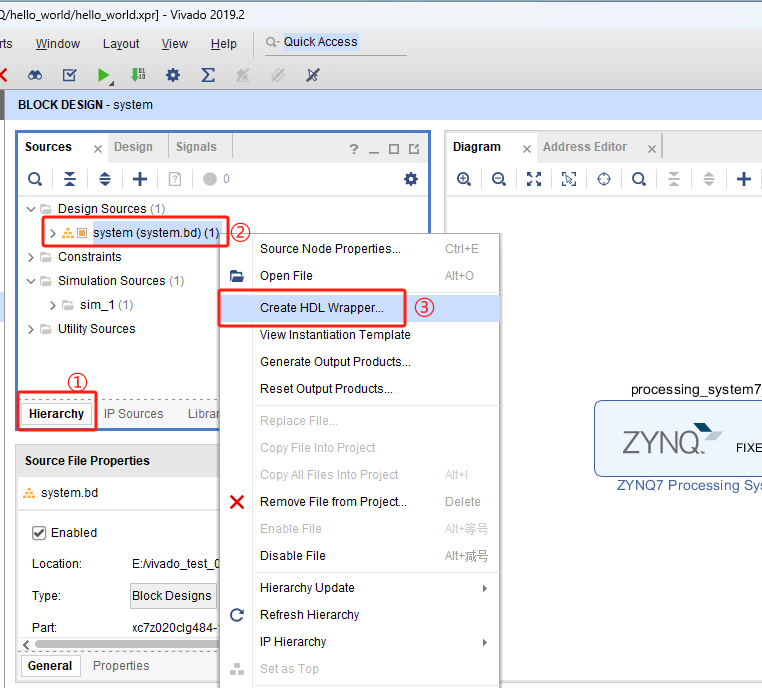

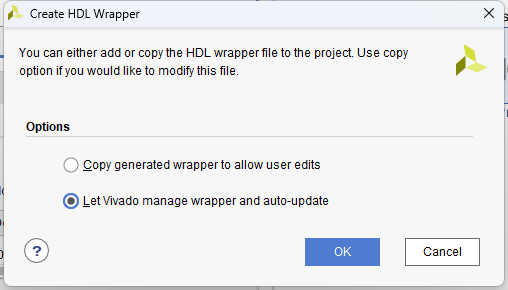

第13步:做HDL封装

为设计完成HDL(封装)

直接点击OK

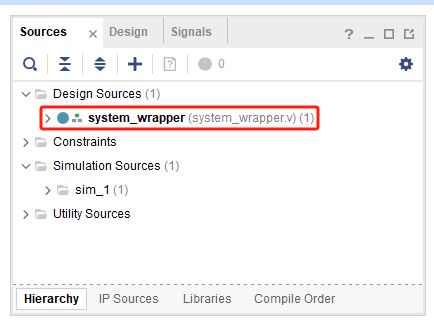

之后多了如下的文件:

此文件都是verilog语言:完成了对之前的设计的例化

至此硬件的搭建完毕;

不涉及PL部分的话,不用在此时生成比特流

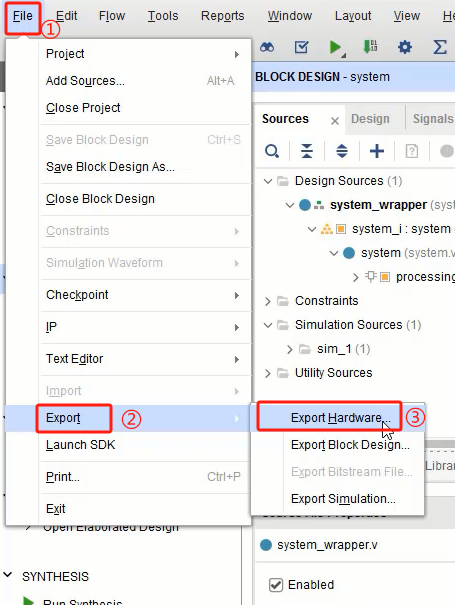

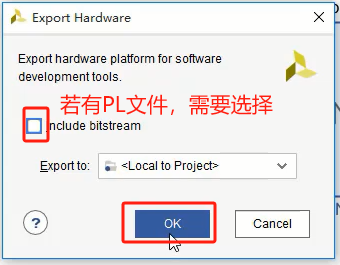

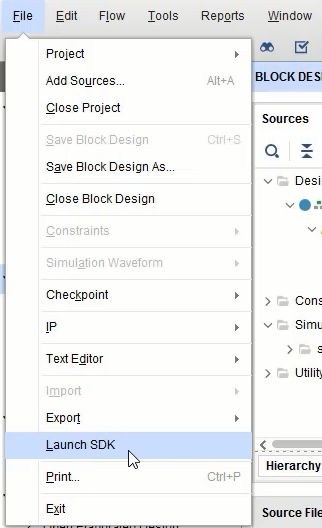

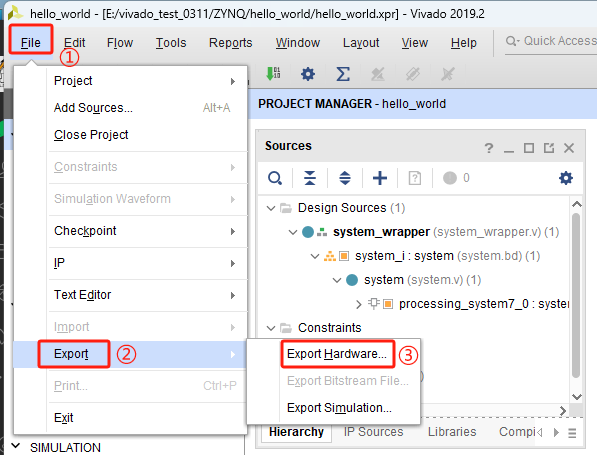

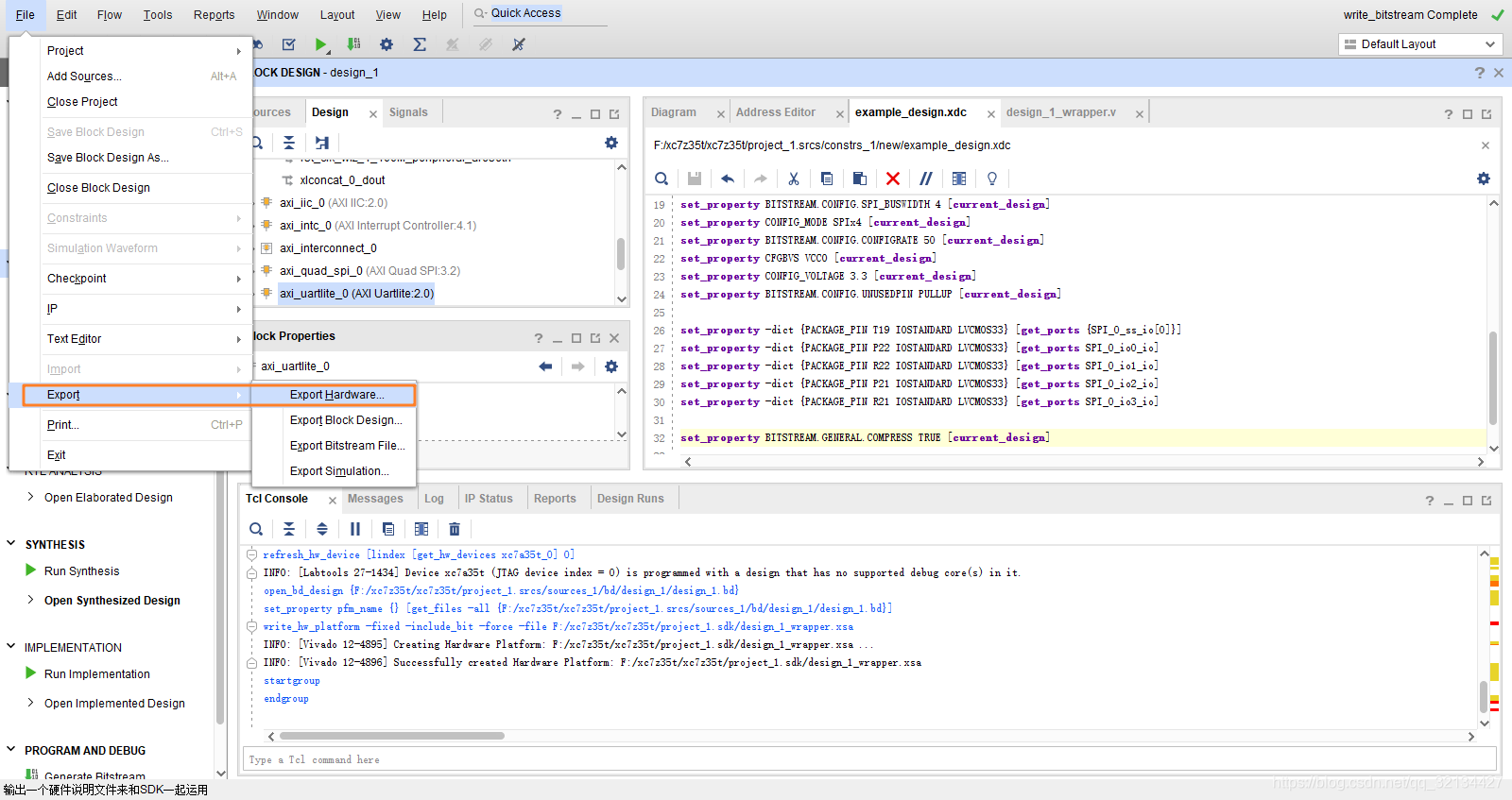

第14步:导出SDK

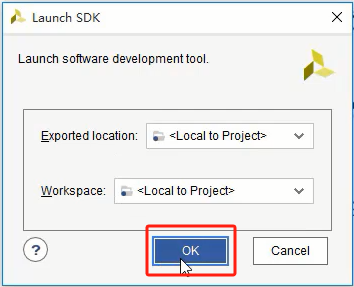

直接导出到SDK

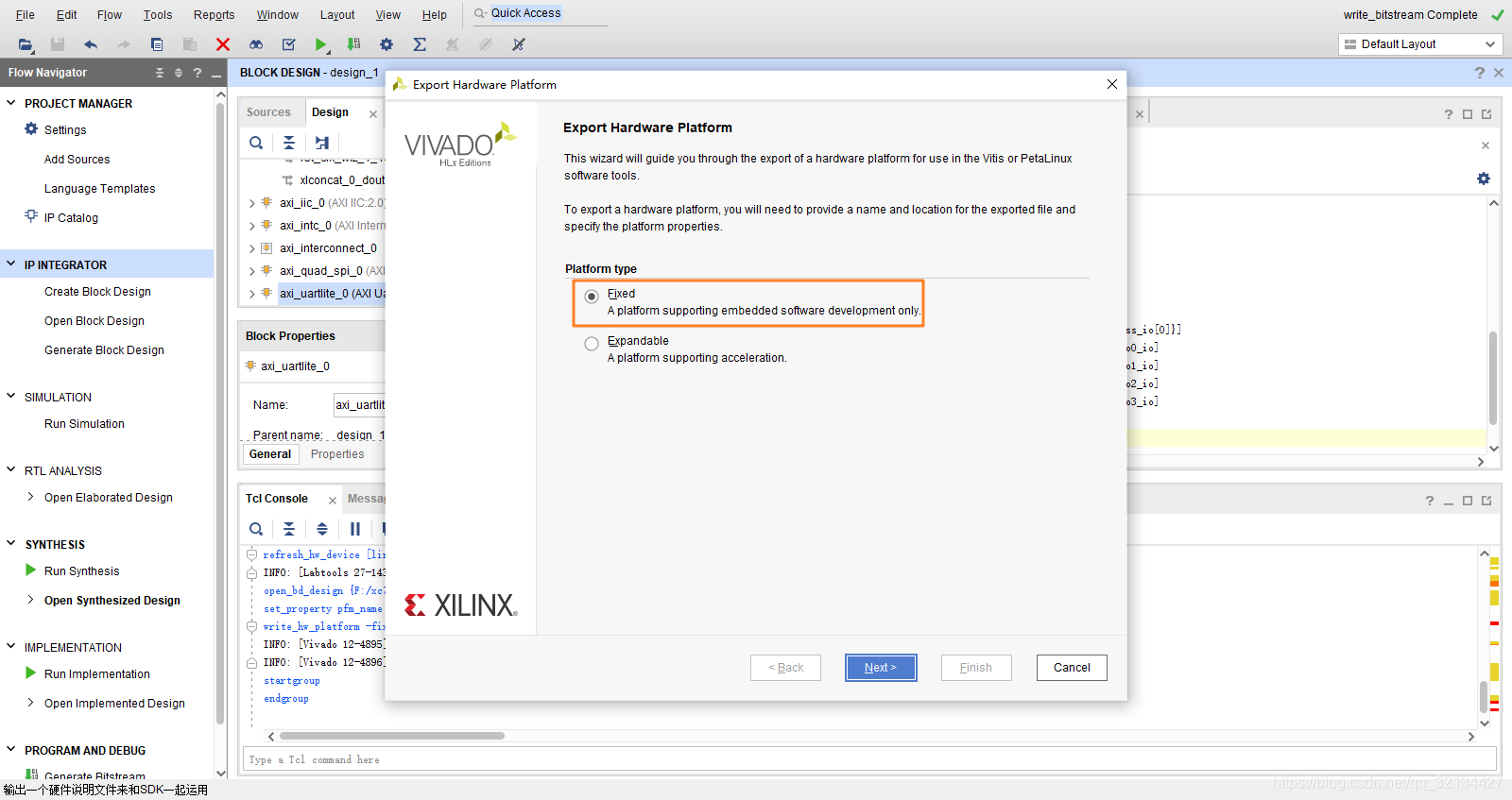

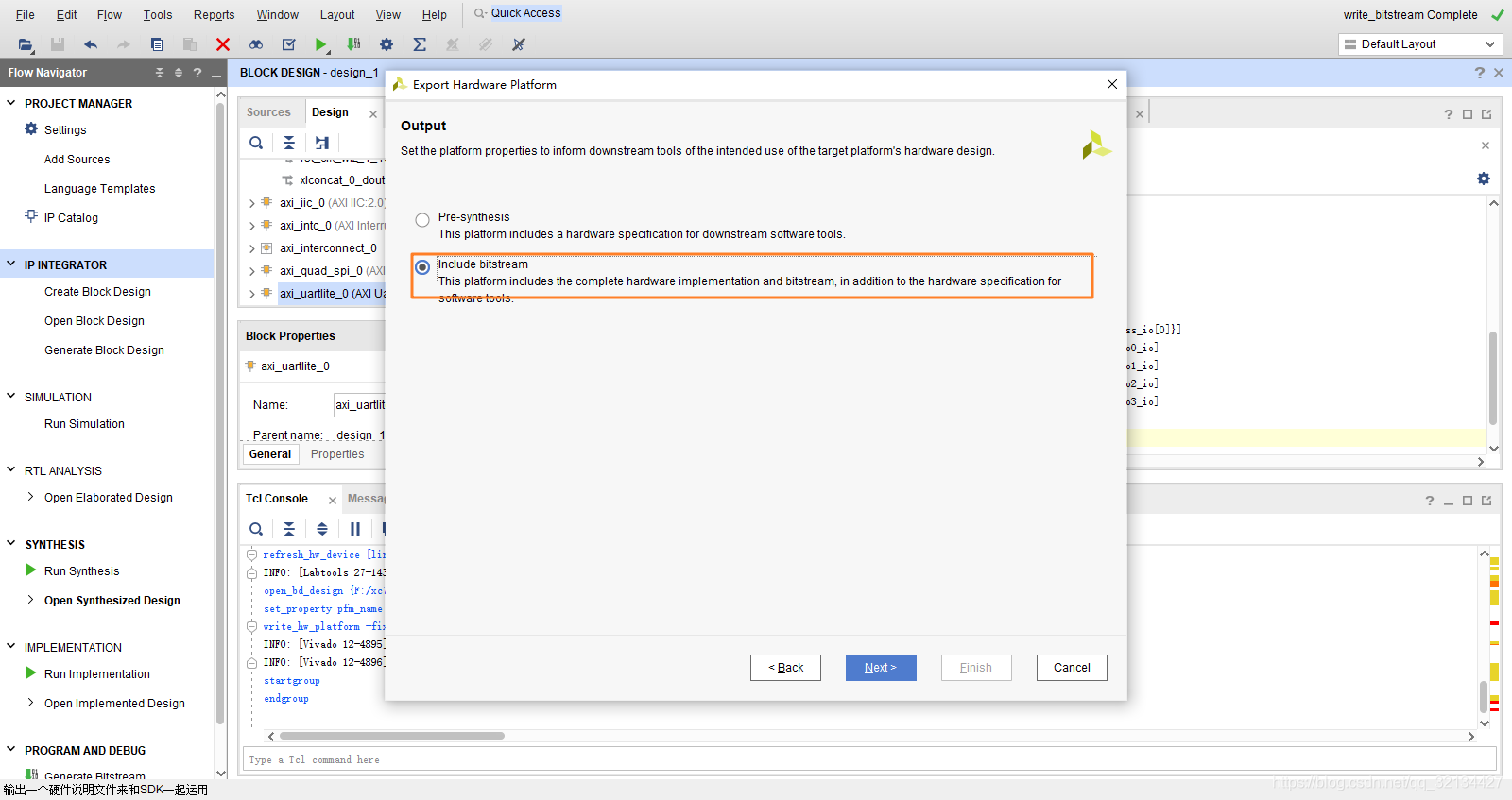

此选项包含是否需要包含比特流。(有PL文件的时候可以选择)

导出路径可以是默认工程的路径,也可以是自定义路径。

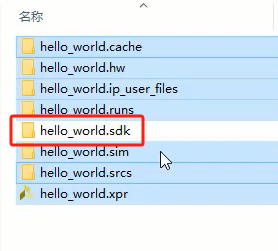

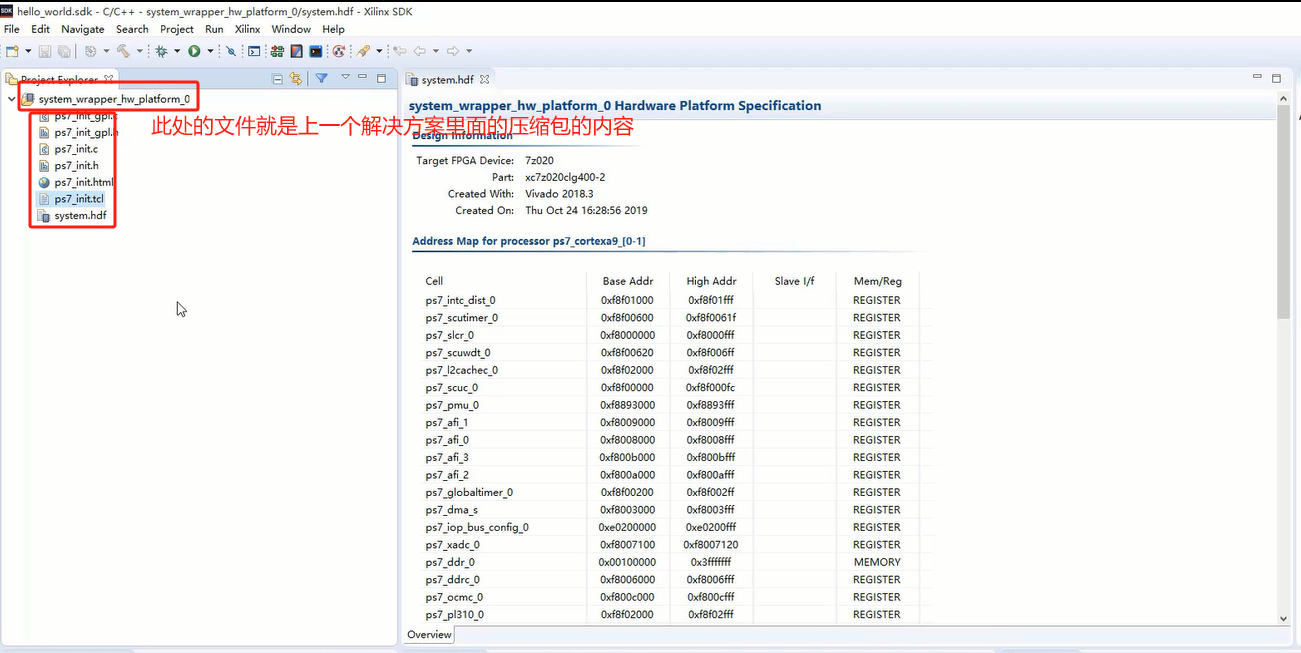

找到工程路径,此时生成了SDK文件。

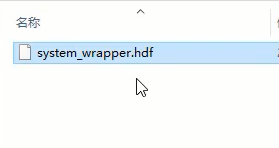

文件夹里面只有一个文件

方法①:(不推荐)

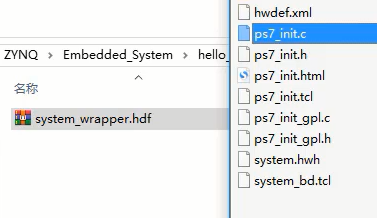

用解压软件打开此HDF文件,解压出的文件之后会用到

方法②:用SDK(VIVADO)解决(本次采用的)

vivado2019.2之前的版本含有SDK可以用这个方法:

vivado2019.2之后的版本推出了Vitis工具 来替换了之前版本的SDK功能。

出现如下的状态的

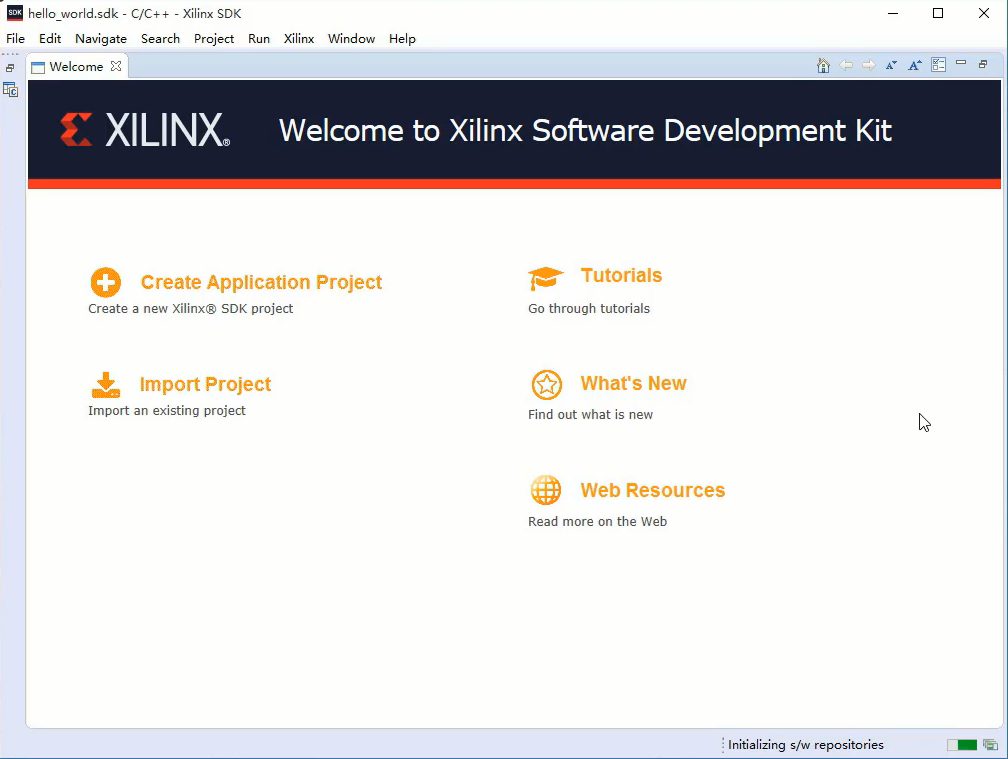

打开了此软件开发环境;

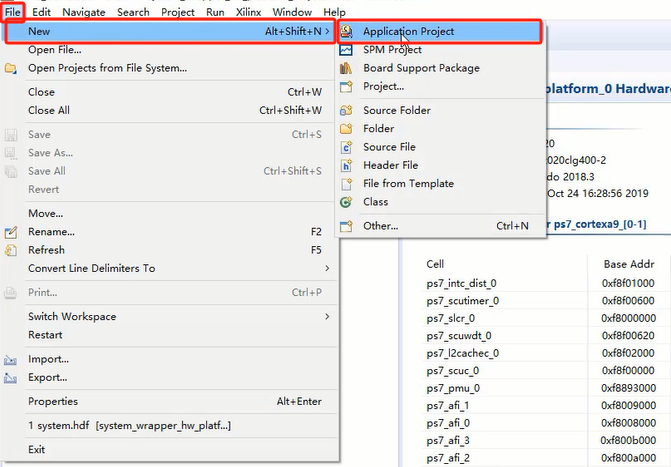

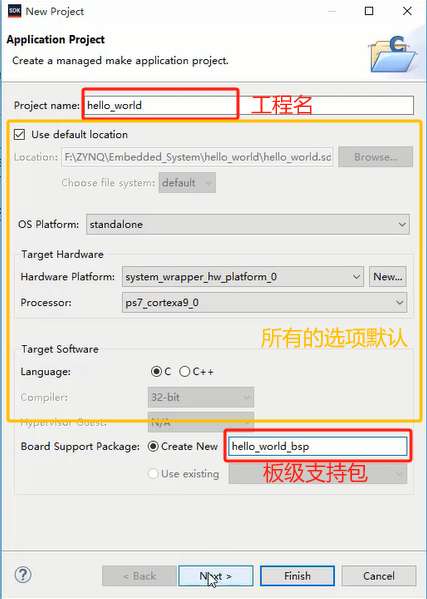

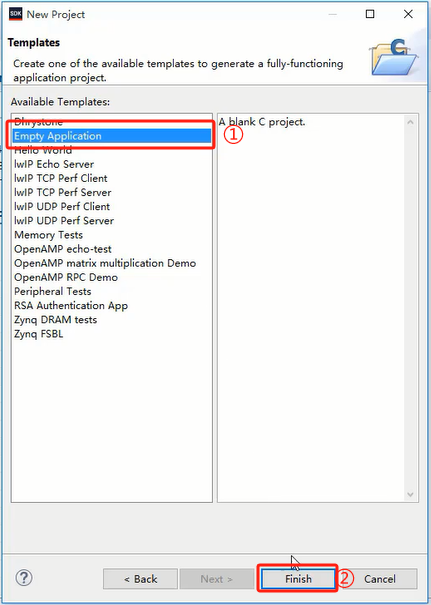

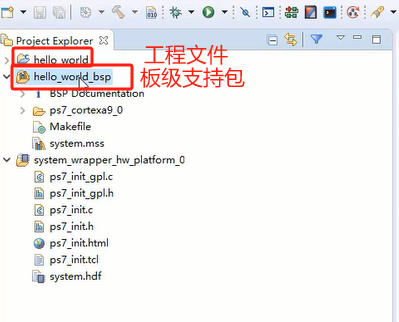

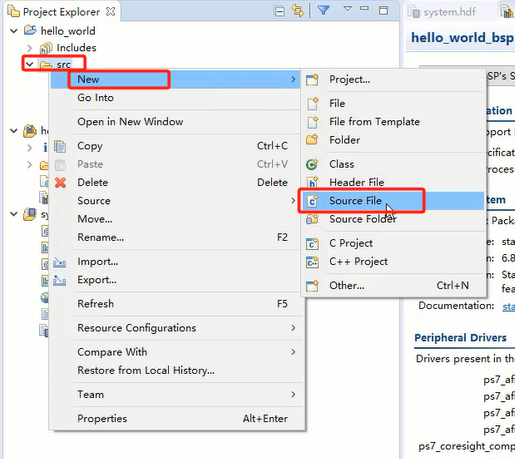

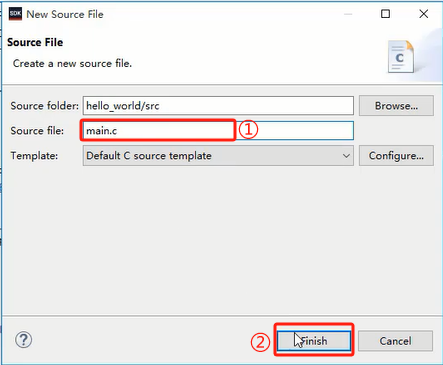

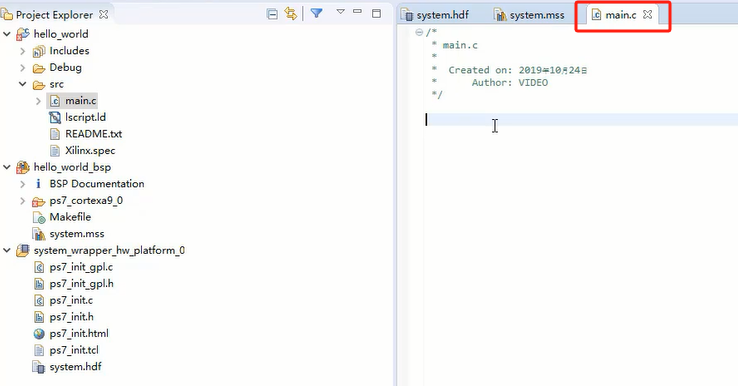

创建C文件:

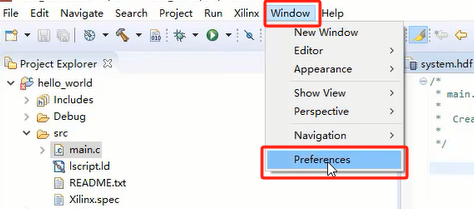

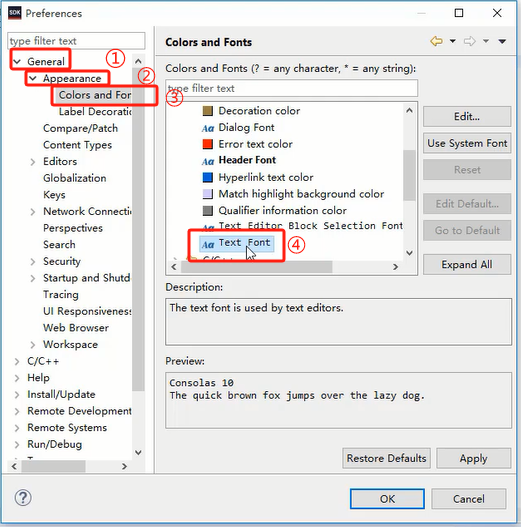

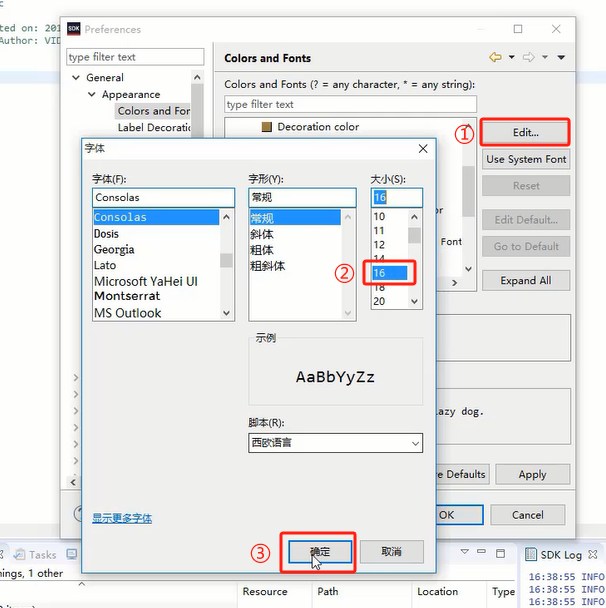

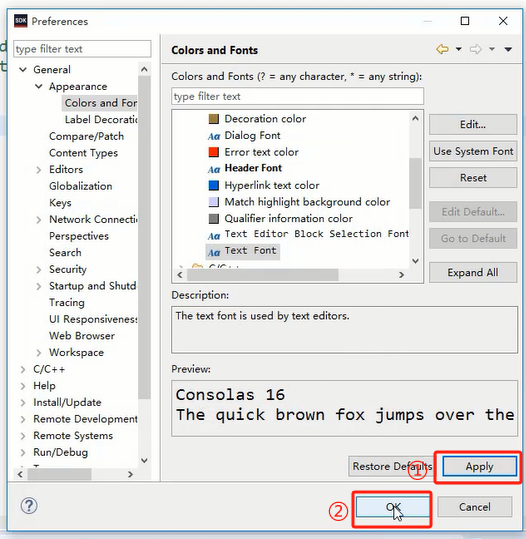

设置字体;

设置字号:

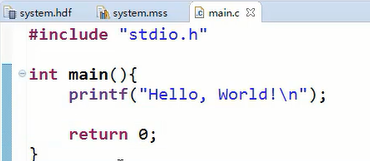

测试代码:

#include:"stdio.h"

int main(){

printf("Hello, World!\n");

return 0;

}

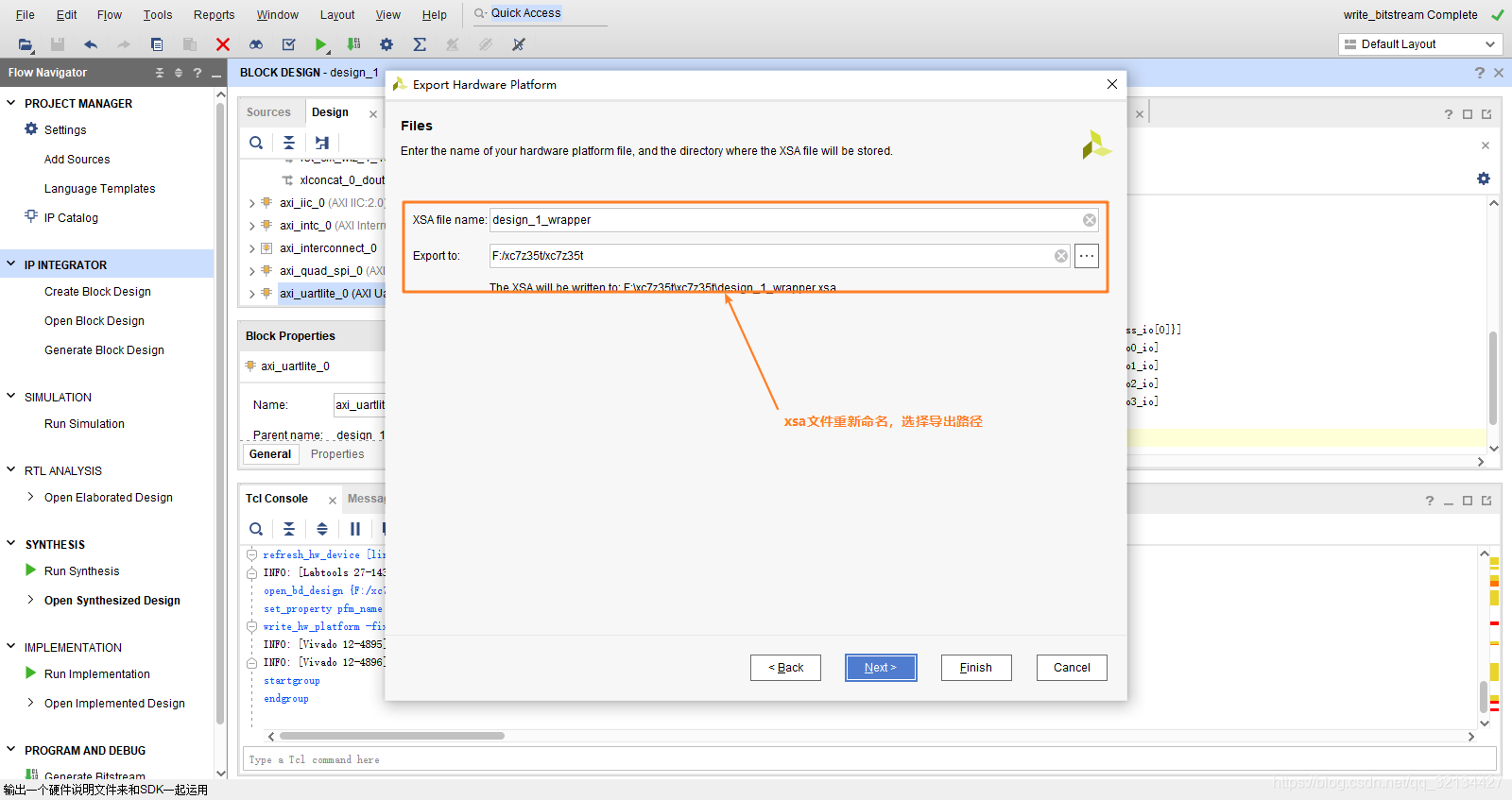

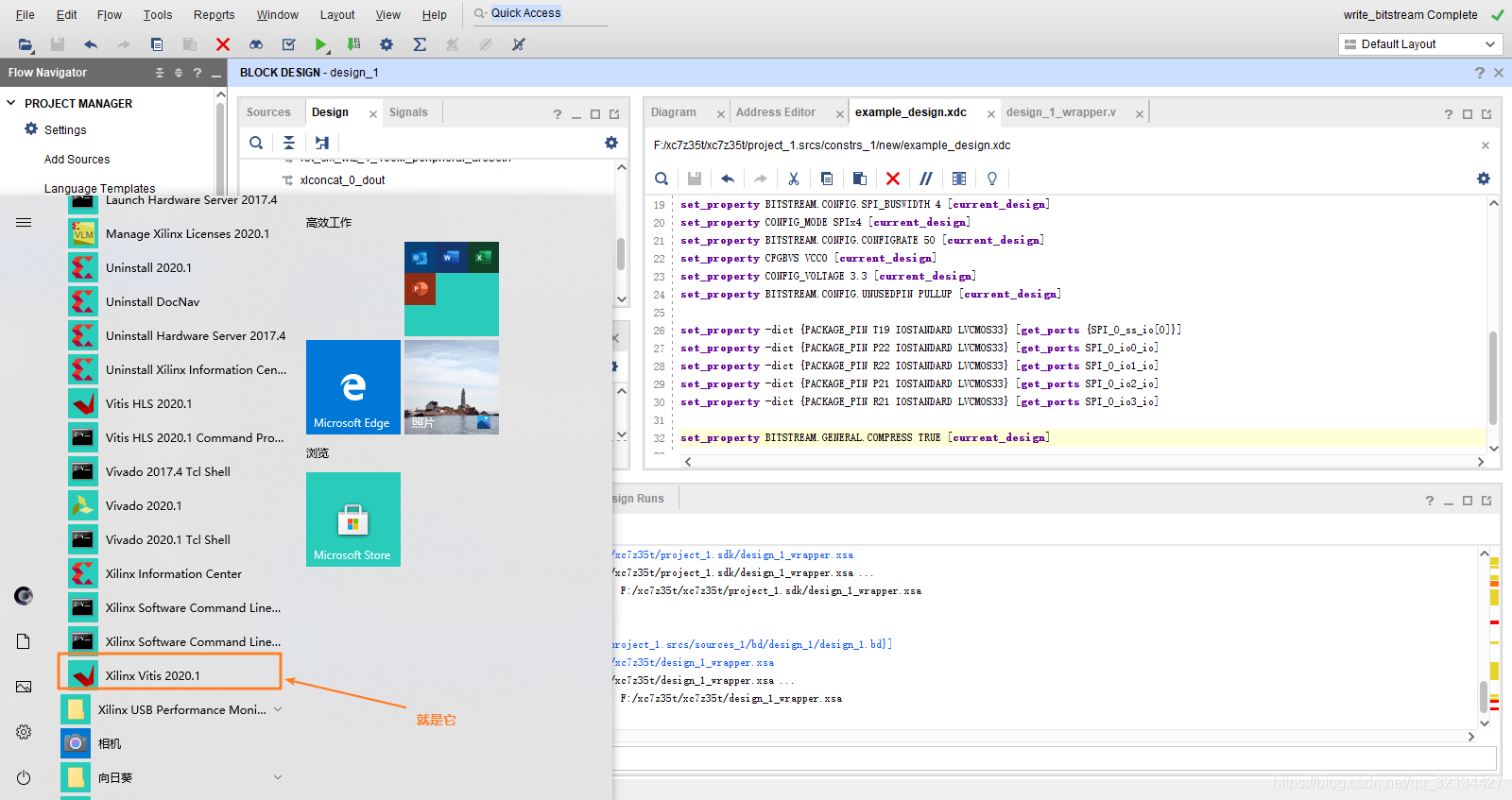

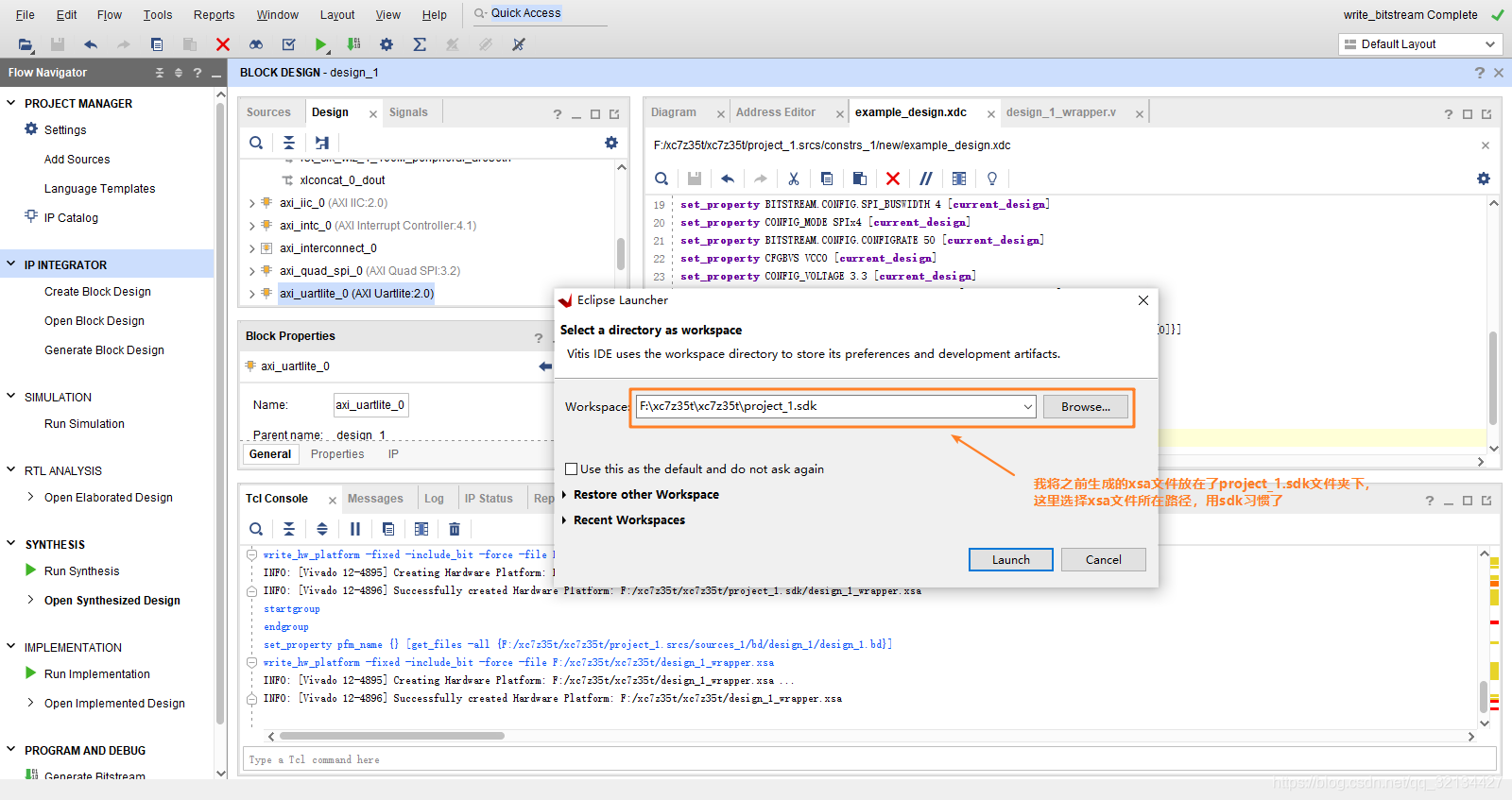

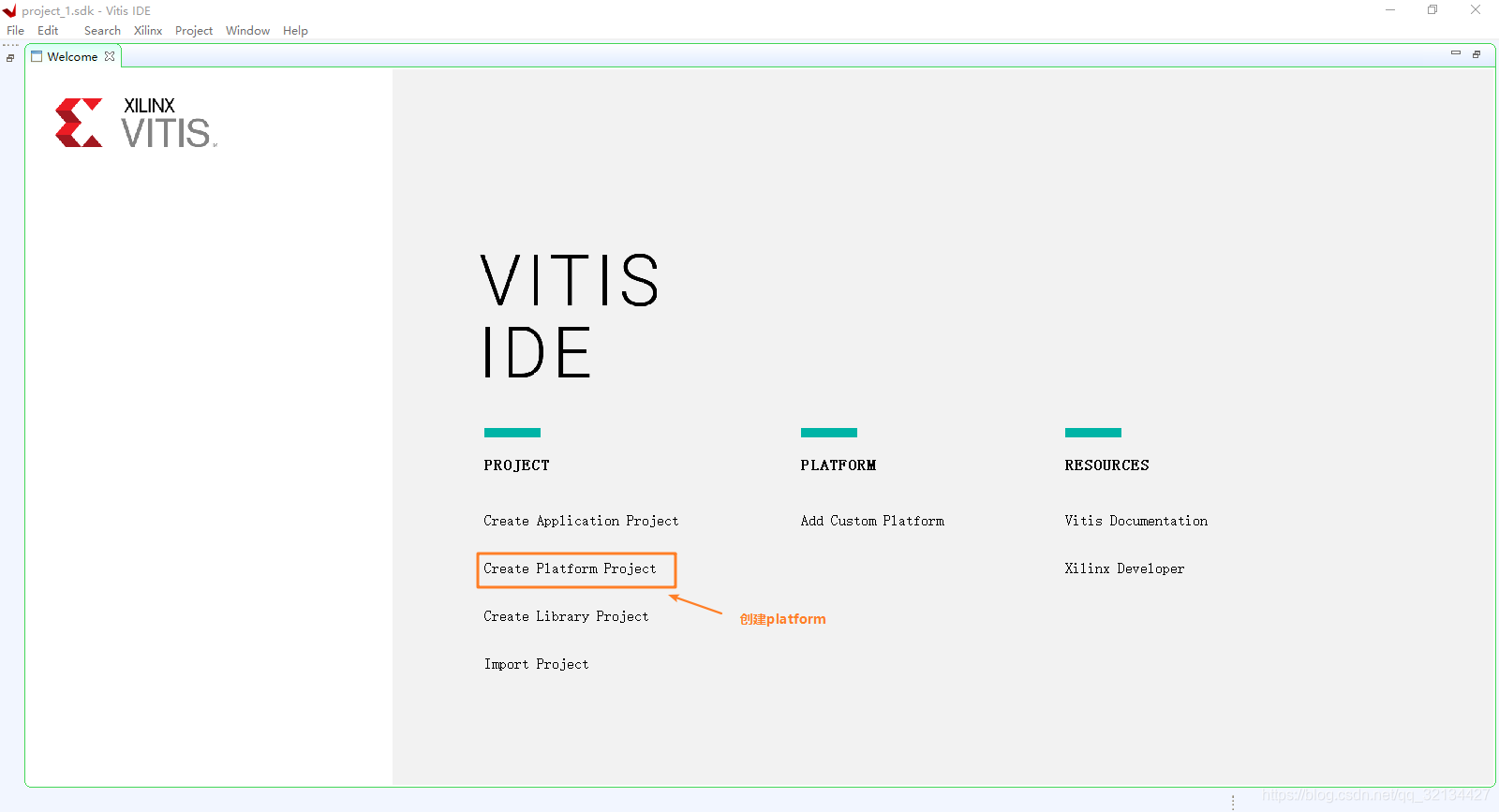

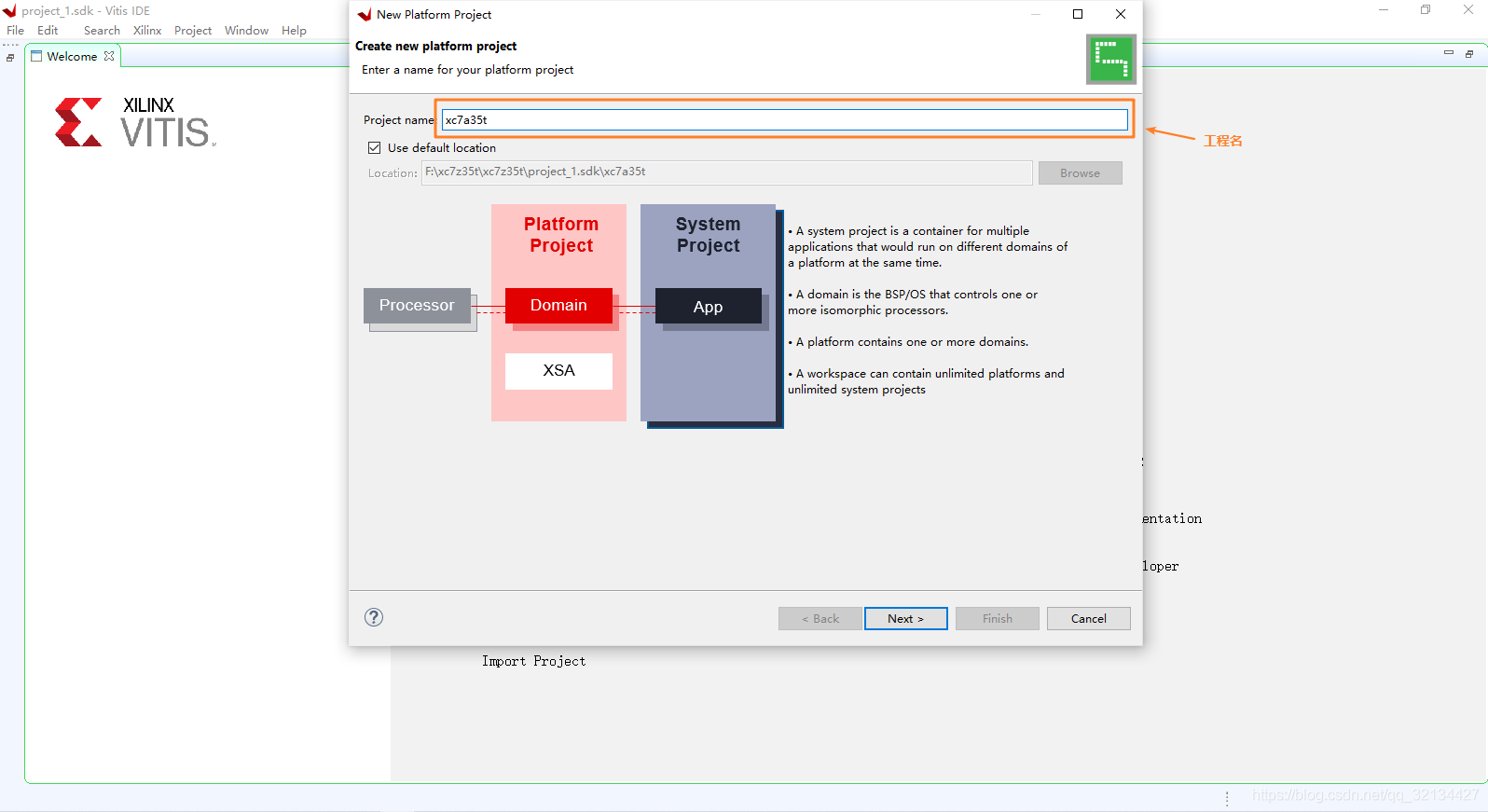

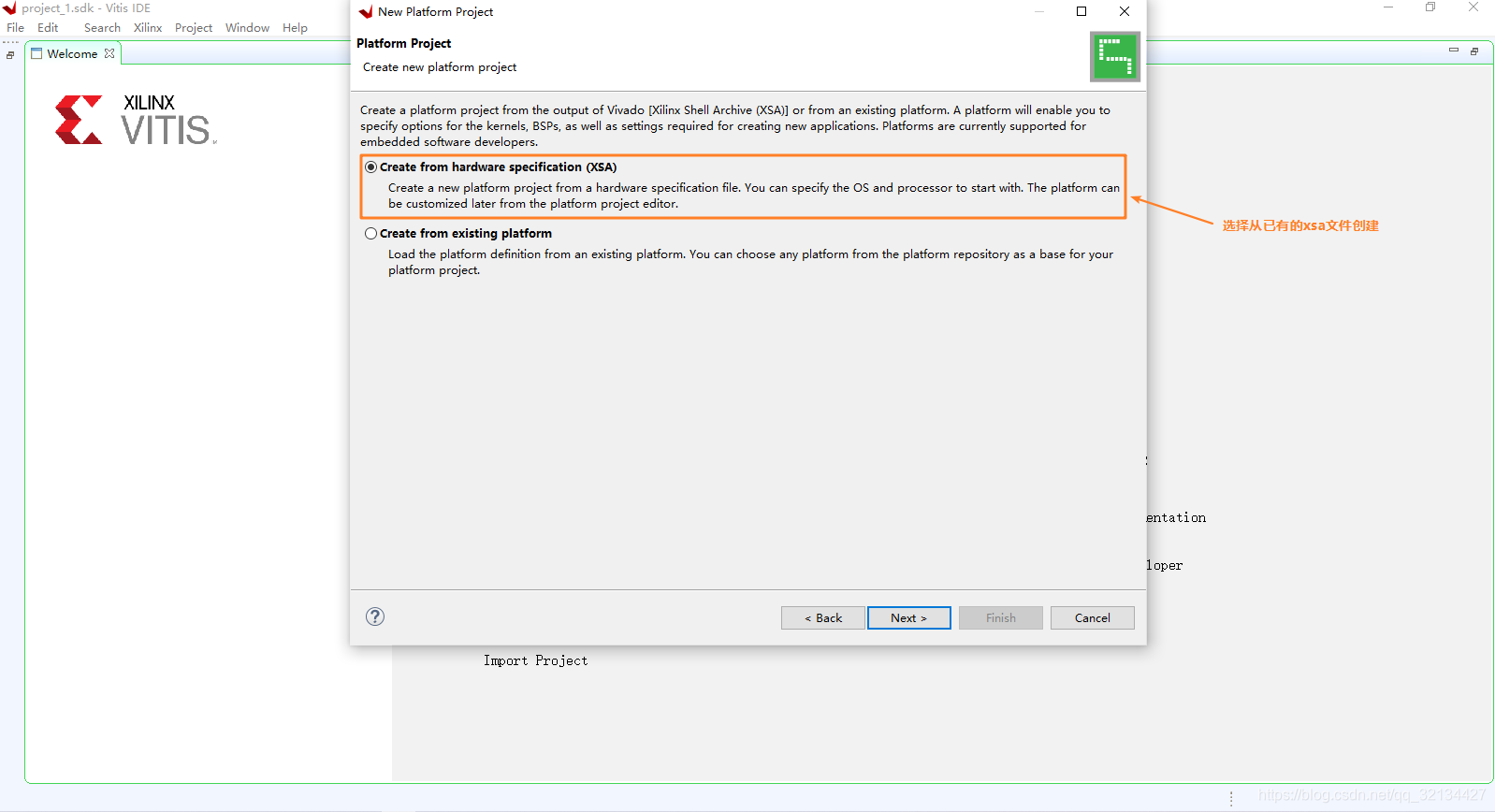

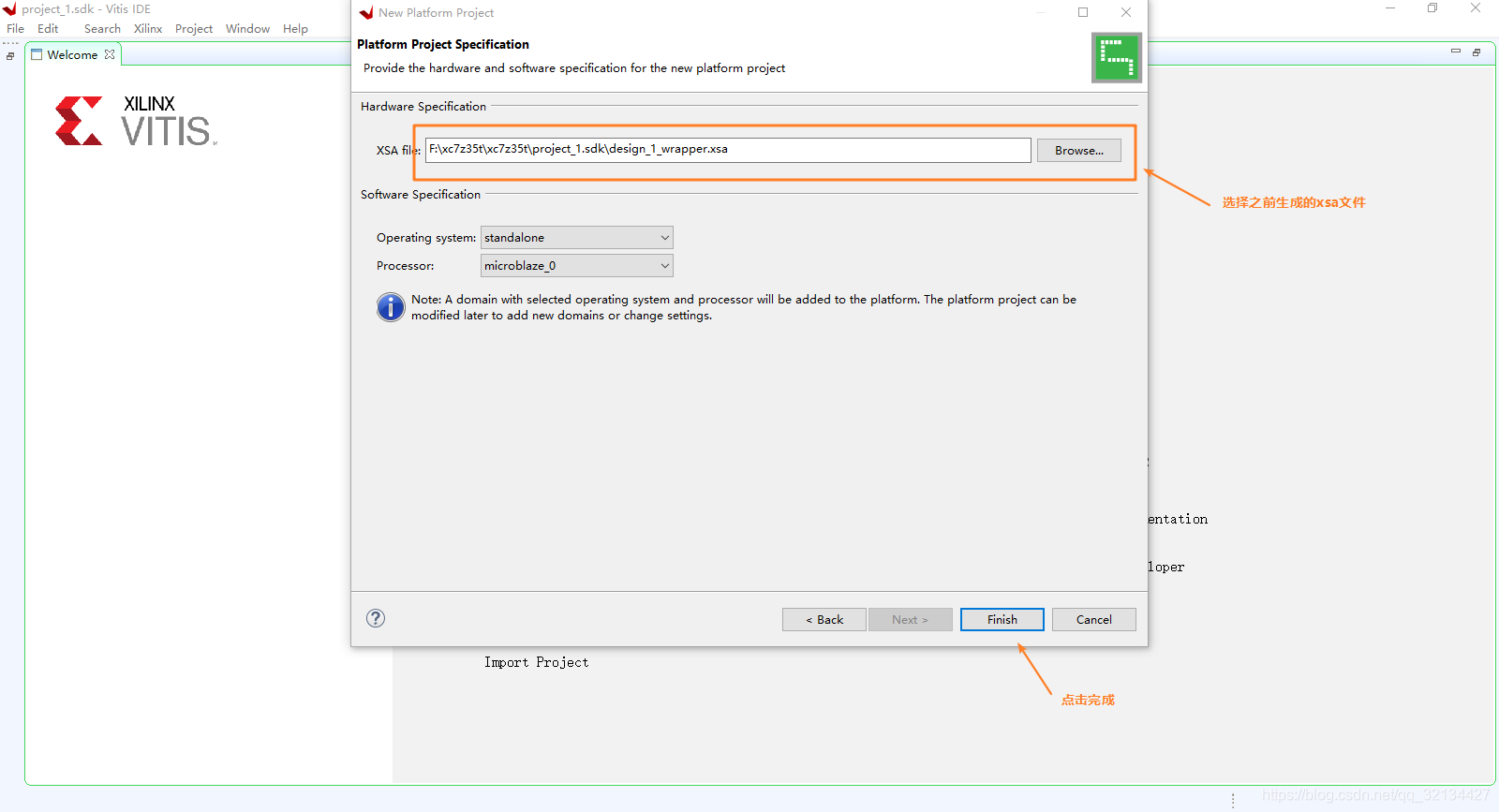

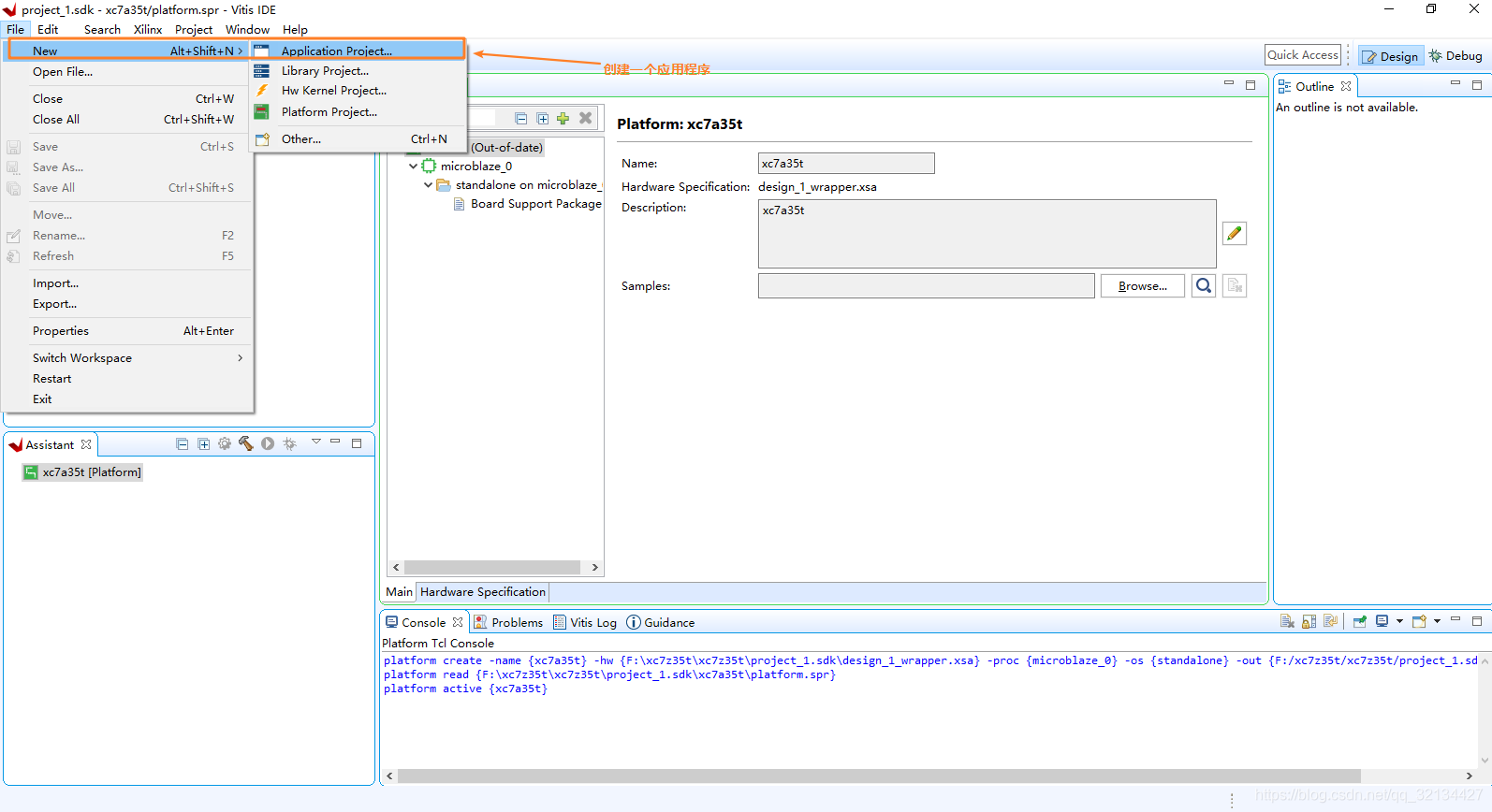

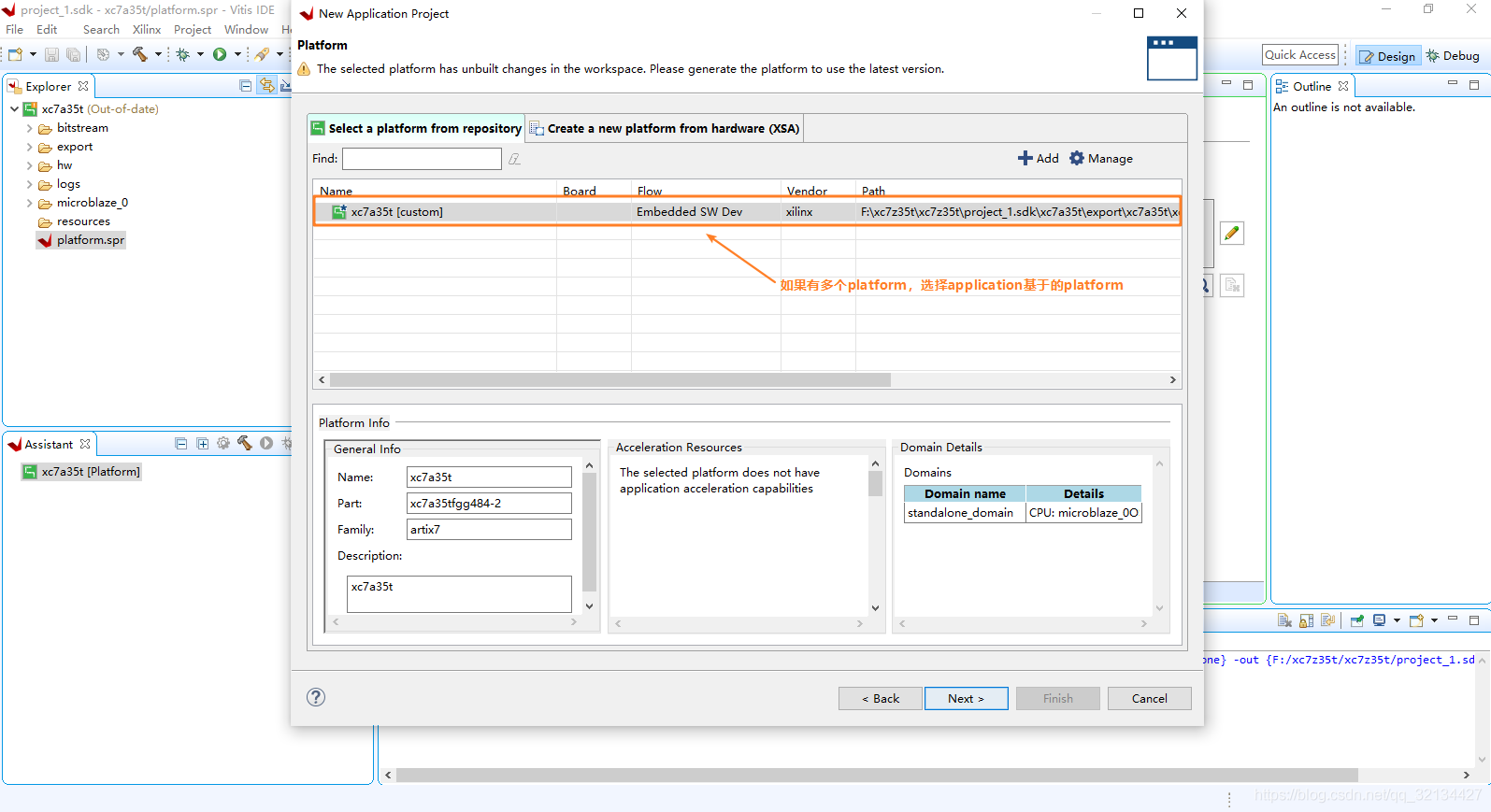

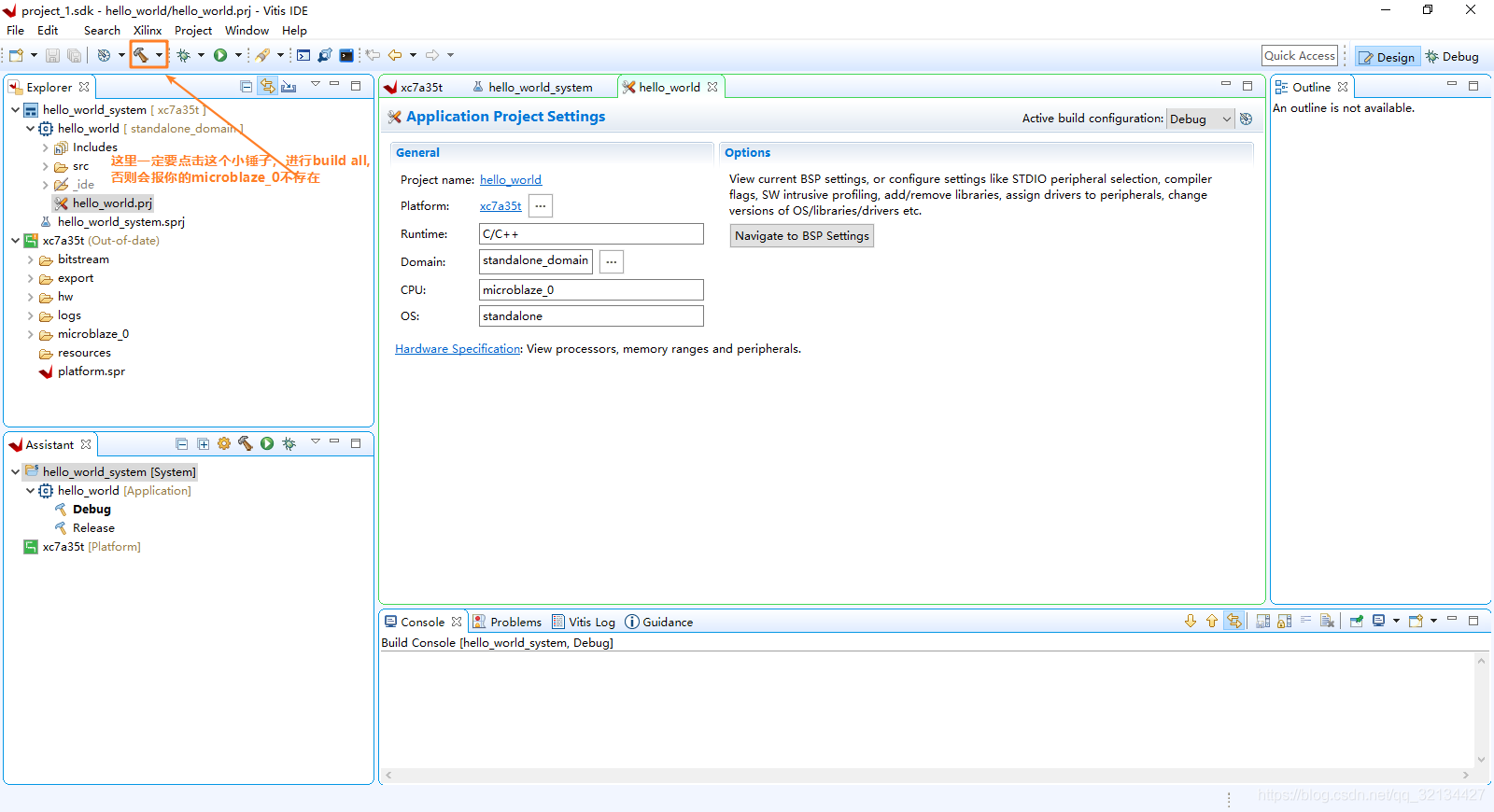

方法③:VITITS(vivado2019.2之后的版本采用的)

然后到处xsa文件:

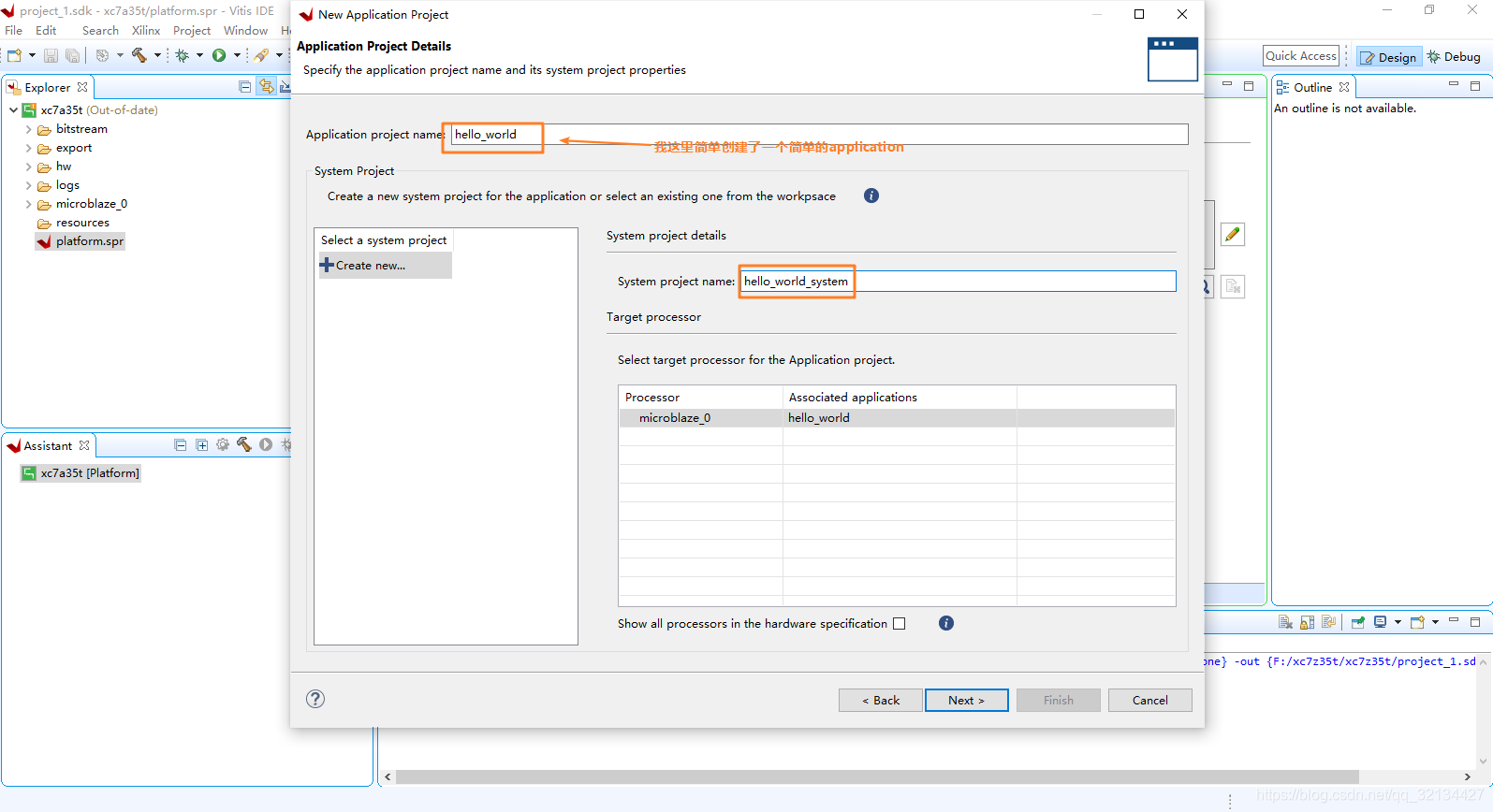

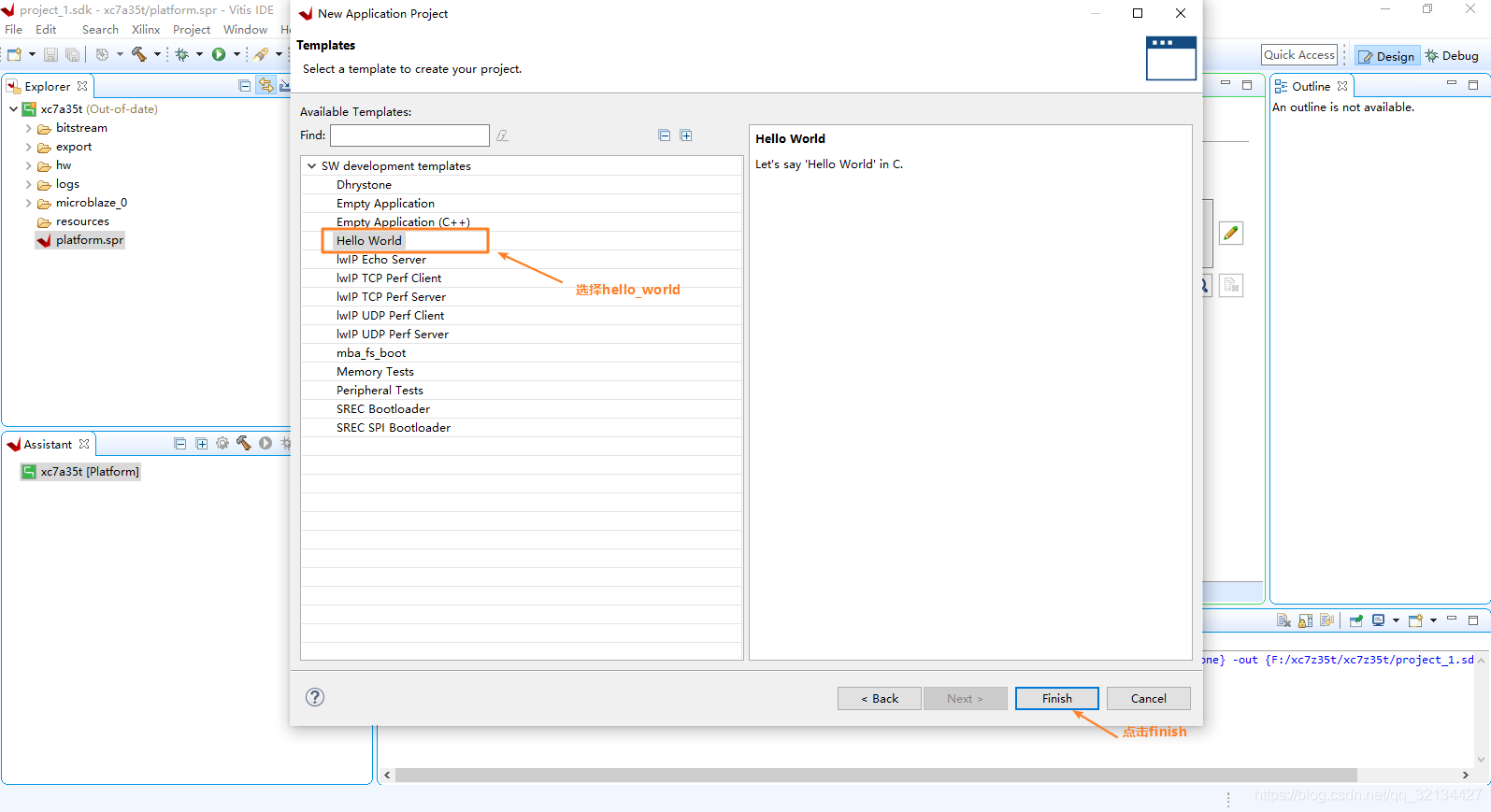

然后就一路next直到finish.

2.手动找到vitis的快捷方式进入vitis(vivado)中已经没有launch选项了,只能手动登录):

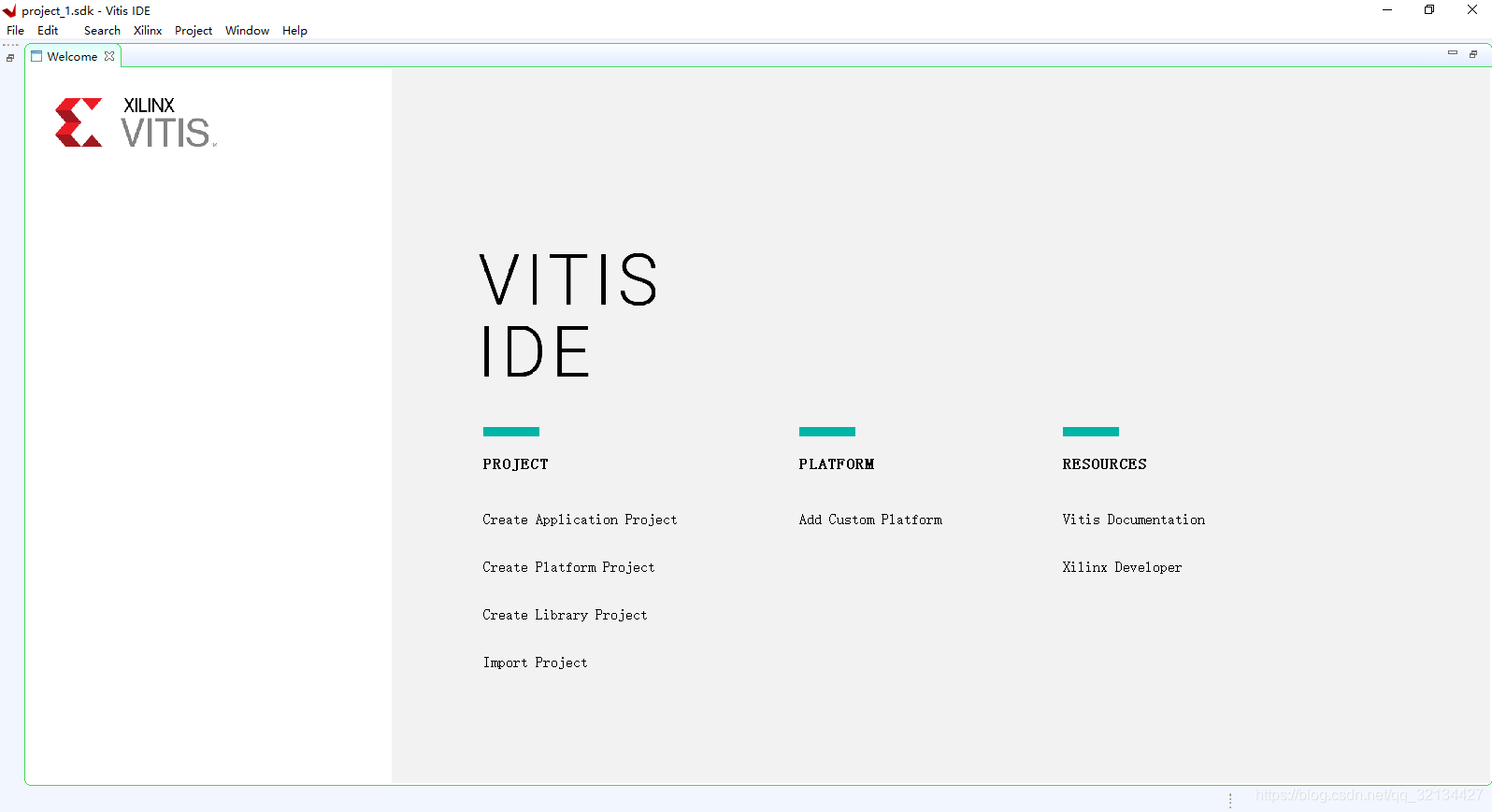

等待进度条跑完,我们就进入了vitis的主界面。

接下来我就不会配那么多文字了,按照图片一页一页操作吧:

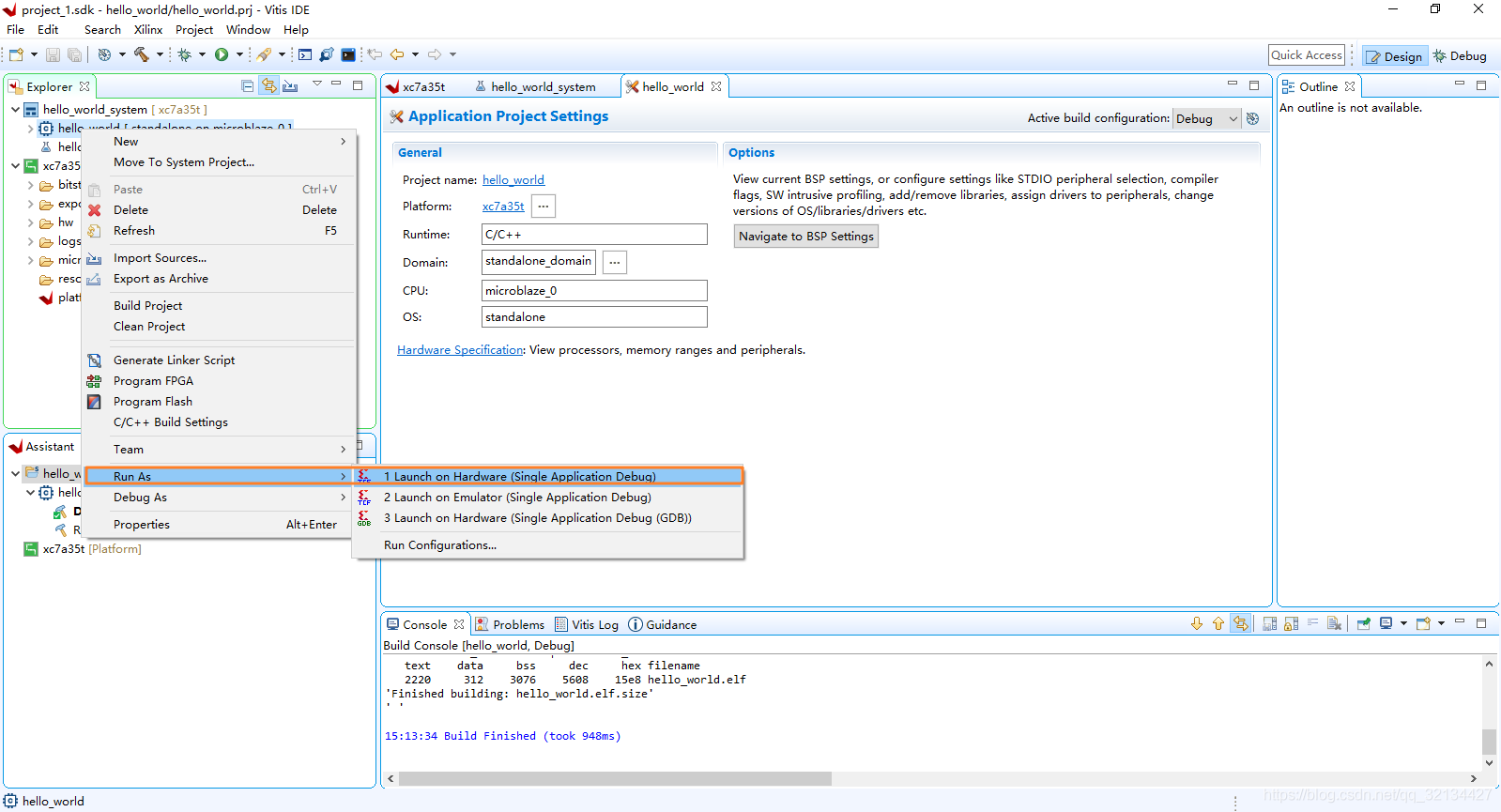

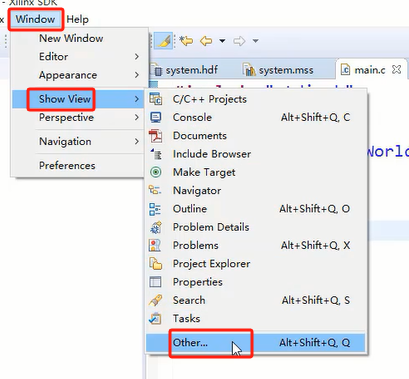

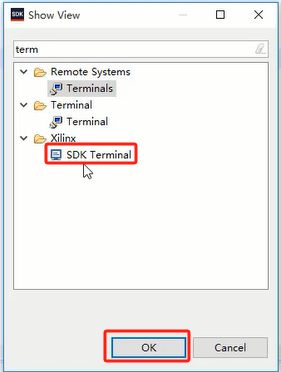

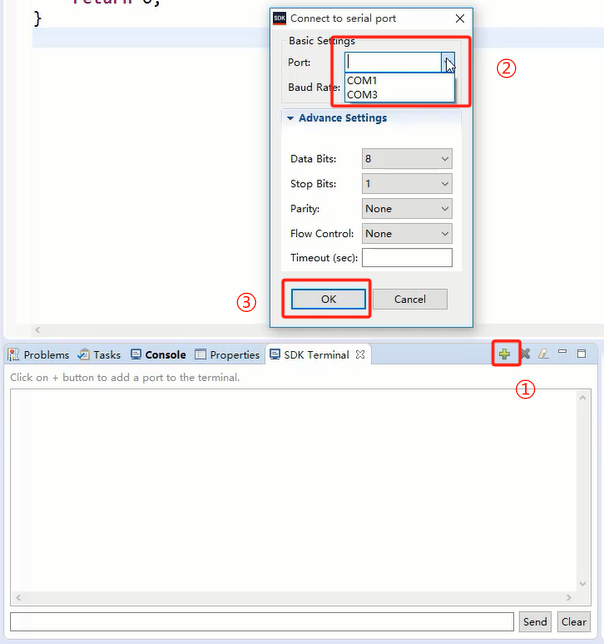

第15步:下载验证:

连接zynq:

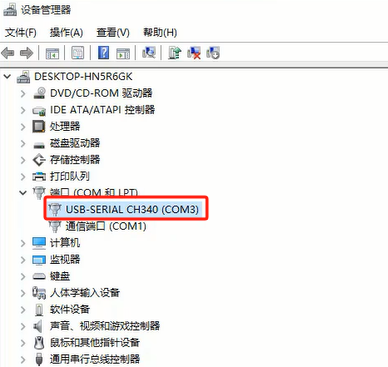

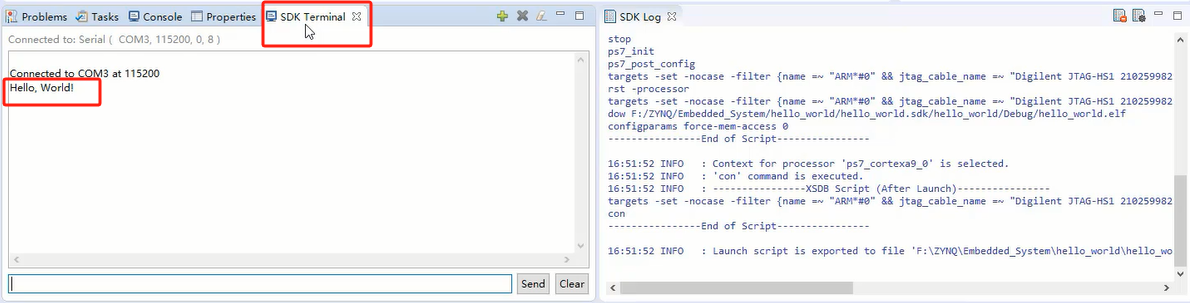

打开设备管理器确认串口位置:

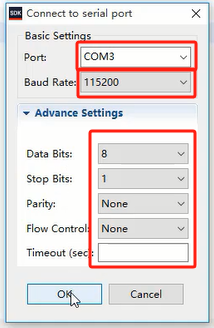

确认好端口、波特率。

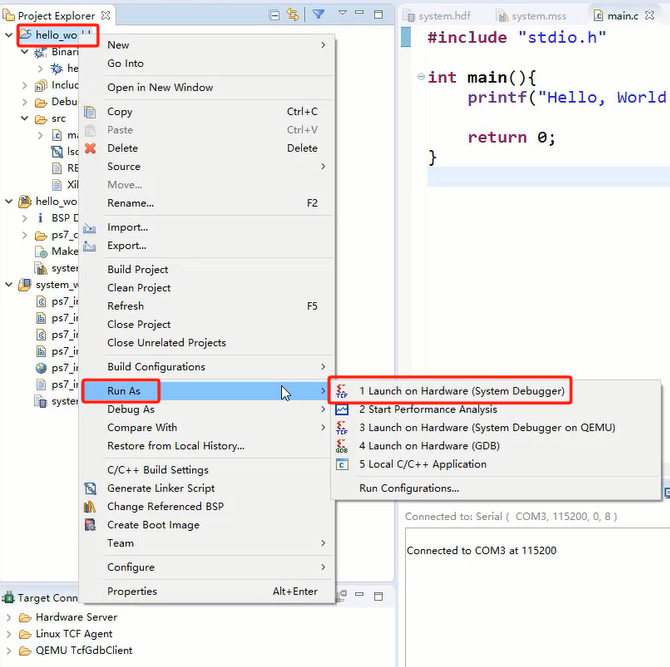

在工程文件上方右键:

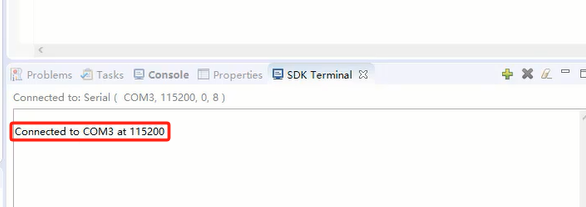

成功显示了 helloword,证明本次实验的结果是成功的

此程序是 ps端的程序通过串口输出给笔记本电脑的一个语句;

浙公网安备 33010602011771号

浙公网安备 33010602011771号