Xilinx ISE下的静态时序分析与时序优化

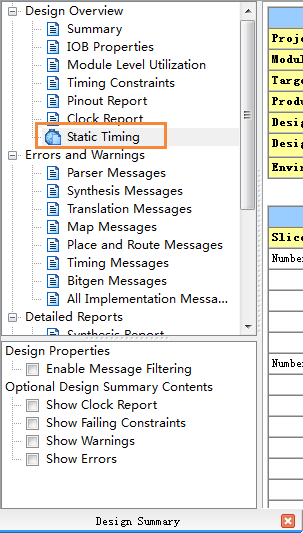

单击Design Summary中的Static Timing就可以启动时序分析器(Timing Analyzer)。

在综合、布局布线阶段ISE就会估算时延,给出大概的时延和所能达到的最大时钟频率,经过PAR后,在Static Timing中给出的是准确的时延,给出的时序报告可以帮助我们找到关键路径,然后针对其进行优化,提高系统的时钟频率。

这里的Minimum period指的是最小的逻辑延迟;

造成时序性能差的原因很多,主要缘由以下几种:

1. 布局太差

一般和代码本身没有关系。解决方案:只能从软件自身的布局算法考虑(调整布局的努力程度)或者使用高端芯片

2. 逻辑级数太多

逻辑级数越多,资源的利用率越高,但是对工作频率的影响也越大。解决方案:1.使用流水线技术;2.如果是多周期路径,添加多周期约束;3.良好的编码习惯,不要过多嵌套if-else,尽量使用case代替if语句。

3. 信号扇出过高

高扇出会造成信号传输路径过长,从而降低时序性能。解决方案:1.逻辑复制;2.区域约束,想过逻辑放置在一起。

4. 不要同时使用双边沿触发

FPGA的底层工艺都是单向的同步电路,所以本身不支持统一信号的双边沿触发,ISE在实际处理的时候,会自动将该信号2倍频,然后利用第一个沿处理上升沿,第二个沿处理下降沿。这样在分析时序时,自动把约束升级为ucf文件中的两倍。

5. Xilinx最优时序解决方案

1.I/O约束

根据Xilinx器件的特点,控制信号置于器件的顶部或底部,且垂直布置;数据总线的I/O置于器件的左右两侧,且水平布置,这样可以最大程度的利用芯片底层结构。

2.ISE实现工具

ISE中的工具具备不同的努力程度,直接使用最高级别的可以提高时序性能,但是会耗费很多时间,所以应该逐步调整努力程度。第一遍使用默认的参数选项,如果不满足 再调整综合、映射、布局布线的参数。

时序优化的若干策略

优化方向一:合理使用Blcok RAM和Distributed RAM

1. 均衡Block RAM和Distributed RAM的使用。如果Block RAM使用的过多而Distributed RAM使用的较少,建议将一些小型的FIFO用Distributed RAM来实现;如果Distributed RAM使用的过多,而Block RAM有大量富余,建议将一部分由Distributed RAM实现的FIFO改用Block RAM来实现。

2. 当需要使用Block RAM来构建大型的FIFO用作缓存时,由于Block RAM也是分布在FPGA的不同位置,当构建一个FIFO使用的RAM太多时,会给布局布线带来很大的压力。所以建议实施的时候可以用多个中型的FIFO带代替一个大型的FIFO。

3. 不宜使用distributed RAM构建大位宽或者大深度的FIFO。

优化方向二:合理放宽时序约束

1. 当芯片设计中有多个时钟域时,对于那些通过FIFO隔开的时钟域之间,并不需要有太严格的约束。

2. 如果这些不相关的异步时钟是通过同一个MMCM产生的,如果不对这些异步时钟单独约束,那么按照软件的默认行为,这些异步时钟之间的路径是按同步路劲的分析方法进行分析的。这种默认行为的结果就是,一些不应该那么严格约束的路劲被过约束了。

3. 针对这种现象,一种可行的方案是:对同一个MMCM输出的多个异步时钟分别进行时序约束,并且只需约束两时钟域之间异步线路的最大布线延迟,而不需将异步线路中时序逻辑与LUT的响应时间纳入时序约束的范围。

4. Tip3中提及的时序约束方案的示例如下:

NET "CLKA" TNM_NET = "GRP_A";

NET "CLKB" TNM_NET = "GRP_B";

TIMESPEC TS_Path_A_B = FROM "GRP_A" TO "GRP_B" 5 ns DATAPATHONLY;

优化方向三:设置合理的实现工具属性

1. 尝试将synplify->Implementation option->Device->Enable advanced LUT combining属性关闭。

2. 尝试将ISE中Map Properties->Combinatorial logic optimization属性打开。

3. 尝试将ISE中Map Properties->Register duplication 属性打开。

4. 尝试将ISE中Map Properties->Allow logic optimization across hierarchy属性打开。

5. 尝试将ISE中Map Properties->LUT conbining属性关闭。

优化方向四:优化代码

1. 对于那些输出线扇出太大的寄存器,可以考虑在代码中手动复制。为避免复制的寄存器在综合阶段被优化掉,如果使用的是synplify综合工具,可在寄存器定义时使用综合指导属性/* synthesis syn_keep=1 */。

2. 不宜在一个寄存器前放置过多的组合逻辑,如果一个功能涉及的组合逻辑过于复杂,最好是将组合逻辑较均匀的分布在各个寄存器前面。