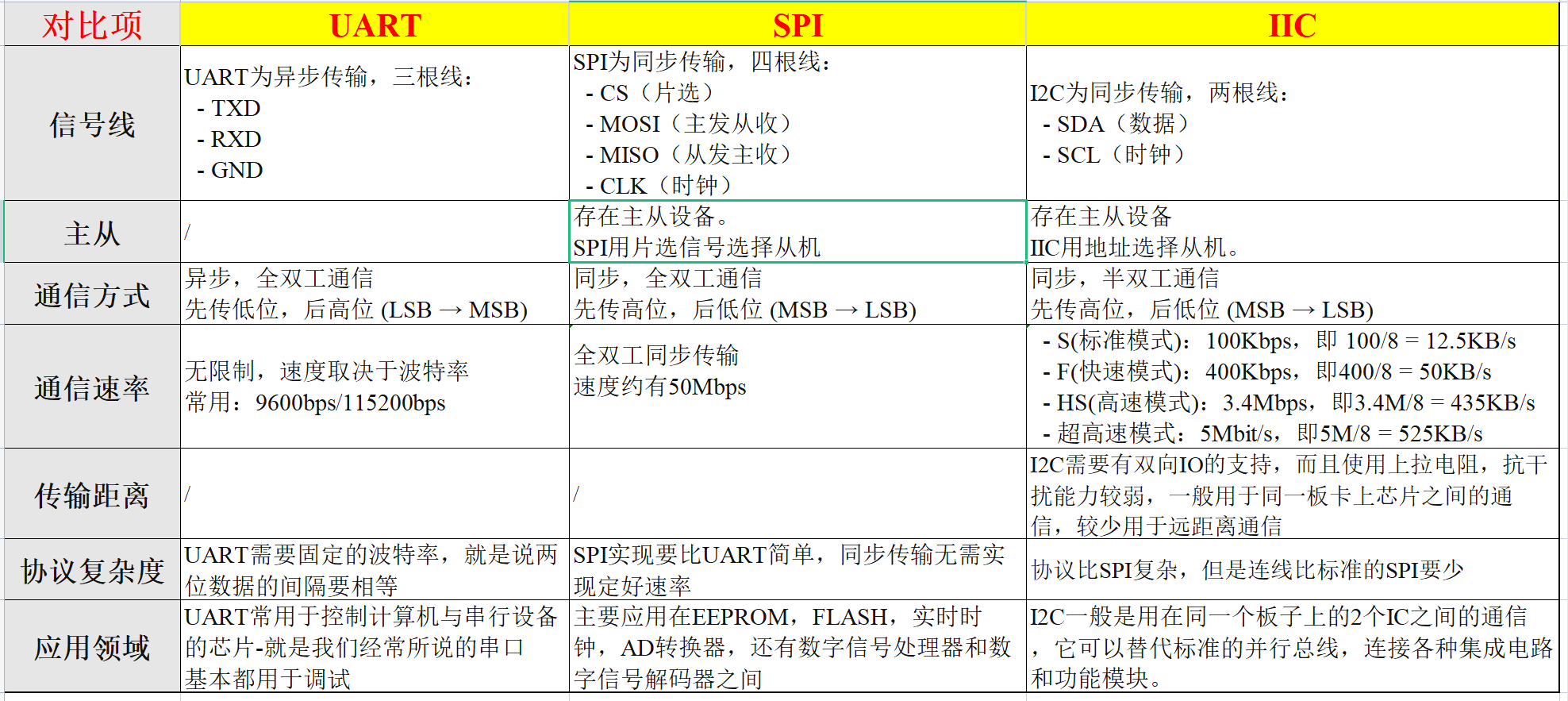

STM32 - UART、IIC、SPI通信协议

1. 基本概念

1.1 总线

详细可参考该Blog:https://zhuanlan.zhihu.com/p/425510158

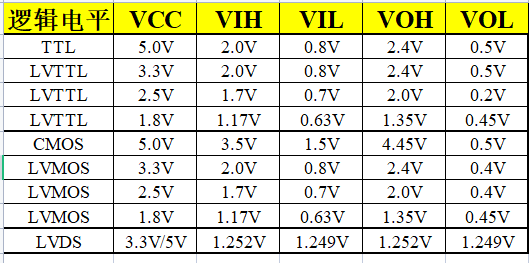

1.2 电平标准

常用的逻辑电平包括:TTL、CMOS、LVTTL、ECL、PECL、GTL;RS232、RS422、LVDS 等

- TTL按照典型电压可分为:5V、3.3V、2.5V、1.8V 系列

- CMOS按照典型电压可分为:5V、3.3V、2.5V、1.8V 系列

- 5V 为通用逻辑电平

- 3.3V、2.5V和1.8V称为低压逻辑电平,即 LVTTL (Low Voltage TTL)

- ECL/PECL和LVDS是差分输入输出

- RS-422/485和RS-232是串口的接口标准,RS-422/485是差分输入输出,RS-232是单端输入输出

1)TTL电平

TTL:(Transistor-Transistor Logic gate,晶体管-晶体管逻辑门),三极管结构,目前被广泛使用,其原因是:采用二进制来表示数据,而且规定 +5V表示逻辑 “1”; 0V表示逻辑“0”

TTL VS CMOS

1)TTL电路是电流控制器件,而coms电路是电压控制器件。

2)TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大;

COMS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。

无论TTL还是CMOS,都存在一个缺点:单线传输信号(Rx、Tx),很容易受到外界的干扰

如5V TTL,外界干扰当大于5V时候,会将高电平拉低

为此,我们可以采用两根线传输信号,取两者的差值。

2)差分电平

LVDS(Low Voltage Differential Signal)即低电压差分信号,LVDS接口又称RS644总线接口。

它的传输机制是把TTL逻辑电平转换成低电压差分信号,以便于高速传输

3)RS232

RS232:Recommended standard 推荐标准

严格来说,RS232/R485并不是通信协议,而是建立在串口通信UART基础上的电气接口.

其电平值如下:

- 逻辑1:-3~-15V

- 逻辑0:+3~+15V

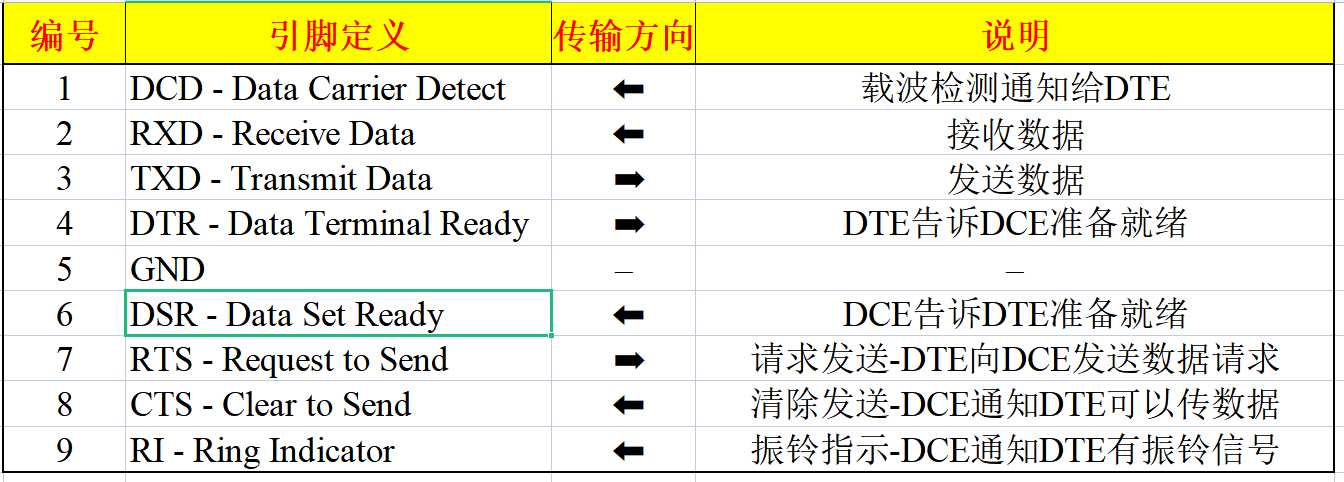

其接口形如下:

引脚定义如下:

1.3 通信方向

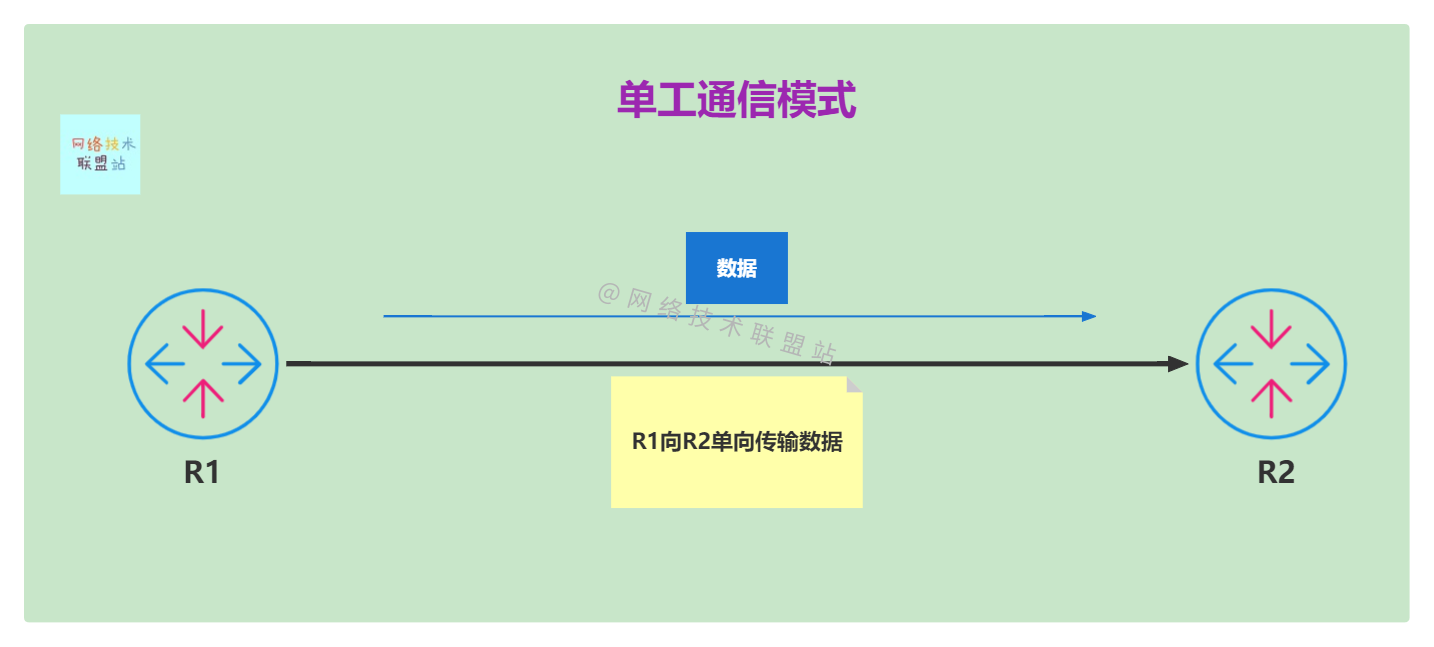

通信根据传输的方法分为单方向通信,即 单工;和双向通信,即双工.

- 单工:即数据传输只在一个方向上传输,方向是固定的,不能实现双向通信。比如收音机和广播。

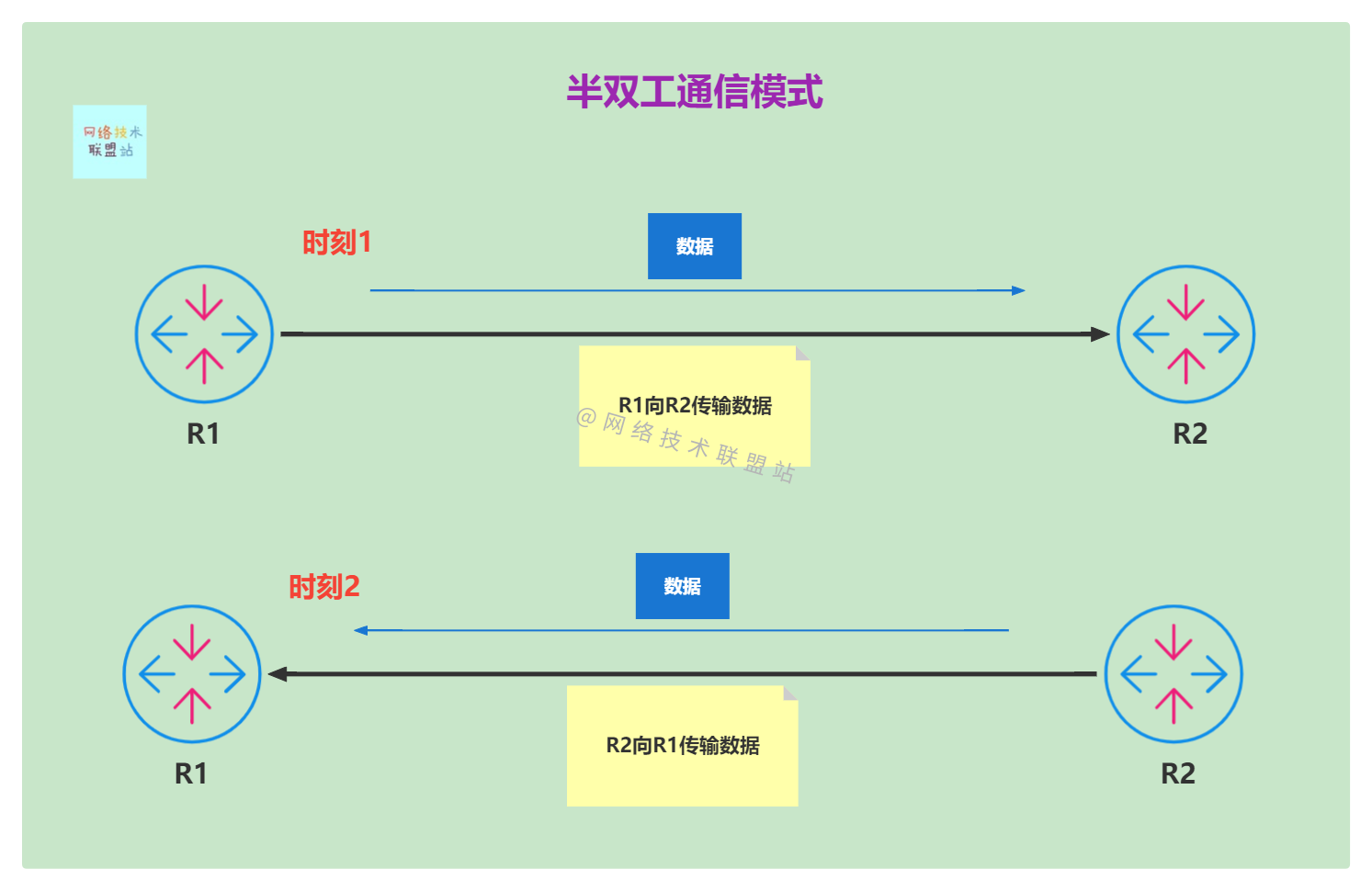

- 半双工:传输方向可以切换,允许数据在两个方向上传输。但是某个时刻,只允许数据在一个方向上传输,可以基本双向通信。

收发数据使用同一条线,比如单行道,根据时间切换行进的方向

RS485属于半双工通讯。

- 全双工:允许数据同时在两个方向传输,发送和接收完全独立,在发送的同时可以接收信号,或者在接收的同时可以发送。它要求发送和接收设备都要有独立的发送和接收能力。

收发各一条线,好比双车道。

比如RS232、RS422就属于全双工通讯。

c

1.4 串并行

- 串行就是数据是一位一位的发送

- 并行就是数据一组一组的发送

并行 VS 串行:

1)速率

并行总线由于是多个数据同时传输,需要考虑数据的协同性,这就导致了并行传输的频率不能做的很高

串行总线只有一条链路,就可以把频率做的很高,提高传输速度

2)抗干扰

并行总线两根相邻的链路其数据是同时传输的,这就会导致它们彼此之间会产生严重干扰,并行的链路越多,干扰越强;

并行的链路越多,干扰越强。因此并行总线需要加强抗干扰的能力,否则传输过程中数据就可能被损坏。如果传输过程中数据故障了,就需要重新对齐数据再传输

串行总线如果一个数据出错了,只需要重新传输一次就好了,由于串行总线频率高,很快就可以把错误数据重新传输过去

3)线路针脚

并行总线是多链路一块传输数据,就需要很多线,接口需要很多针脚

串行总线只需要很少的几个针脚即可

2. UART

UART:Universal Asynchronous Receiver-Transmitter, 通用异步收发器

- 串口:在

嵌入式里指的是UART口,常用TTL电平即3.3V或者5.0V;- COM口:在

台式机上常用的口,DB9那种接口,接口协议只有两种RS232和RS485;

UART口、COM口指的是物理接口形式;TTL、RS232和RS485指的是电平逻辑标准

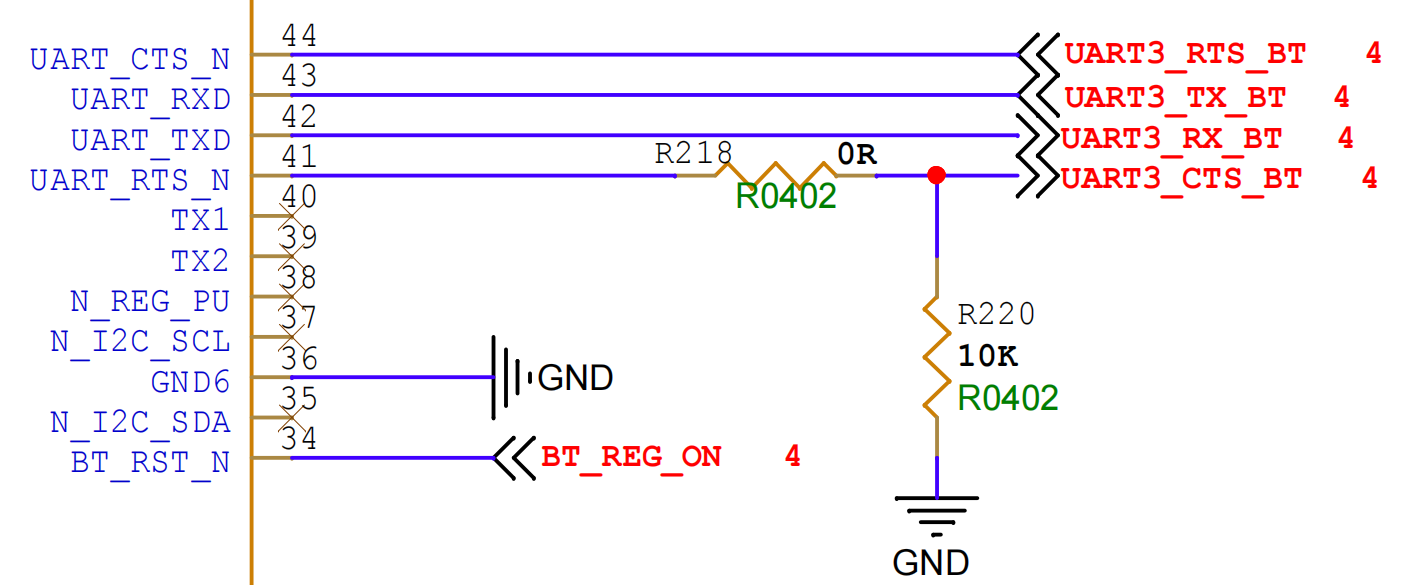

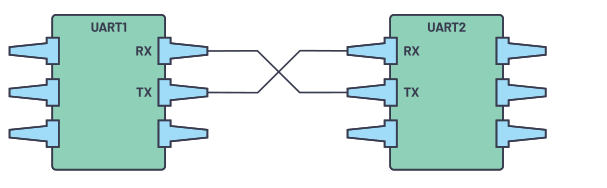

2.1 硬件结构

UART是串口总线,但无时钟信号,所以称为异步串行总线;

也正是由于其无时钟信号,使得收发双方无一个统一的时钟标准,以各自的时钟为准,为了防止偏移的累计误差,使得每次发送数据的位数不超过8bit

在嵌入式系统中,UART可用于板内通信(芯片和芯片间),也可用于板间通信,由于其结构简单、传输距离相对长,因此被广泛使用;

1)板内通信

接线方式为:A---------B

- TX --> RX

- RX <-- TX

- RTS ---> CTS

- CTS <--- RTS

CTS/RTS用于硬流控,协调双方收发,保证数据不丢失

芯片A通过UART发送数据,当芯片B拉高RTS时,A就会暂停发送,当芯片B拉低RTS时,A又会继续发送。

2)板间通信

板间通信一般情况下只用 Rx、Tx、GND 三条线

注意:板间通信时必须接上GND

2.2 通信协议

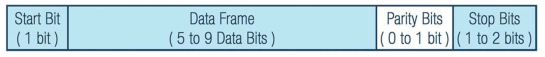

UART因为是串行总线,数据是一位一位的传输,其通信协议格式如下:

数据包由起始位、数据帧、奇偶校验位和停止位组成。

- 起始位:空闲时处于高电平,当开始发送数据时,发出逻辑‘0’的信号,表示开始传输数据

- 数据位:紧随起始位,位数一般是5-8bit,最低位优先发送

- 奇偶校验位:检验数据位中‘1’的个数为奇数(奇校验为1,偶检验为0)/偶数(奇校验为0,偶检验为1),一般不使用该校验

- 停止位:表示数据传输结束,电平变为高,由1-2bit组成,通常使用1bit

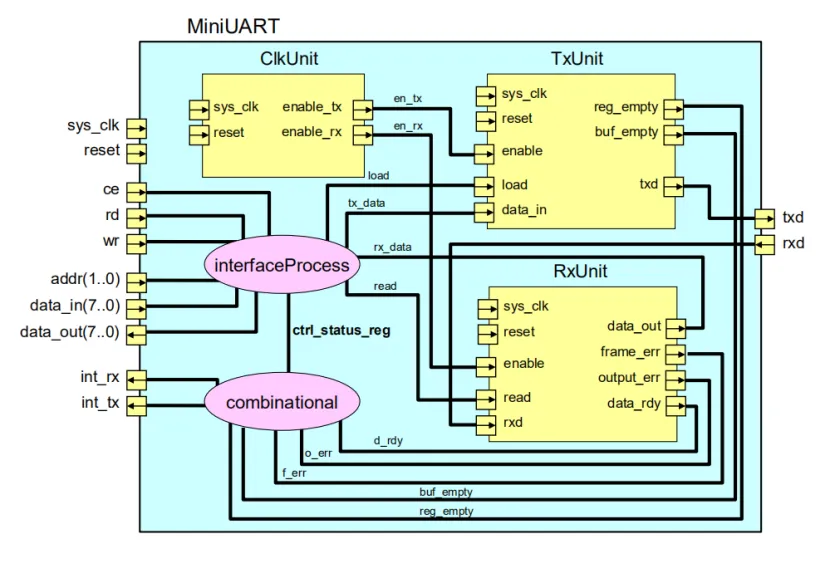

2.3 工作流程

UART一般具备:发送/接收缓冲区,发送/接收移位寄存器。

- 发送/接收缓冲区:用于缓存发送/接收的数据,通常为FIFO(First In First Out)

- 发送/接收移位寄存器:将发送/接收的数据按位排列后(先低位后高位),开始发送/接收

数据传输流程

-

发送数据之前,收发双方必须协商好发送的波特率,帧格式,否则无法完成数据的正确接收。

-

发送设备上的 UART从 CPU(微处理器或微控制器)接收并行数据,并将其放入到缓冲区中

-

UART把缓冲区中的数据,放到移位寄存器中,即:将并行数据转换为串行数据

-

该串行数据被传输到接收设备上的 UART

-

接收 UART 在接收到串行数据后,将其转换回并行数据(通过接收移位寄存器)

-

将数据放置到缓冲区中,提供给 CPU。

3. IIC

如果不想看文字,可直接看 IIC的B站视频

IIC(Inter-Integrated Circuit)总线,开发公司NXP(被Philips收购),两线式的串行总线,用于连接微控制器和其外围设备。

半双工传输方式,即发送时不能接收,接收时不能发送!

传输距离较短,速率可达到400Kbps左右。

由于其结构简单,被广泛使用在CPU和IC、IC和IC连接上。

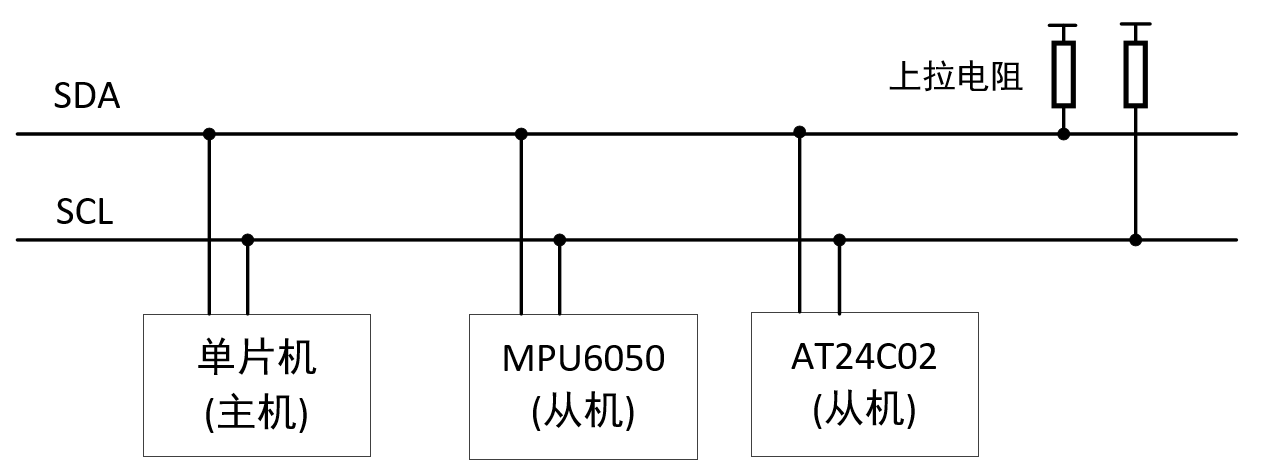

3.1 硬件链接

IIC通信线只有只有 · 两根:

- 数据线SDA:高低电平传输二进制数据

- 时钟线SCL:通过方波信号提供时钟节拍

IIC上可以挂载多个设备,每个设备都可以作为主机,也可以作为从机(但一般MCU/CPU作为主机),IIC支持多个主控。

每个设备都具备自己的器件地址,地址通常在IC出厂时已经被厂家固定了,使用者不可更改(类似于MAC地址);少数IC厂商固定了前几位的厂商地址,留给用户定义剩余的地址。

一个主控能够控制信号的传输和时钟频率。当然,在任何时间点上只能有一个主控。

使用IIC通信的IC器件有很多,如:陀螺仪、IMU、EEPROM存储等,通过IIC总线,可以与单片机之间进行数据传输。

3.2 通信流程

3.2.1 名词解释

在介绍通信流程前,我们必须明确几个名词术语

1)主机、从机

主机:负责整个系统的任务协调与分配,一般为CPU或MCU

从机:通过接收主机的指令从而完成某些特定的任务

发送端:发送数据的IC器件,注意,发送端不一定为主机

接收端:接收数据的IC器件

2)信号类型

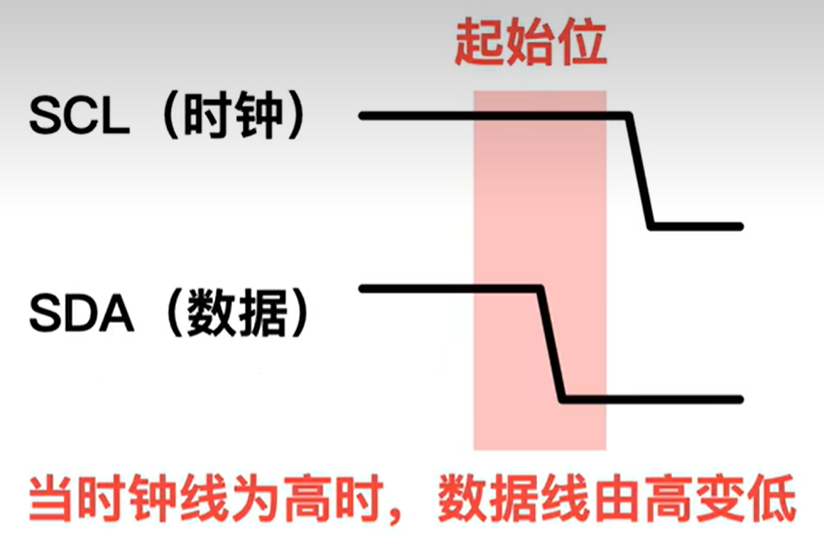

空闲状态:SDA和SCL同时为高时,为IIC总线的

空闲状态起始信号:SCL 为高电平时,SDA 由高电平向低电平跳变,开始传送数据。

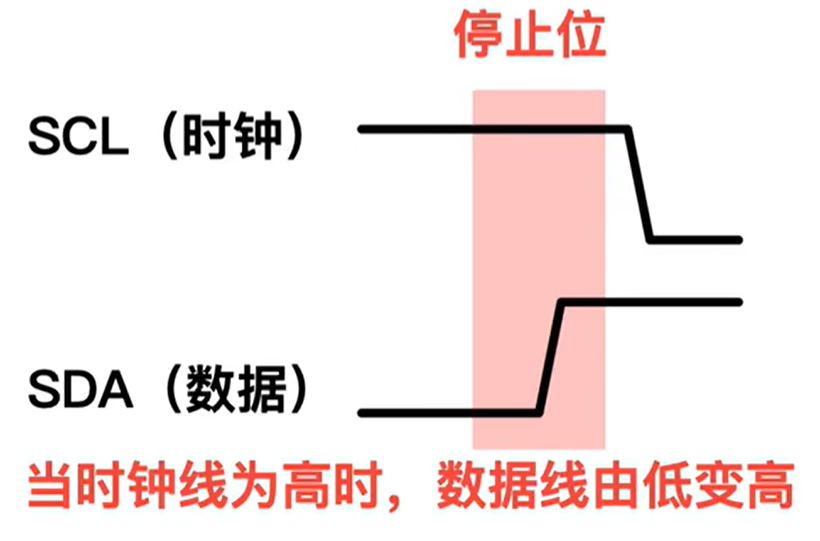

停止信号:SCL 为高电平时,SDA 由低电平向高电平跳变,结束传送数据。

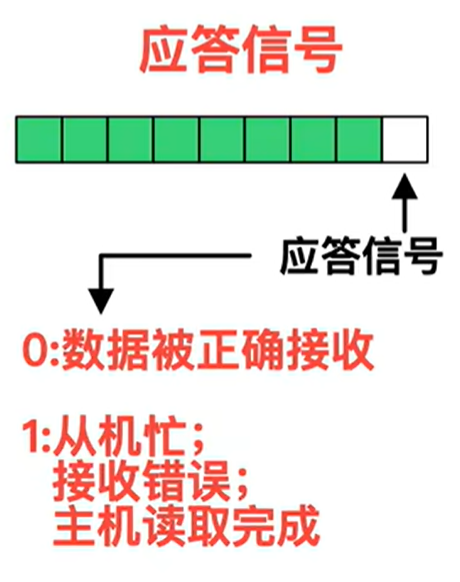

应答信号:接收数据的 IC 在接收到 8bit 数据后,向发送数据的 IC 发出特定的低电平脉冲,表示已收到数据

接收端收到有效数据后向对方响应的信号,发送端每发送一个字节(8位)数据,在第9个时钟周期释放数据线去接收对方的应答。

- 当SDA是低电平为有效应答(ACK),表示对方接收成功;

- 当SDA是高电平为无效应答(NACK),表示对方没有接收成功(可能原因为从机忙/接收错误等)。

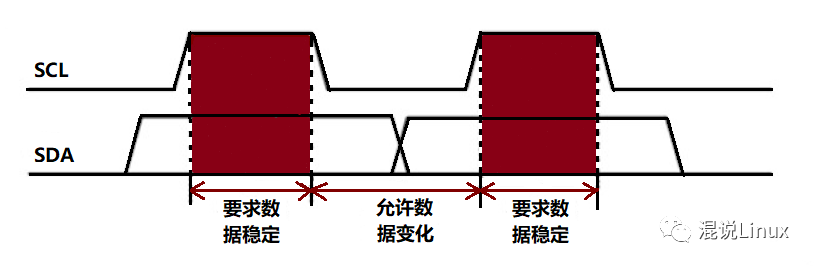

3.2.2 数据有效性

I2C总线进行数据传送时,在SCL的每个时钟脉冲期间传输一个数据位

时钟信号SCL为高电平期间,数据线SDA上的数据必须保持稳定

只有在时钟线SCL上的信号为低电平期间,数据线SDA上的高电平或低电平状态才允许变化

因为当SCL是高电平时,数据线SDA的变化被规定为控制命令(START或STOP,也就是前面的起始信号和停止信号)

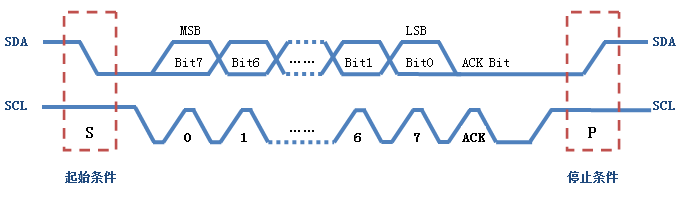

3.2.3 工作流程

1)注意事项

注意事项:

-

SDA线上的数据在SCL时钟“高”期间必须是稳定的

-

只有当SCL线上的时钟信号为低时,数据线上的“高”或“低”状态才可以改变

-

输出到SDA线上的每个字节必须是8位

-

数据传送时,先传送最高位(MSB)

-

每一个被传送的字节后面都必须跟随一位应答位(即一帧共有9位)。

当一个字节按数据位从高位到低位的顺序传输完后,紧接着从设备将拉低SDA线,回传给主设备一个应答位ACK, 此时才认为一个字节真正的被传输完成

如果一段时间内没有收到从机的应答信号,则停止发送,结束本次通信。

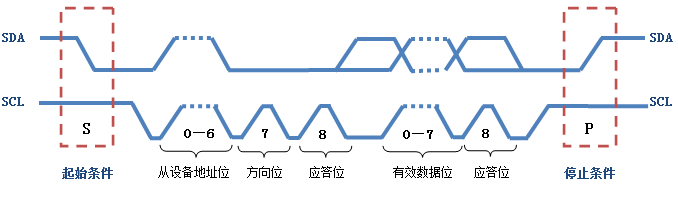

2)发送数据

- IIC的IC设备的地址一般为

7位八位设备地址 = 7位从机地址 + 方向(0:write;1:Read)

- IIC每帧数据由

9 bit组成如果是

发送数据,则包含 8bit数据+1bit ACK,

如果是设备地址数据,则8bit包含7bit设备地址 1bit方向

主机向从机写数据流程:

主机首先产生START信号

发送一个从机地址,这个地址共有7位,第8位是数据方向位(R/W),0表示主机发送数据(写),1表示主机接收数据(读)

主机发送地址时,总线上的每个从机都将这7位地址码与自己的地址进行比较,若相同,则认为自己正在被主机寻址

主机等待从机的应答信号(A)

主机接收到应答:发送欲写入的寄存器地址(8bit),并等待从机应答

- 当主机收到应答信号时,发送N个字节的数据,继续等待从机的N次应答信号

- 当主机未收到应答信号,说明接收端未收到数据(地址不存在或设备忙)或者无法解析该数据,由master决定来如何处理(stop 或者 repeat send)

- 主机产生停止信号,结束传送过程。

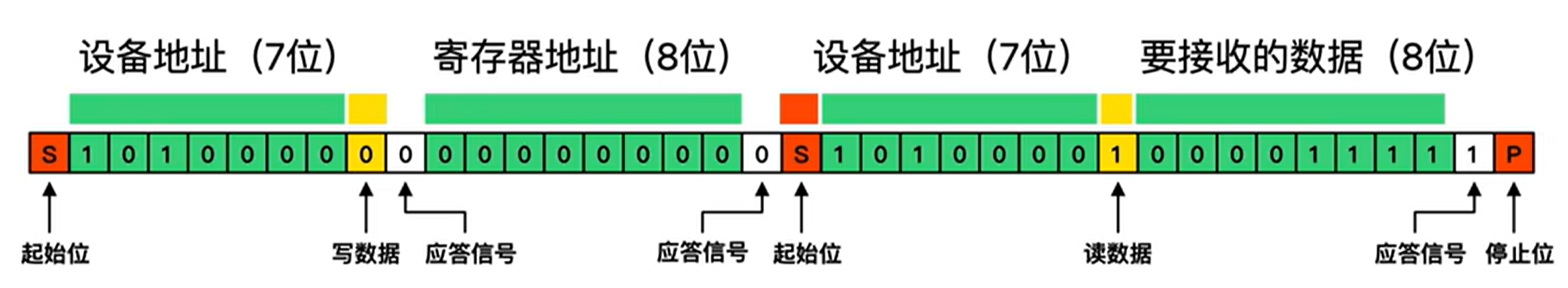

3)接收数据

主机读数据流程:

主机首先产生START信号

主机发送一个从机地址,注意此时该地址的第8位为0,因为后面一帧要写寄存器地址,这时候主机等待从机的应答信号(ACK)

当主机收到应答信号时,写欲读取的寄存器地址(8bit)

当收到应答时,再次发送一个起始信号

再次发送从机地址,注意此时第8位为1,表示读取数据

等待从机响应

开始发送数据,每8bit数据一组,每组都需要接收方的应答信号

当接收完成后,主机若不应答,表示不在接收数据;否则应答后继续接收数据

接收完成后,主机进产生停止信号,结束传送过程。

4. SPI

如果不想看文字,可直接看 SPI的B站视频

SPI(Serial Peripheral interface,串行外围设备接口),是美国摩托罗拉公司(Motorola)最先推出的一种同步串行传输规范。它是一种单片机外设芯片串行扩展接口,是一种 高速、全双工、同步通信 总线,主要应用在 EEPROM、FLASH、RTC,ADC/DAC,DSP等设备之间.

4.1 组成结构

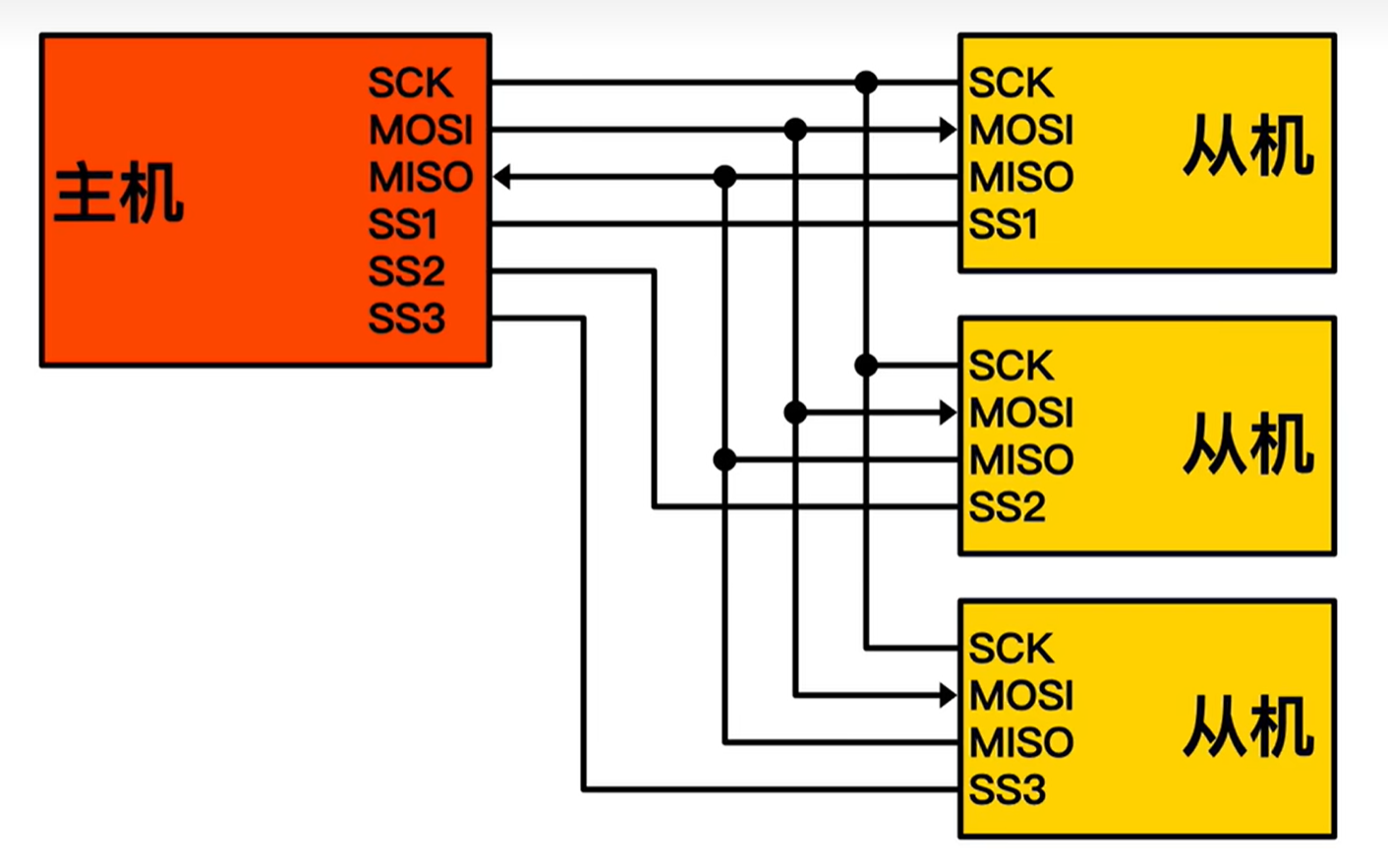

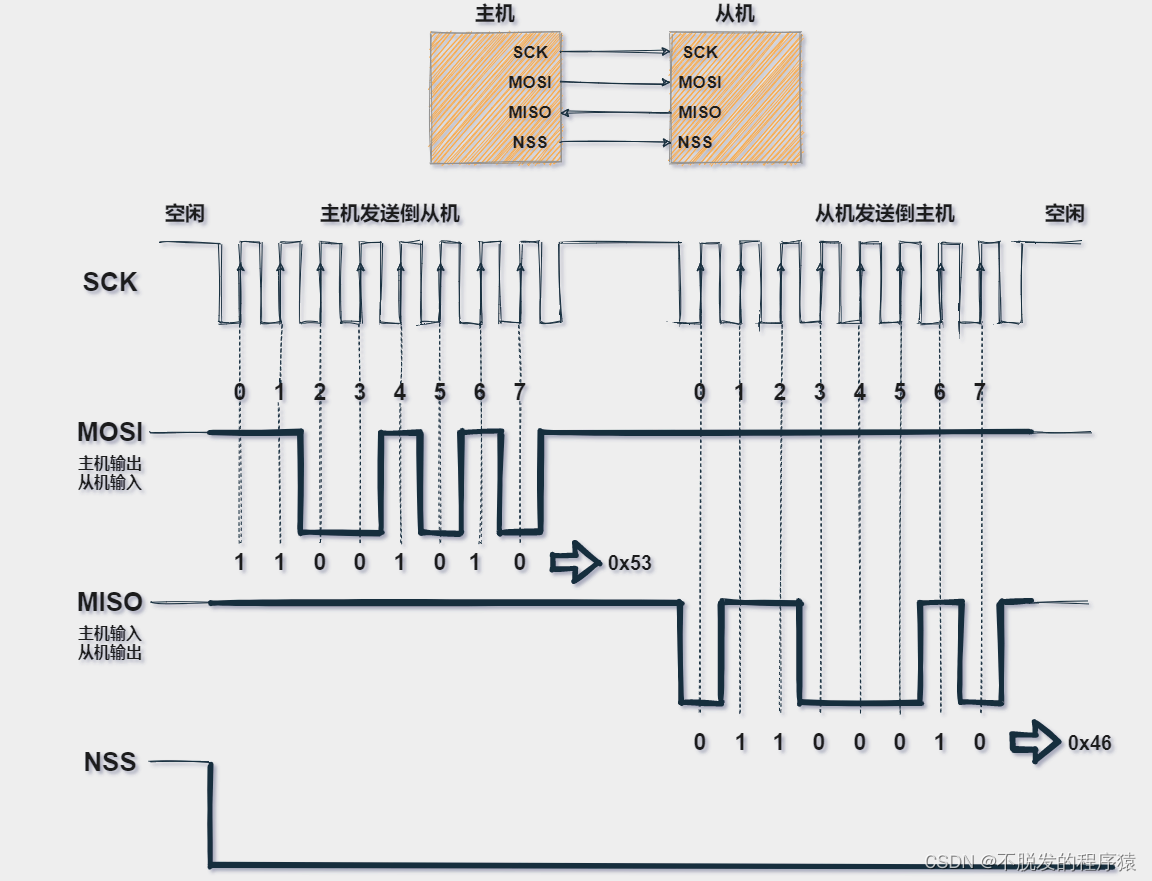

SPI有主、从两种模式,通常由一个主模块和一个或多个从模块组成(SPI不支持多主机). 主模块选择一个从模块进行同步通信,从而完成数据的交换。提供时钟的为主设备(Master),接收时钟的设备为从设备(Slave),SPI接口的读写操作,都是由主设备发起,当存在多个从设备时,通过各自的片选信号进行管理。

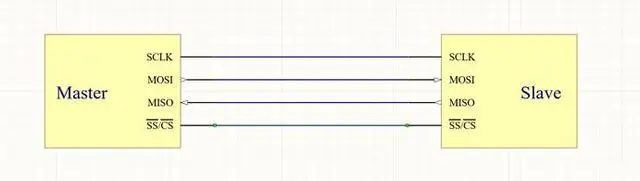

一主一从连接

一主多从连接

SPI由四根线组成:

- MISO( Master Input Slave Output):主设备数据输入,从设备数据输出;

- MOSI(Master Output Slave Input):主设备数据输出,从设备数据输入;

- SCLK(Serial Clock):时钟信号,由主设备产生;

- CS/SS(Chip Select/Slave Select):从设备使能信号,由主设备控制,一主多从时,CS/SS是从芯片是否被主芯片选中的控制信号,只有片选信号为预先规定的使能信号时(高电位或低电位),主芯片对此从芯片的操作才有效

4.2 通信过程

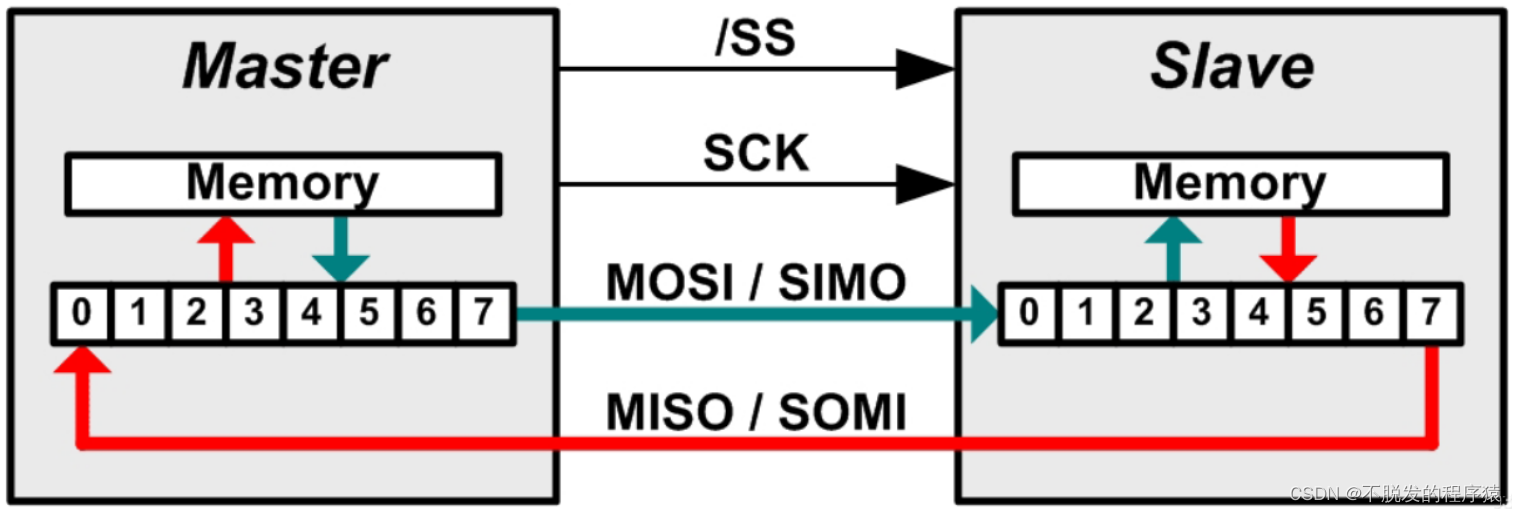

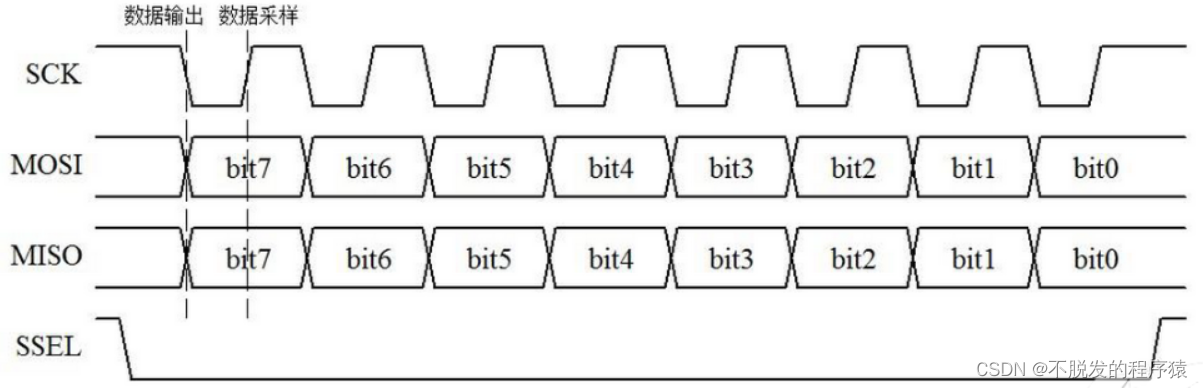

SPI主设备和从设备都有一个 串行移位寄存器,主设备通过向它的SPI串行寄存器写入一个字节来发起一次传输。

SPI数据通信的流程可以分为以下几步:

-

1、主设备发起信号,将CS/SS拉低(一般芯片的片选都是低电平有效,具体还要看slave的芯片手册),启动通信。

-

2、主设备通过发送时钟信号,来告诉从设备进行写数据或者读数据操作(采集时机可能是时钟信号的上升沿或下降沿。

-

3、主机(Master)将要发送的数据写到发送数据缓存区(Menory),缓存区经过移位寄存器(缓存长度不一定,看单片机配置),串行移位寄存器通过MOSI信号线将字节一位一位的移出去传送给从机,同时MISO接口接收到的数据经过移位寄存器一位一位的移到接收缓存区。

-

4、从机(Slave)也将自己的串行移位寄存器(缓存长度不一定,看单片机配置)中的内容通过MISO信号线返回给主机。同时通过MOSI信号线接收主机发送的数据,这样,两个移位寄存器中的内容就被交换。

看文字太枯燥,举个栗子:

4.2.1 设备选择

- 当SPI主设备读/写从设备时,它首先拉低从设备对应的SS线(注意,SS只有主设备可以操控)。

- 接着开始发送工作脉冲到时钟线上,

- 在相应的脉冲时间上,主设备把信号发到MOSI实现“写”,同时可对MISO采样而实现“读”。

数据的发送和接收,都是从最高位MSB → 最低位LSB

4.2.2 设备时钟

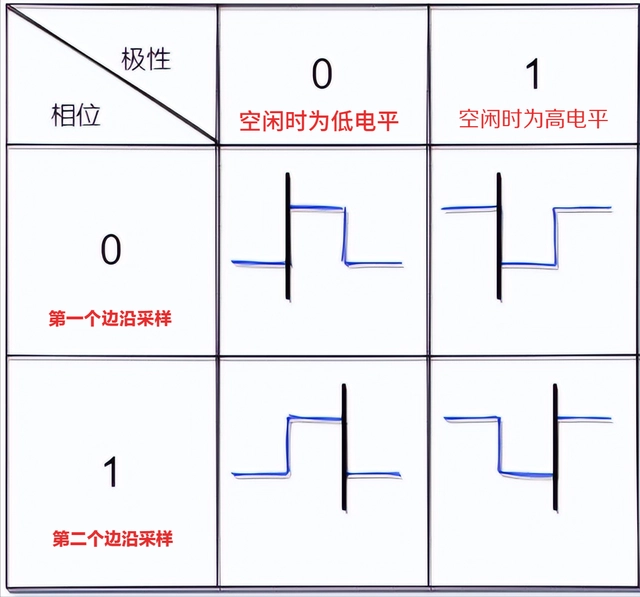

SPI时钟特点主要包括:时钟速率、时钟极性和时钟相位三方面。

1)时钟频率

SPI总线上的主设备必须在通信开始时候配置并生成相应的时钟信号。

理论上讲,时钟频率可以无限大,但受限于主控所能提供的最大时钟频率(晶振的频率都是有限的)和SPI所能承受的最大传输速率。

2)时钟极性

时钟极性通常写为CKP或CPOL。

时钟极性和相位共同决定读取数据的方式,比如信号上升沿读取数据还是信号下降沿读取数据。

CKP可以配置为1或0。这意味着你可以根据需要将时钟的默认状态(IDLE)设置为高或低。极性反转可以通过简单的逻辑逆变器实现。你必须参考设备的数据手册才能正确设置CKP和CKE。

- CKP = 0:时钟空闲IDLE为低电平 0;

- CKP = 1:时钟空闲IDLE为高电平1。

3)时钟相位

时钟相位通常写为CKE或CPHA。顾名思义,时钟相位/边沿,也就是采集数据时是在时钟信号的具体相位或者边沿;

- CKE = 0:在时钟信号SCK的第一个跳变沿采样;

- CKE = 1:在时钟信号SCK的第二个跳变沿采样。

4.2.3 四种模式

根据SPI的时钟极性和时钟相位特性可以设置4种不同的SPI通信操作模式,它们的区别是定义了在时钟脉冲的哪条边沿转换(toggles)输出信号,哪条边沿采样输入信号,还有时钟脉冲的稳定电平值(就是时钟信号无效时是高还是低),详情如下所示:

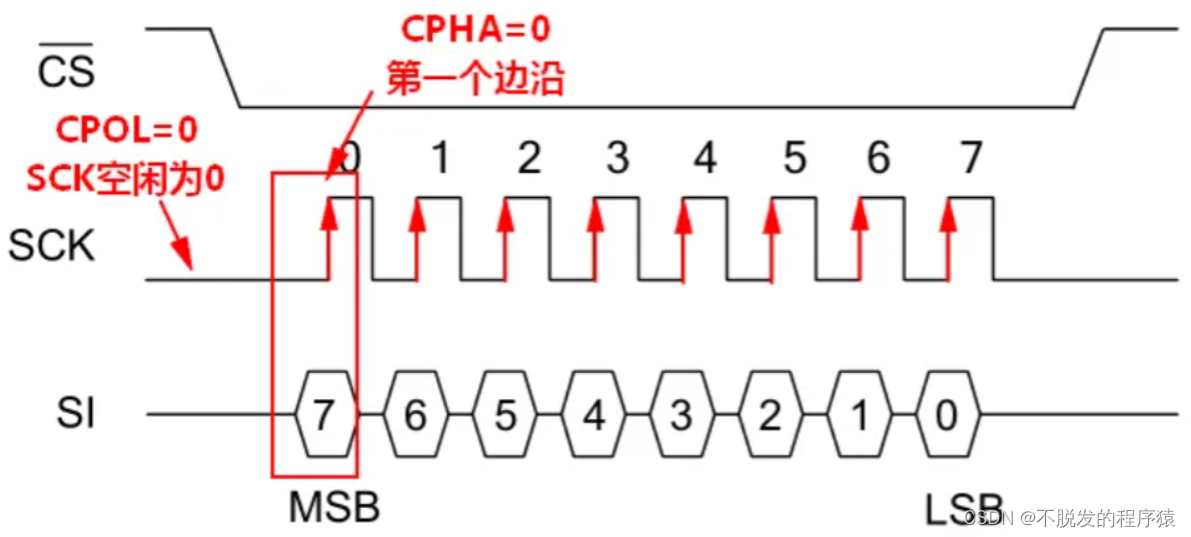

-

Mode0:CKP=0,CKE =0:当空闲态时,SCK处于低电平,数据采样是在第1个边沿,也就是SCK由低电平到高电平的跳变,所以数据采样是在上升沿(准备数据),(发送数据)数据发送是在下降沿。

-

Mode1:CKP=0,CKE=1:当空闲态时,SCK处于低电平,数据发送是在第2个边沿,也就是SCK由低电平到高电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿。

-

Mode2:CKP=1,CKE=0:当空闲态时,SCK处于高电平,数据采集是在第1个边沿,也就是SCK由高电平到低电平的跳变,所以数据采集是在下降沿,数据发送是在上升沿。

-

Mode3:CKP=1,CKE=1:当空闲态时,SCK处于高电平,数据发送是在第2个边沿,也就是SCK由高电平到低电平的跳变,所以数据采集是在上升沿,数据发送是在下降沿。

举个例子,下图是SPI Mode0读/写时序,可以看出SCK空闲状态为低电平,主机数据在第一个跳变沿被从机采样,数据输出同理。

4.3 SPI优缺点

- 优点

-

无起始位和停止位,因此数据位可以连续传输而不会被中断;

-

没有像I2C这样复杂的从设备寻址系统;

-

数据传输速率比I2C更高(几乎快两倍);

-

分离的MISO和MOSI信号线,因此可以同时发送和接收数据;

-

极其灵活的数据传输,不限于8位,它可以是任意大小的字;

-

非常简单的硬件结构。从站不需要唯一地址(与I2C不同)。从机使用主机时钟,不需要精密时钟振荡器/晶振(与UART不同)。不需要收发器(与CAN不同)。

- 缺点

-

使用四根信号线(I2C和UART使用两根信号线);

-

无法确认是否已成功接收数据(I2C拥有此功能);

-

没有任何形式的错误检查,如UART中的奇偶校验位;

-

只允许一个主设备;

-

没有硬件从机应答信号(主机可能在不知情的情况下无处发送);

-

没有定义硬件级别的错误检查协议;

-

与RS-232和CAN总线相比,只能支持非常短的距离;

5. UART、SPI、IIC 对比

浙公网安备 33010602011771号

浙公网安备 33010602011771号