【FPGA基础】时钟设计与异步复位同步撤离设计

一、时钟设计

1、时钟分频设计

累加器时钟分频(32分频)

always @(posedge clk and negedge rst_n) begin if (!rst_n) clk_cnt <= 5'b0; else clk_cnt <= clk_cnt + 1'b1; end

异步时钟分频(32分频)

always @(posedge clk ) clk_2 <= ~clk_2; always @(posedge clk_2 ) clk_4 <= ~clk_4;

推荐采用异步时钟分频结构,防止毛刺产生,面积小不需要复位;

(注:当然最好还是用clk_wizard产生时钟,尽量避免自己分频)

二、复位设计

1、同步复位设计

同步复位就是指复位信号只有在时钟上升沿到来时才有效,否则无法完成对系统的复位工作。用Verilog描述如下:

always @(posedge clk ) begin if (!rst_n) …… end

(1)同步复位的优点:

a.有利于仿真器的仿真;

b.可以使所设计的系统成为100%的同步时序电路,这便大大有利于时序分析,而且综合出来的fmax一般较高;

c.因为它只有在时钟有效电平到来时才有效,所以可以滤除高于时钟频率的毛刺。

(2)同步复位的缺点

a.复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位。同时还要考虑,诸如:clk skew,组合逻辑路径延时,复位延时等因素;

b.由于大多数的逻辑器件的目标库内的DFF(DFF捕获时钟上升沿的D端数据,并在Q端输出,一直维持到下一时钟上升沿到来之前。在此期间,D端的数据变化不会直接影响到Q端的输出)都只有异步复位端口,所以倘若采用同步复位的话,综合器就会在寄存器的数据输入端口插入组合逻辑,这样会耗费较多的逻辑资源。

2、异步复位设计

异步复位:指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。用Verilog描述如下:

always @(posedge clk or negedge rst_n) begin if (!rst_n) …… else …… end

(1)异步复位的优点:

a.大多数目标器件库的DFF都有异步复位端口,因此采用异步复位可以节省资源;

b.设计相对简单;

c.异步复位信号识别方便,而且可以很方便的使用FPGA的全局复位端口。

(2)异步复位的缺点

a.在复位信号释放(release,也就是复位信号无效的时候)的时候容易出现问题,倘若复位释放时恰恰在时钟有效沿附近,就很容易使电路处于亚稳态;

b.复位信号容易受到毛刺的影响。

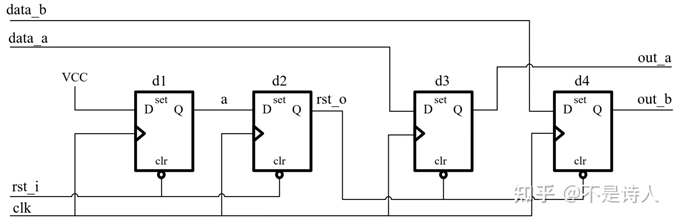

3、异步复位同步撤离设计

用verilog描述如下:

always @(posedge clk or negedge arst_n) begin if (!arst_n) {rst_n, rff1} <= 2'b0; else {rst_n, rff1} <= {rff1, 1'b1}; end always @(posedge clk or negedge rst_n) begin if (!rst_n) …… else …… end

推荐设计中使用这种复位设计,结合了双方面的优点,很好的克服了异步复位的缺点,因为异步复位的问题主要出现在复位信号释放的时候。倘若异步复位信号有效的话,触发器就会复位,从而复位后级寄存器;但是又因为这属于时钟沿触发,当复位信号释放时,触发器的输出要延迟一个时钟周期才能恢复成1,因此使得复位信号的释放与时钟沿同步化。

这种复位方式,既可以防止后级寄存器无法满足恢复时间要求,也可以避免前级寄存器无法满足恢复时间要求,还能捕捉持续时间小于一个时钟周期的复位信号。但要注意的是,虽然复位不依赖输出,但是复位输出信号需要依赖于时钟才能撤离,即在上电复位或者门控时钟电路里,当电路中没有正常工作的时钟时,该复位电路无法工作。

浙公网安备 33010602011771号

浙公网安备 33010602011771号