【Implementation】Vivado实现参数设置

实现(Implementation)是FPGA设计中至关重要的环节之一。implementation是一个place和route的过程,也就是布局布线 。综合后生成的门级网表只是表示了门与门之间虚拟的连接关系,并没有规定每个门的位置以及连线的长度等。 布局布线就是一个将门级网表中的门的位置以及连线信息确定下来的过程。

一、Vivado布线概述

Vivado布线是在FPGA设计中实现物理布局的关键步骤之一。这一步骤不仅可以对综合后生成的网表进行逻辑综合优化,还可以进行针对特定设计的功率和物理综合设计进行优化。最终目标是建立一个符合设计要求的物理布局,同时最小化电路的时钟周期延迟和功耗消耗。

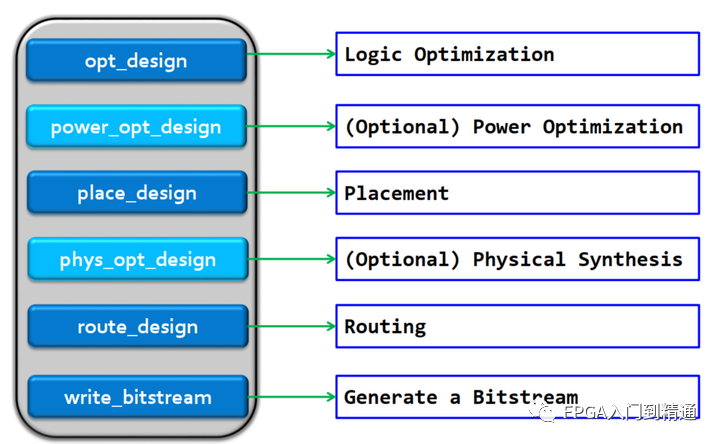

主要布线步骤如下:

说明:

opt_design:逻辑优化;

power_opt_design:可选,电源优化。

place_design:布局设计。

phys_opt_design:可选,物理综合优化。

route_design:布线设计。

write_bitstream:生成bit文件。

二、布线参数设置

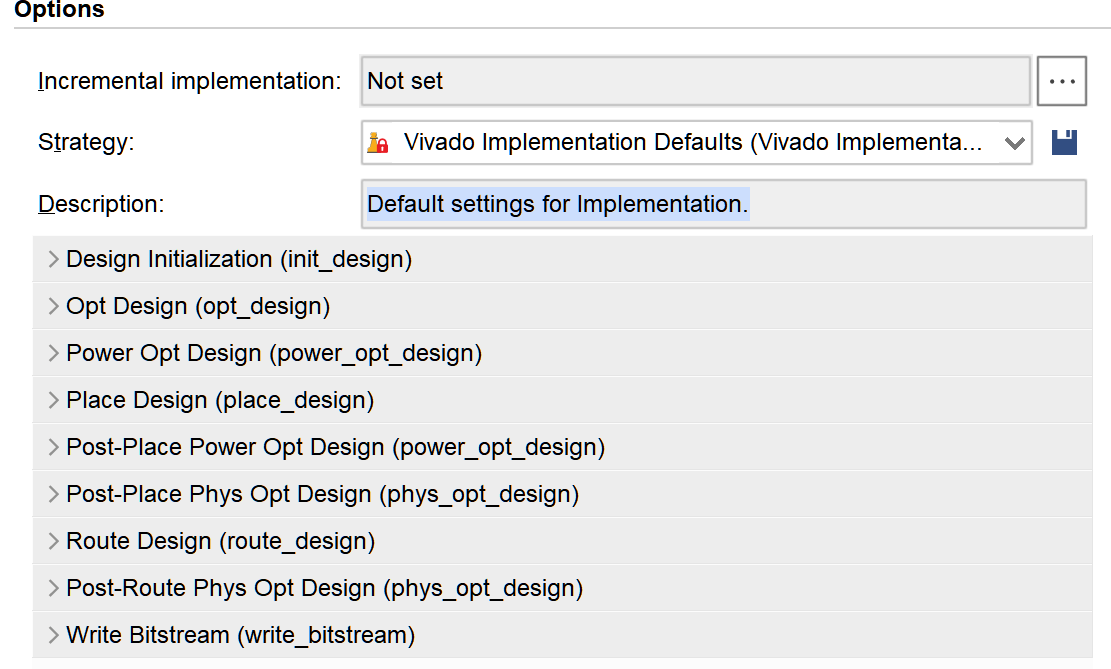

在设置界面中,可以选择指定的约束文件、综合策略,如下图所示:

1、Incremental implementation

增量编译设置,可以选择加载上一版本布线后DCP文件,优化编译速度。

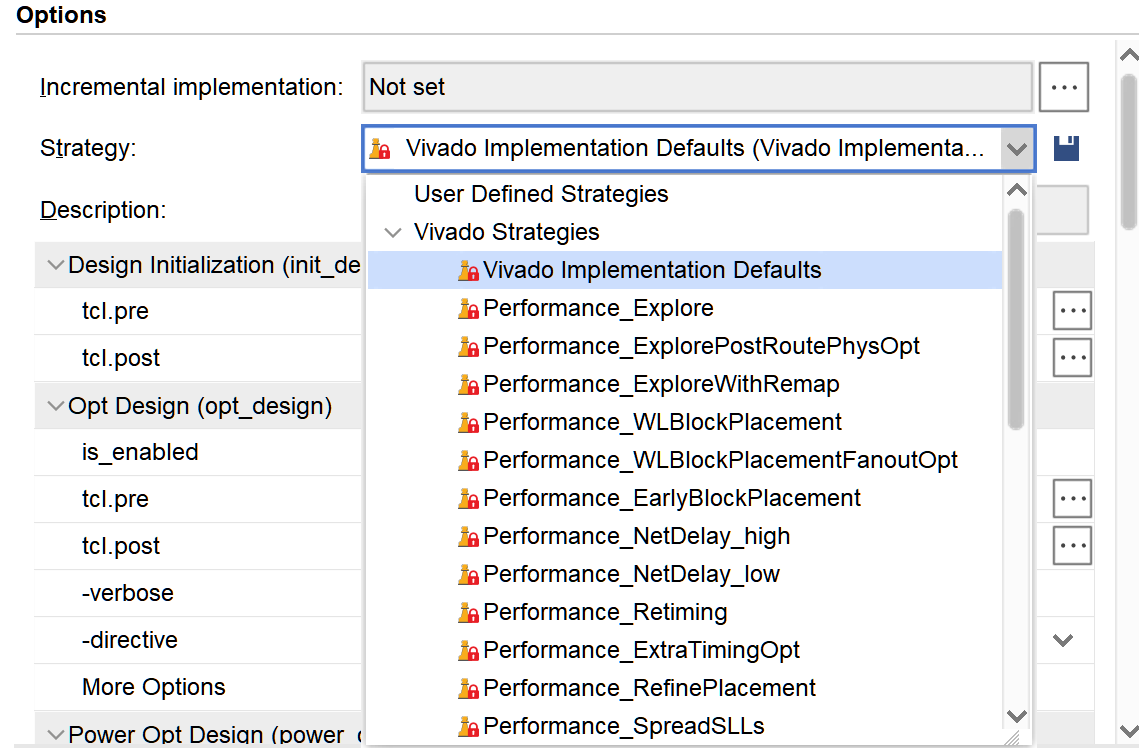

2、Startegy

布线策略选择,根据实际需要来选择,一般选用默认配置即可。

3、参数设置说明

(1)directive与strategy

directive:是指定某一阶段的指令,用于设定某一阶段的优化策略和实现方法。

strategy:是为了整个工程的实现指标,而运行了一系列的directive,算是各阶段directive指定好的策略合集。

(2)tcl.pre和tcl.post

可选择加载TCL文件,用于在布线前和布线后执行的逻辑。

三、设置Vivado压缩BIT文件

Vivado 生成bit文件可以设定是否压缩,这样可以降低flash存储空间的占用

1、添加约束的方法

在XDC约束文件中,添加这个约束即可:

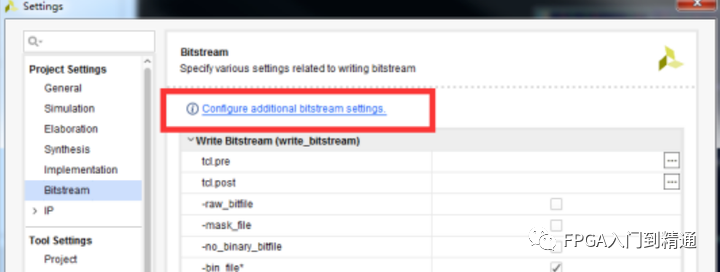

2、设置生成bit操作的参数

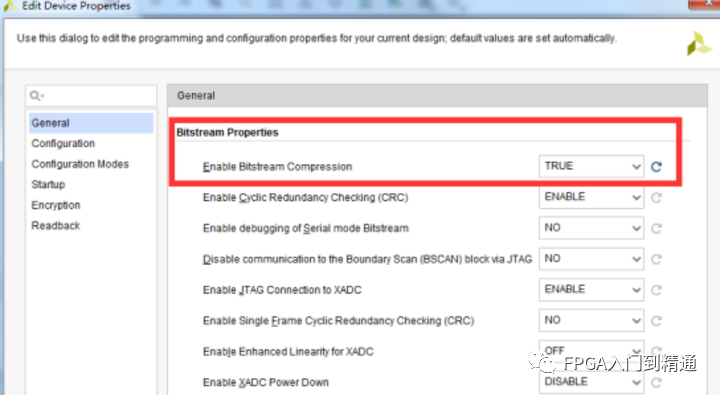

在打开implementation design后,打开settings界面,选择bitstream,点开“Configure additional bitstream settings”

将压缩BIT文件的选项设置为True即可

浙公网安备 33010602011771号

浙公网安备 33010602011771号