【嵌入式通信】嵌入式通信的底层逻辑

本文主要是对B站视频【蛋饼嵌入式】嵌入式通信的底层逻辑 的总结,视频内容帮我进一步认识了几个问题:同步通信和异步通信的区别、DDR、NRZ编码的意义等。

0、计算机网络通信框架

ISO国际标准化组织在上世界70年代末,把计算机网络通信的整个框架描述成了一个七层的模型,称之为OSI开放系统互联模型:

我们最能直观感受到的通信方式的区别,诸如通信的速率,电平范围,用几根线,同轴还是双绞线,这些都体现在最下面的物理层。

而如何把物理线路上的比特流正确的切分,并识别出一帧数据内部的结构,则属于数据链路层。

1、嵌入式通信方式

一根线:最多半双工,单方向通信。

两根线:全双工,已经是UART的雏形了。还要加上一些标记信号位,来实现正确解析出一帧数据。

除了数据线外,再加一条时钟线来传输时钟,接收方就根据时钟来采样,这就是同步通信(IIC、SPI,分为半双工和全双工)

提高通信的距离、稳定性:

双绞线代替同轴电缆。常见的百兆以太网100BASETX用2对4根,千兆1000BASETX用到4对8根,车载以太网100BASE-T1则只用一对。这种情况下,如果还保留同步通信,带上时钟线的话,就还要再准备一对双绞线,所以往往去掉时钟线,回归异步通信。

然而对于以太网这种速率达到百兆、千兆,和其他需要应对远距离传输需求的serdes通信而言,单纯靠两边约定好的速率(异步通信)是无法保证采样的可靠性的。

可以通过已经存在的数据线,来恢复时钟信号。首先思考一个问题,时钟的本质是什么。通俗意义上的时钟可以看做是周期性的方波,而对于采样电路中的触发器而言,实际上需要的是方波中的边沿。实际上数据线中也含有边沿,但是不那么规律。如果我们刻意地通过编码改造数据,让边沿变多,就有可能恢复周期固定的时钟。接收方再由这个恢复出来的时钟作采样,就可靠的多了。这涉及到CDR,时钟恢复电路的设计,具体可以再查资料。

如果连续的电平过多时,也就是数据的跳变沿过少时,会导致锁相环失锁,后端输出的时钟也就无法稳定了。

为了产生足够多的边沿,就引出了类似于曼彻斯特编码、4B/5B、8B/10B等的编码技术。当然减少直流分量,降低传输过程中的电容损耗也是引入新编码方式的一大原因。Serdes一般也会结合scrambler加扰器来辅助实现这一点。

提高通信的速率和带宽:

提高信号产生的频率,也就是时钟,显而易见地可以提高通信的速率。但是在能保证信号质量的前提下,单纯提高时钟频率能达到的提高通信速率的效果是非常有限的。

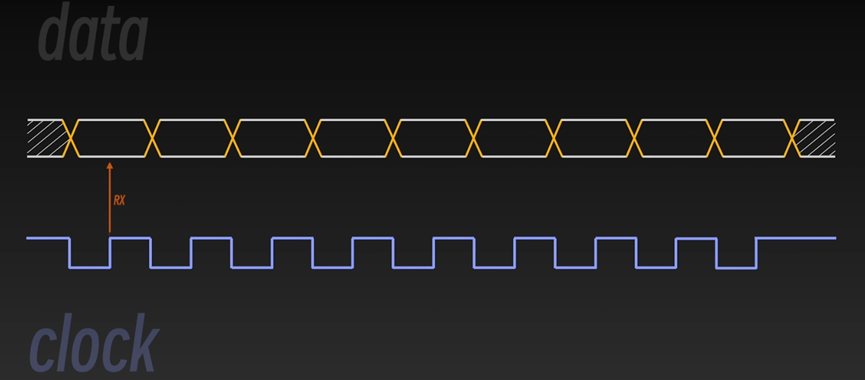

正常收发一个bit数据,需要一个时钟周期才能完成,比如说发送方在时钟下降沿切换,那么接收方就在上升沿采样。一对上下边沿构成一整个周期。

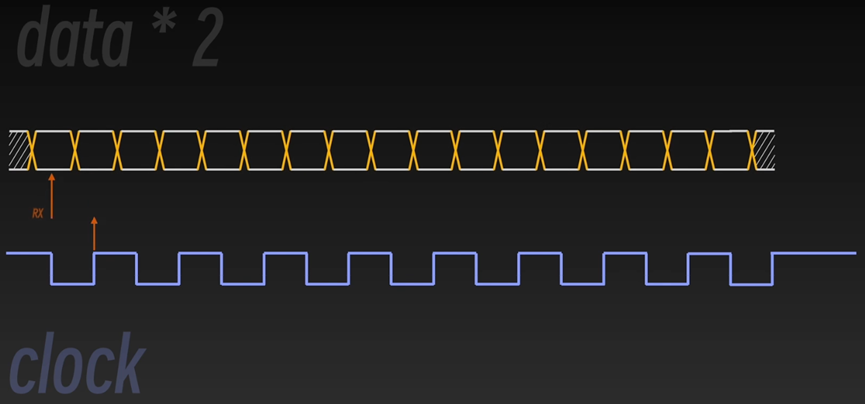

如果每个比特只用半个时钟周期,效率就可以翻倍。可以在时钟的上下边沿均做数据切换,发送到总线的时候,在两根线之间做一定的相位延迟,接收方则在延时后的每个时钟边沿进行采样。这就实现了double data rate,简称DDR

除了通过改进时钟来提高通信速率外,也可以通过改串行为并行的方式提高通信速率,比如SPI就有Dual SPI、Quad SPI、OSPI,常用来连接flash等存储设备。

但板级通信多线并行还有可能实现,比如DDR的PCB布线,通过走等长线,保证多根并线数据线的采样都有充足的建立和保持时间。在米级传输下,并行通信就很难实现了。

最后,通过信号调制技术,可以变相的提高带宽,详细可以了解PAW编码调制技术。

浙公网安备 33010602011771号

浙公网安备 33010602011771号