【FPGA基础】脉冲边沿检测技术

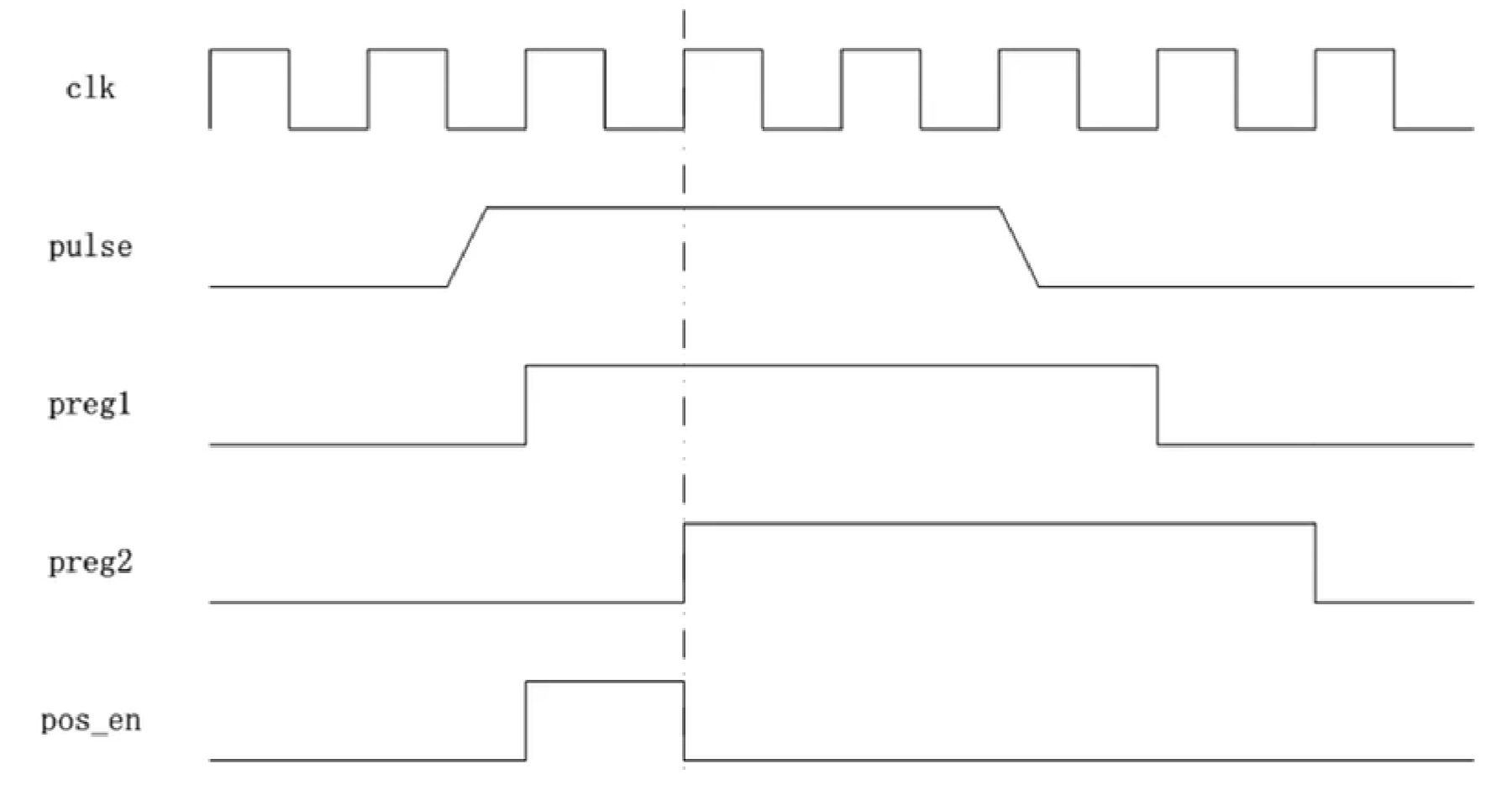

一、脉冲边沿检测原理

- 对输入脉冲信号进行两级寄存器的锁存

- 对两级寄存器进行逻辑运算,在其边沿脉冲电平变化时获取保持一个时钟周期的高电平

二、脉冲边沿检测的适用场景

- 同步或异步信号均可,使用脉冲边沿检测法对异步控制信号进行同步是非常简单实用的一种方式

- 对于异步信号的脉冲检测,采样时钟频率要高于检测信号的变化率(也就是待检测脉冲的频率),即被检测信号的低电平或高电平都应该至少保持若干个时钟周期(要遵循奈奎斯特采样定理,采样时钟至少要两倍于被采样信号的变化率)

- 尤其适合于一些异步控制信号的检测:

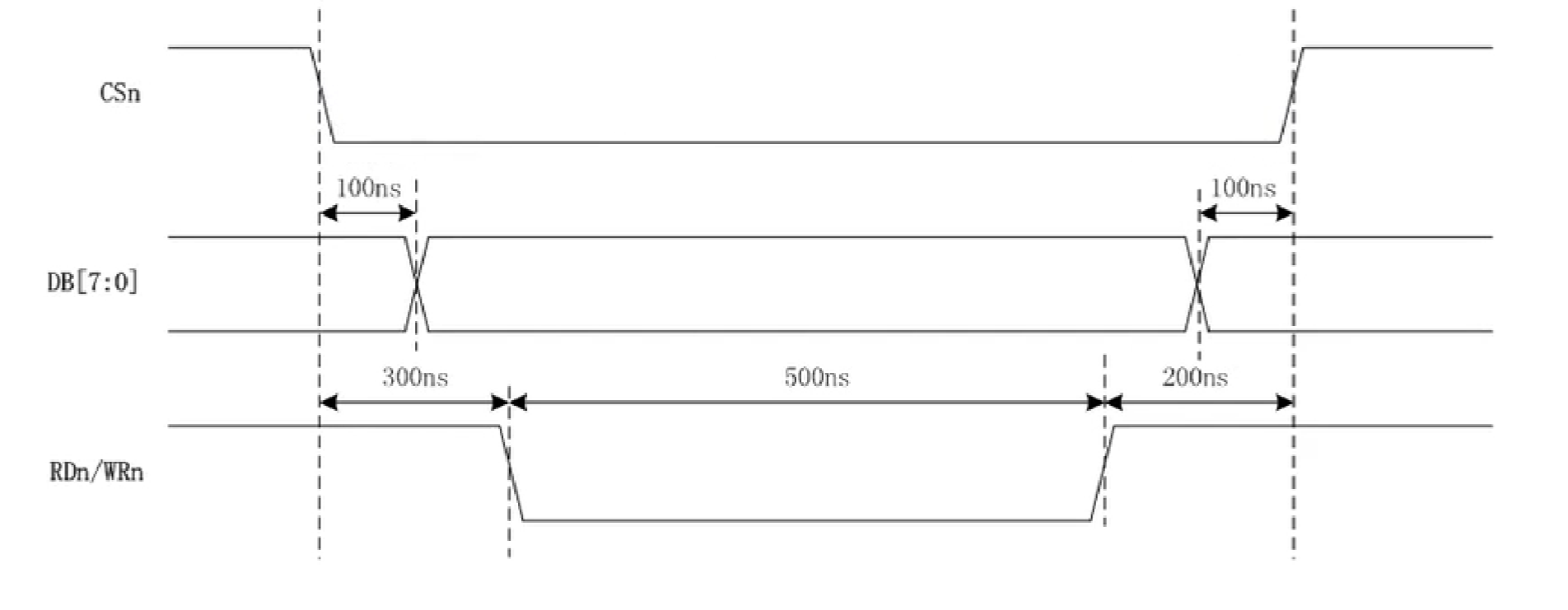

- 一些CPU的外扩异步存储接口(EMIF)的控制信号检测

- 控制或命令信号的变化检测,如中断信号的跳变检测

- 脉冲计数

- 频率计数

例:CPU的外扩异步存储接口(EMIF)的控制信号检测

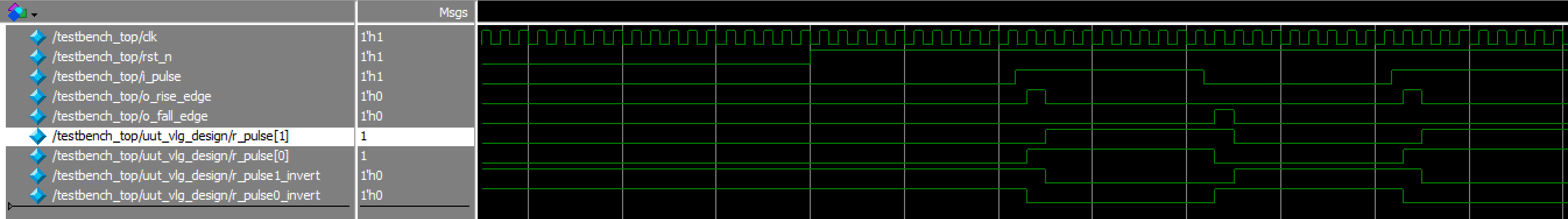

三、示例

input i_pulse; output o_rise_edge, o_fall_edge; always @(posedge i_clk) begin if (!i_rst_n) r_pulse <= 2'b0; else r_pulse <= {r_pulse[0], i_pulse}; end assign o_rise_edge = r_pulse[0] & ~r_pulse[1]; assign o_fall_edge = r_pulse[1] & ~r_pulse[0];

浙公网安备 33010602011771号

浙公网安备 33010602011771号