【FPGA基础】同步复位与异步复位

一、何时何处需要复位

参考Xilinx官方文档《UltraFast Design Methodology Guide for FPGAs and SoCs (UG949)》:

Xilinx器件具有专用的全局置位/复位信号 (global set/reset signal,GSR)。在器件配置结束时,此信号会对硬件中所有时序逻辑电路做初始化的赋值。 如果未指定初始状态,将为时序原语分配默认值。在大多数情况下,默认值为 0。FDSE 和 FDPE 原语是例外,其默认为逻辑 1。每个寄存器在配置结束时都将处于已知状态。因此无需编写仅用于在上电时初始化器件的全局复位代码。(作者补:有时也需要软复位,可以可控的复位FPGA器件内部的逻辑电路,这时通过外部定义的引脚,或者当使用zynq系列FPGA时由PS端复位,需要专门设计复位电路)

Xilinx强烈建议您谨慎判断何时设计需要复位以及何时不需要复位。大多数情况下,控制电路逻辑上可能需要复位以确保正常运行,数据电路逻辑上通常不需要复位。(作者补:因为数据信号的有效与否通常是由控制信号,比如使能信号或有效信号,来决定的)

复位的使用限制如下:

- 限制复位信号线的总体扇出。

- 减少复位布线所需的互连数量。

- 简化复位路径的时序。

- 在大多数情况下,这样即可整体改进性能、面积和功耗。

二、同步复位与异步复位

参考Xilinx官方文档《UltraFast Design Methodology Guide for FPGAs and SoCs (UG949)》:

如需复位,Xilinx建议使用同步复位。同步复位相比于异步复位具有如下优势:

- 在Xilinx的器件结构中,同步复位可以直接映射至器件架构中的更多资源元件。

- 异步复位会影响通用逻辑结构的性能。由于所有Xilinx器件的通用寄存器均可将置位/复位编程为异步或同步,可能看似使用异步复位不会受到任何惩罚。使用全局异步复位虽然并不会增加控制集,但由于需要将此复位信号布局到所有寄存器元件,因此会增加布线复杂性。

- 需要更高密度或者微调布局时,同步复位会为控制集重新映射提供更多的灵活性。如果在布局更优化的 slice 中发现不兼容的复位,那么可将同步复位重新映射到寄存器的数据路径。这样即可根据需要减少布线资源利用率并增加布局密度,从而实现正确的适配并改进性能。

- 异步复位可能需要多周期断言(multi-cycle assertion),以确保电路正确复位并稳定。同步复位没有这个要求。

- 复位断言有效期间,异步复位导致 block RAM、LUTRAM、以及 SRLs的存储器内容损坏的可能性更高。

- 对于含异步复 位(用于驱动 block RAM、LUTRAM 和 SRL 的输入管脚)的寄存器尤其如此。DSP48 和 block RAM 等部分资源仅包含同步复位以供块内的寄存器元件使用。在与这些元件关联的寄存器元件上使用 异步复位时,可能无法在不影响功能的前提下直接将这些寄存器推断到这些块中。

//同步复位,敏感变量表中只有clk always @ (posedge clk) begin if(rst) ...... else ...... end //异步复位,敏感变量表中除有clk外,还有复位信号 always @ (posedge clk or posedge rst) begin if(rst) ...... else ...... end

三、异步复位的同步处理

“异步”的复位信号一般不建议作为FPGA逻辑的全局异步复位信号使用。(1)异步复位的“异步”很可能导致各个逻辑的复位“异步”,引起设计问题;(2)异步复位可能占用更多的FPGA布局布线资源,难以满足时序性能要求。

若设计中一定要做异步复位,那么推荐对异步复位信号先做“同步处理”,再做异步复位信号使用。

//对复位信号做同步处理,产生新的异步复位信号 //input i_rst_n; reg r_rst_n; always @ (posedge i_clk) r_rst_n <= i_rst_n;

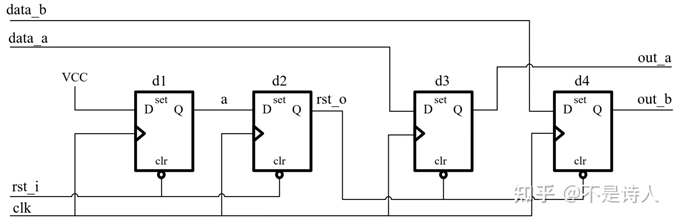

四、异步复位同步撤离(异步复位同步释放)

用verilog描述如下:

always @(posedge clk or negedge arst_n) begin

if (!arst_n) {rst_n, rff1} <= 2'b0;

else {rst_n, rff1} <= {rff1, 1'b1};

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

……

else ……

end

推荐设计中使用这种复位设计,结合了双方面的优点,很好的克服了异步复位的缺点,因为异步复位的问题主要出现在复位信号释放的时候。倘若异步复位信号有效的话,触发器就会复位,从而复位后级寄存器;但是又因为这属于时钟沿触发,当复位信号释放时,触发器的输出要延迟一个时钟周期才能恢复成1,因此使得复位信号的释放与时钟沿同步化。

这种复位方式,既可以防止后级寄存器无法满足恢复时间要求,也可以避免前级寄存器无法满足恢复时间要求,还能捕捉持续时间小于一个时钟周期的复位信号。但要注意的是,虽然复位不依赖输出,但是复位输出信号需要依赖于时钟才能撤离,即在上电复位或者门控时钟电路里,当电路中没有正常工作的时钟时,该复位电路无法工作。

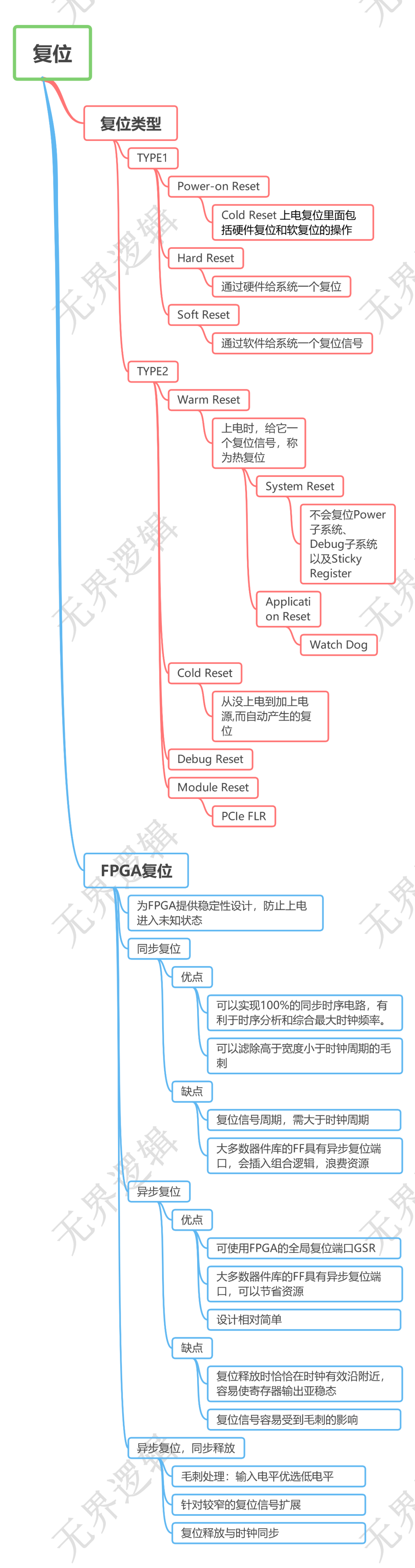

五、复位概念梳理(转自公众号“无界逻辑”)

浙公网安备 33010602011771号

浙公网安备 33010602011771号