【FPGA基础】门控时钟与使能时钟

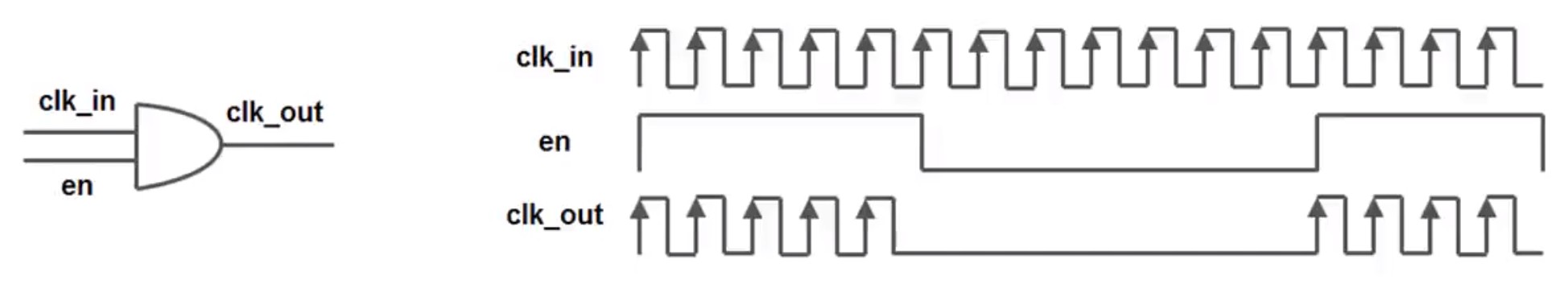

1、门控时钟

- 门控时钟通过一个使能信号控制时钟的开关

- 组合逻辑中多用门控时钟

- 包含一个门电路,容易因竞争而产生不希望的毛刺

- 当系统不工作时可以关闭时钟,降低系统功耗

- 使用门控时钟并不符合同步设计的思想,它可能会影响设计的实验和验证

- /////////////////////////////////////////////////////////////////////////

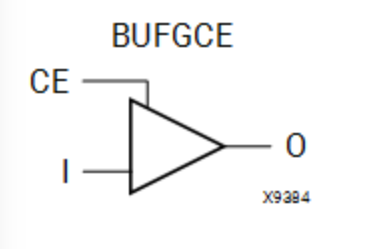

- 与全局时钟资源相关的两条原语:BUFGCE和BUFGMUX

-

![]()

- BUFGCE是带有时钟使能端的全局缓冲。它有一个输入I、一个使能端CE和一个输出端O。只有当BUFGCE的使能端CE有效(高电平)时,BUFGCE才有输出,相当于门控时钟。 (带有时钟使能端的BUFG)

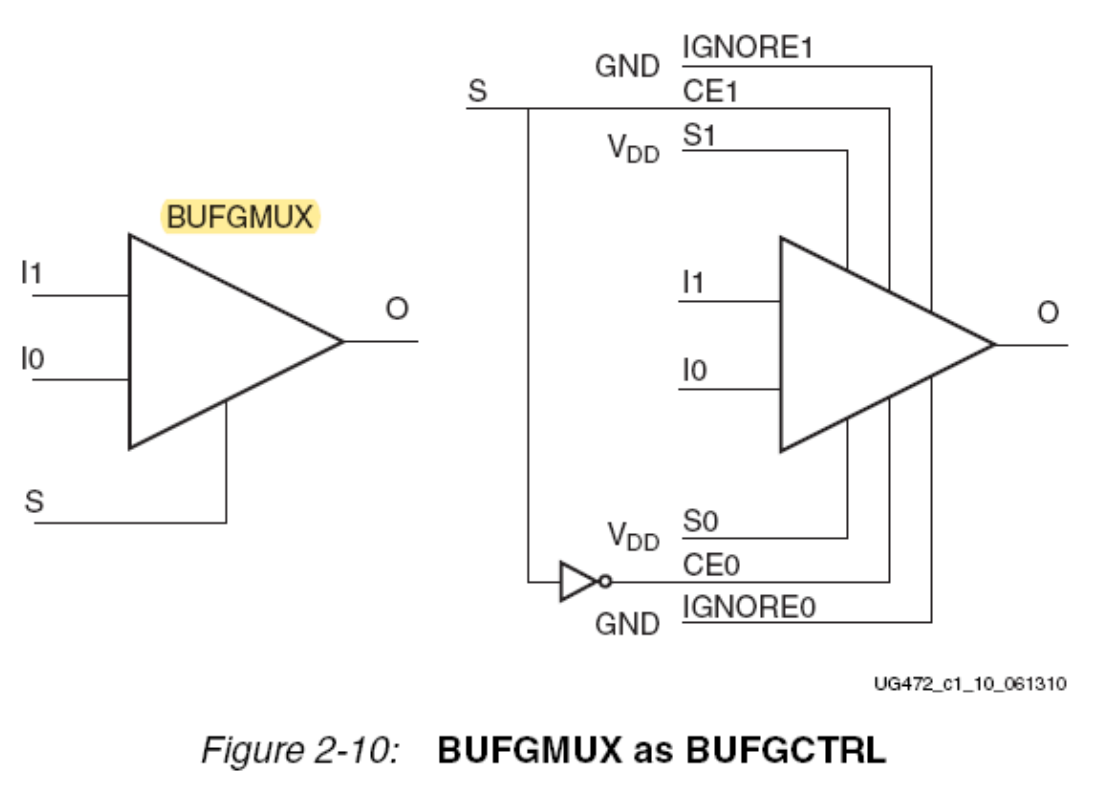

- BUFGMUX是全局时钟选择缓冲,它有I0和I1两个输入,一个控制端S,一个输出端O。当S为低电平时输出时钟为I0,反之为I1。需要指出的是BUFGMUX的应用十分灵活,I0和I1两个输入时钟甚至可以为异步关系。当I0和I1是异步关系时,例化BUFGMUX的时候需要加上"异步"的属性:

BUFGMUX #( .CLK_SEL_TYPE("ASYNC") ) BUFGMUX_inst ( .O(O), // 1-bit output: Clock output .I0(I0), // 1-bit input: Clock input (S=0) .I1(I1), // 1-bit input: Clock input (S=1) .S(S) // 1-bit input: Clock select );

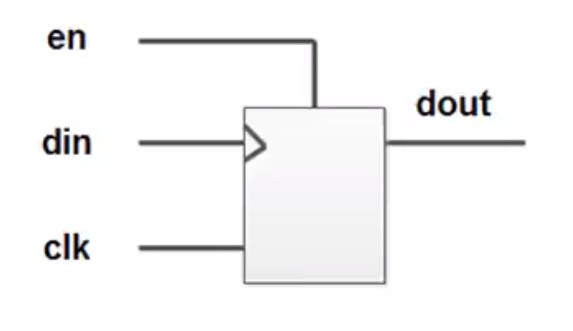

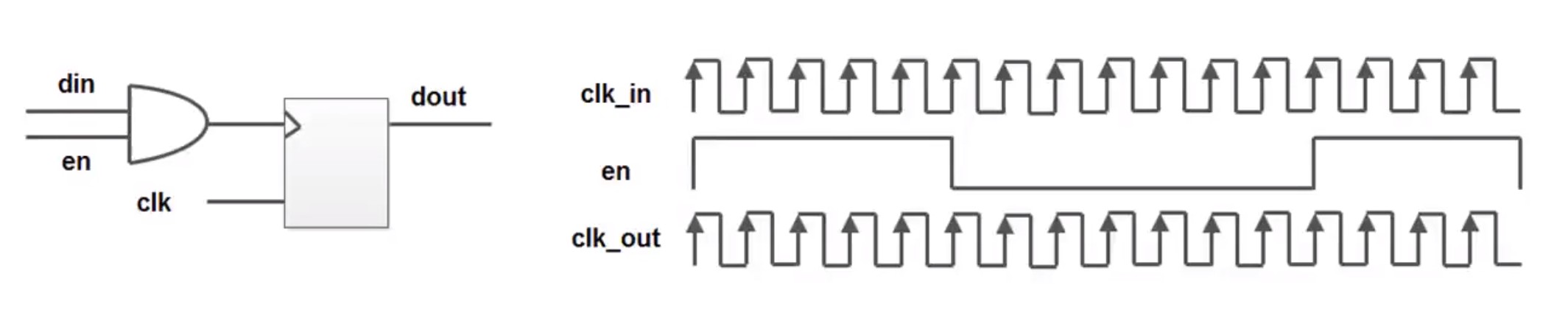

2、使能时钟

- 时钟始终保持开启工作状态,使能时钟是在每个时钟周期都判断使能信号以确定是否进行逻辑处理

- 使能时钟不能像门控时间一样降低系统功耗

- 使能时钟使用同步设计思想,便于设计实现与验证

相比之下,门控时钟是对时钟本身“是否存在”加以限制,而使能时钟是通过使能信号对时钟的某些时刻“是否有效”进行限制。

3、用使能时钟代替分频时钟

- FPGA内部时钟使用逻辑计数分频产生的时钟,一般不推荐直用于FPGA内部逻辑的时钟

- 若不希望使用PLL资源,或者无法产生过慢的时钟,那么可以考虑使用使能时钟的方式产生“分频时钟”

- 分频时钟改用使能时钟的好处:

- 避免时钟不稳定

- 保持一个时钟,减少跨时钟域

- 时序设计可以使用“多周期约束“

SoC中的门控时钟可参考:https://zhuanlan.zhihu.com/p/139363948

浙公网安备 33010602011771号

浙公网安备 33010602011771号