【IP】在线调试(ILA/VIO/*mark_debug*)

Xilinx FPGA在Vivado中有多种在线调试方法:

1、调用IP

(1)ILA IP核

ILA核的一个应用技巧:

当系统钟为50M或100M等高速时钟时,对于慢速信号,比如2.4k时钟下的信号,ila核需要设置非常大的采样深度才能抓到该信号,这样会非常浪费BRAM资源。这时可以通过二次编译来添加触发条件,从而抓取到慢速信号。

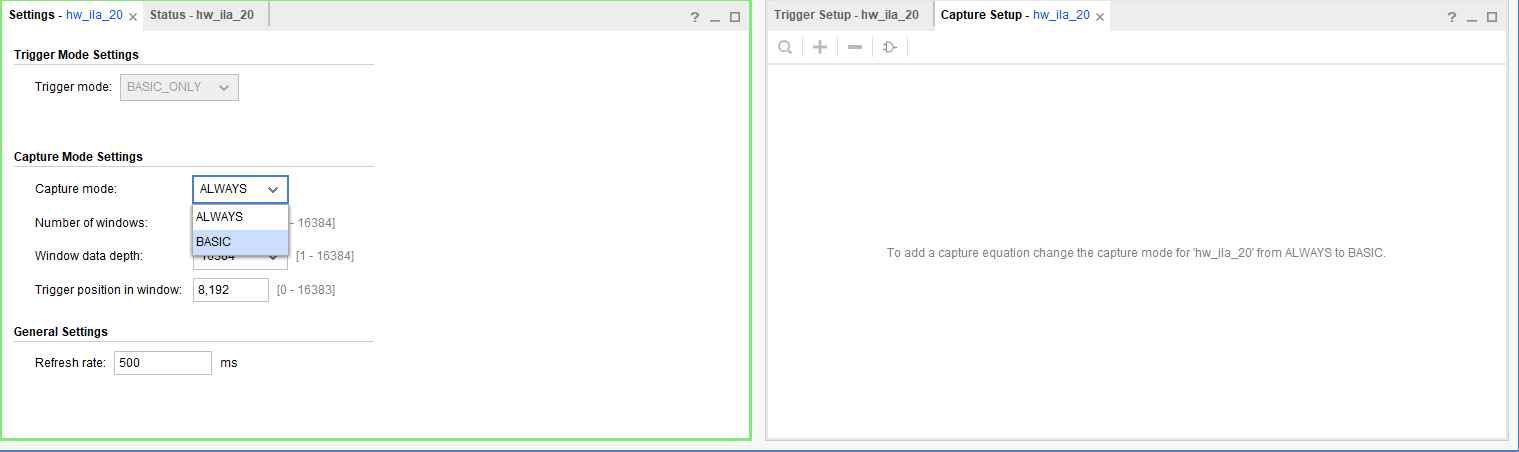

在配置ILA核时,在General Options-Trigger and Storage Settings中勾选Capture Control,将程序下载进板子里后,再在ILA核的Settings界面把Capture Mode改为Basic,就可以在右侧的Capture Setup中添加二次触发的条件了。

ILA核还可以实现FPGA启动的时候触发,以及Advanced Trigger的使用,详见如下帖子:

FPGA启动的时候触发和Vivado ILA Advanced Trigger的使用_vivado ila 触发条件-CSDN博客

(2)VIO IP核

VIO的输出可以控制测试模块的输入,VIO的输入可以显示模块的输出值。非常常用。

2、添加调试信号*mark_debug*

更详细的内容可以查看这篇文章:Vivado 逻辑分析仪使用教程-腾讯云开发者社区-腾讯云 (tencent.com)

(1)在Verilog HDL文件中直接添加,特点是防止信号被优化,最大可能保留信号原本的名称。

在input/output前或在声明变量前添加(* mark_debug = “true” *)

(* mark_debug = "true" *) wire done; (* mark_debug = "true" *) reg cnt;

(2)标记Debug mark方法,可以在原理图(block design)或在综合后的网表(Netlist)中添加。

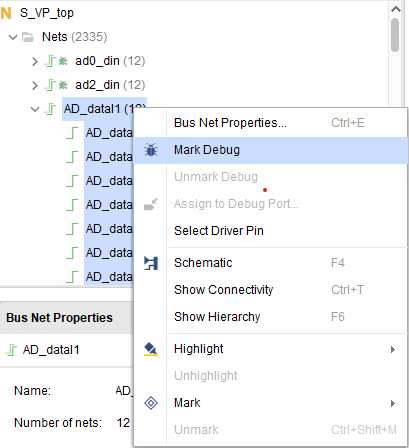

A、在原理图(block design)右击添加“Mark Debug”,工程综合后,在SYNTHESIS > Open Synthesized Design,在Netlist窗口中选择需要调试的网络节点,进行调试。

或者右键单击任意网络节点,点击Mark Debug,该网络节点会出现小甲虫标记。

对于已经选中Mark Debug的网络节点,也可以取消调试。右键单击该网络节点,选择Unmark Debug即可。

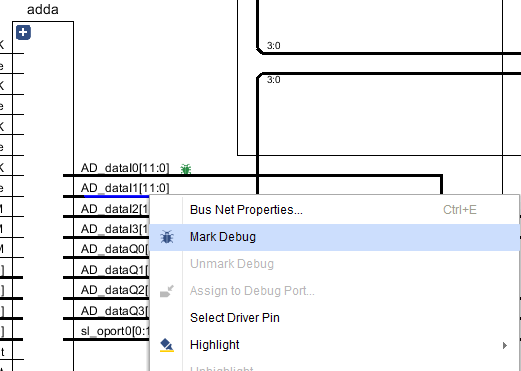

B、在综合后,Flow Navigator > SYNTHESIS > Open Synthesized Design > Schematic下打开的原理图(Schematic)中通过右键单击选中线路,添加Mark Debug信号,和Unmark Debug信号

点击 Windows > Debug,即可出现Debug窗口,在这里可以观察到已经mark debug的信号。

(3)使用Tcl命令,直接修改*.xdc文件,和添加ILA( Integrated Logic Analyzer) IP核完成。

set_property MARK_DEBUG true [get_nets [list {control_reg[0]} {control_reg[1]} \ {control_reg[2]} {control_reg[3]} {control_reg[4]} {control_reg[5]} \ {control_reg[6]} {control_reg[7]} {control_reg[8]} {control_reg[9]} \ {control_reg[10]} {control_reg[11]} {control_reg[12]} {control_reg[13]} \ {control_reg[14]} {control_reg[15]} {control_reg[16]} {control_reg[17]} \ {control_reg[18]} {control_reg[19]} {control_reg[20]} {control_reg[21]} \ {control_reg[22]} {control_reg[23]} {control_reg[24]} {control_reg[25]} \ {control_reg[26]} {control_reg[27]} {control_reg[28]} {control_reg[29]} \ {control_reg[30]} {control_reg[31]}]] create_debug_core u_ila_0 ila set_property port_width 1 [get_debug_ports u_ila_0/CLK] connect_debug_port u_ila_0/CLK [get_nets [list wbClk ]] set_property port_width 32 [get_debug_ports u_ila_0/PROBE0] connect_debug_port u_ila_0/PROBE0 [get_nets [list {control_reg[0]} {control_reg[1]} {control_reg[2]} {control_reg[3]} {control_reg[4]} \ {control_reg[5]} {control_reg[6]} {control_reg[7]} {control_reg[8]} \ {control_reg[9]} {control_reg[10]} {control_reg[11]} {control_reg[12]} \ {control_reg[13]} {control_reg[14]} {control_reg[15]} {control_reg[16]} \ {control_reg[17]} {control_reg[18]} {control_reg[19]} {control_reg[20]} \ {control_reg[21]} {control_reg[22]} {control_reg[23]} {control_reg[24]} \ {control_reg[25]} {control_reg[26]} {control_reg[27]} {control_reg[28]} \ {control_reg[29]} {control_reg[30]} {control_reg[31]} ]]

浙公网安备 33010602011771号

浙公网安备 33010602011771号