摘要:

eFlash控制器的RTL gvim 操作 gg -- 跳到首页 GG -- 按住shift,跳到尾部 ctrl+V --> 上下键选择行 --> shift+i -->输入 -->esc退出 -- 实现列操作 u -- 撤销操作 . -- 重复上一次操作 v/flash/d -- 删除有flash 阅读全文

摘要:

# 1. 奇分频 实现将一个系统时钟进行 5 分频的奇数分频的功能。可以用于将高频的时钟降低为低频的时钟工作使用。 ## 1.1 框图及波形 上升沿或者是下降沿作用下,将信号 阅读全文

摘要:

1.Latch简介 Latch就是锁存器,是一种在异步电路系统中,对输入信号电平敏感的单元,用来存储信息 锁存器在数据未锁存时,输出端的信号随输入信号变化,就像信号通过一个缓冲器,一旦锁存信号有效,数据就会被锁存,输入信号不起作用,因此,锁存器也被称为透明锁存器,指的是不锁存时输出对于输入是透明的 阅读全文

摘要:

1.层次化设计 数字电路中根据模块层次不同有两种基本的结构设计方法:自底向上的设计方法和自顶向下的设计方法 1.1 自底向上的设计方法(Bottom-Up) 自底向上的设计是一种传统的设计方法,对设计进行逐次划分的过程是从存在的基本单元出发的(基本单元是已有的或者是购买的),有基本单元构建高层单元, 阅读全文

摘要:

1.半加器 加法器是数字电路中经常用到的一种基本器件,主要用于两个数或者是多个数相加,加法器又分为半加器(half adder)和全加器(full adder) 半加器电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。是实现两个一位二进制数的加法运算电路。 全加器是在半加 阅读全文

摘要:

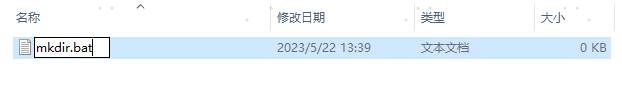

# **快速创建文件夹的技巧** 1.首先创建文本文档将扩展名更改为**.bt**,**mkdir.bat**  ! 阅读全文