05 2023 档案

摘要:1.SD协议版本 SD 1.1 SD 2.0 SD 3.0 在看协议的时候,需要注意协议的版本,注意版本之间的差别 SD协议是常见的数据通信和存储卡之间的协议 HDMI是显示相关的协议,遵循HDMI协议 USB遵循USB协议,USB3.0协议的复杂度高于USB2.0 主要学习的是协议的分析方法 2.

阅读全文

摘要:# eFlash控制器Debug

阅读全文

摘要:# eFlash控制器的基本功能仿真

阅读全文

摘要:eFlash控制器的RTL gvim 操作 gg -- 跳到首页 GG -- 按住shift,跳到尾部 ctrl+V --> 上下键选择行 --> shift+i -->输入 -->esc退出 -- 实现列操作 u -- 撤销操作 . -- 重复上一次操作 v/flash/d -- 删除有flash

阅读全文

摘要:# 1. 奇分频 实现将一个系统时钟进行 5 分频的奇数分频的功能。可以用于将高频的时钟降低为低频的时钟工作使用。 ## 1.1 框图及波形 上升沿或者是下降沿作用下,将信号

阅读全文

摘要:1.Latch简介 Latch就是锁存器,是一种在异步电路系统中,对输入信号电平敏感的单元,用来存储信息 锁存器在数据未锁存时,输出端的信号随输入信号变化,就像信号通过一个缓冲器,一旦锁存信号有效,数据就会被锁存,输入信号不起作用,因此,锁存器也被称为透明锁存器,指的是不锁存时输出对于输入是透明的

阅读全文

摘要:1.层次化设计 数字电路中根据模块层次不同有两种基本的结构设计方法:自底向上的设计方法和自顶向下的设计方法 1.1 自底向上的设计方法(Bottom-Up) 自底向上的设计是一种传统的设计方法,对设计进行逐次划分的过程是从存在的基本单元出发的(基本单元是已有的或者是购买的),有基本单元构建高层单元,

阅读全文

摘要:1.半加器 加法器是数字电路中经常用到的一种基本器件,主要用于两个数或者是多个数相加,加法器又分为半加器(half adder)和全加器(full adder) 半加器电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。是实现两个一位二进制数的加法运算电路。 全加器是在半加

阅读全文

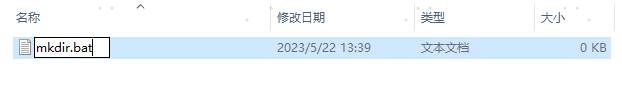

摘要:# **快速创建文件夹的技巧** 1.首先创建文本文档将扩展名更改为**.bt**,**mkdir.bat**  !

阅读全文

摘要:1.译码器 译码器是编码的逆过程,在编码时,每一种二进制代码都赋予了特定的含义,即都代表了一个确定的信号或者是对象;把代码状态的特定含义翻译出来的过程叫做译码,实现译码操作的电路称为译码器,或者说,译码器可以将输入二机制代码的状态翻译成输出信号,以表示其原来含义的电路 译码器(decoder)是一类

阅读全文

摘要:1.多路选择器 组合逻辑是Verilog设计中的一个重要组成部分,从电路本质上讲,组合逻辑电路的特点是输出信号只是当前时刻输入信号的函数,与其他时刻的输入状态无关,无存储电路,也没有反馈电路 组合逻辑电路输出信号的电平变化仅仅与输入信号的电平变化有关,不涉及信号跳变沿的处理 多路选择器,是数据选择器

阅读全文

摘要:1.FPGA设计流程 1.设计规划 对项目需求了解,划分子功能模块,子功能模块的输入输出信号及通信关系 2.波形绘制 了解子模块的功能,画出框图,搞清楚如何通过输入信号得到输出信号,进而绘制波形图 3.代码编写 参照绘制的波形图 4.代码编译 检查代码中的语法错误 5.逻辑仿真 编写仿真代码,对ve

阅读全文

摘要:# 1.开发环境搭建 需要使用的软件: * QuartusII * ModelSim * Visio * Notepad++ # 2.初识Verilog ## 2.1 Verilog HDL简介 * Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表

阅读全文

摘要:1.module module有出入接口,输出接口 module有时钟和复位 // input clock; rest_n; // n表示低电平复位 //output o_data; module module_a( // module是关键字表示声明一个模块 // module module名 /

阅读全文

摘要:1.枚举类型 1.枚举数据类型是C语言中一种构造数据类型,可以让数据更加简洁,更易读,对于只有几个特定的数据,可以使用枚举类型 2.枚举对应英文enumeration,简写为enum 3.枚举是一组常量的集合,包含一组有限的特定的数据 4.枚举语法的定义格式为 enum 枚举名 {枚举元素} 1.1

阅读全文

摘要:输入输出 1.字符输出函数 c语言中没有I/O语句,I/O操作由函数实现 #include <stdio.h 1.1 字符输出函数 - putchar 格式:putchar(c) 参数:c为字符常量\变量\表达式 功能:把字符c输出到显示器上 返回值:正常,为显示的代码值ASCII码 #includ

阅读全文

摘要:1.运算符 1.1 算术运算符 + - * / ++ -- % -- 取余 # include <stdio.h> int main() { int a = 15,b = 8,c; c = a + b; printf("c = %d\n",c); c = a - b; printf("c = %d\

阅读全文

摘要:1.数据类型 1.1 数据类型分类 构造类型--用户自定义的数据类型 存储负数使用有符号数 字符型也分为有符号数和无符号数 #include <stdio.h> int main() { } 1.2基本数据类型 bool类型 bool不是基本数据类型,使用的时候需要加入头文件 #include <s

阅读全文

摘要:1 Linux开发环境搭建 1.1 虚拟机安装 1、安装VM Ware 2、安装ubuntu 分区 -- Linux没有盘符的概念 / -- 5000M /boot -- 系统启动过程中读取的重要文件 /swap -- 2000M,虚拟内存是物理内存的两倍左右 /home -- 常见的分区 Linu

阅读全文

浙公网安备 33010602011771号

浙公网安备 33010602011771号